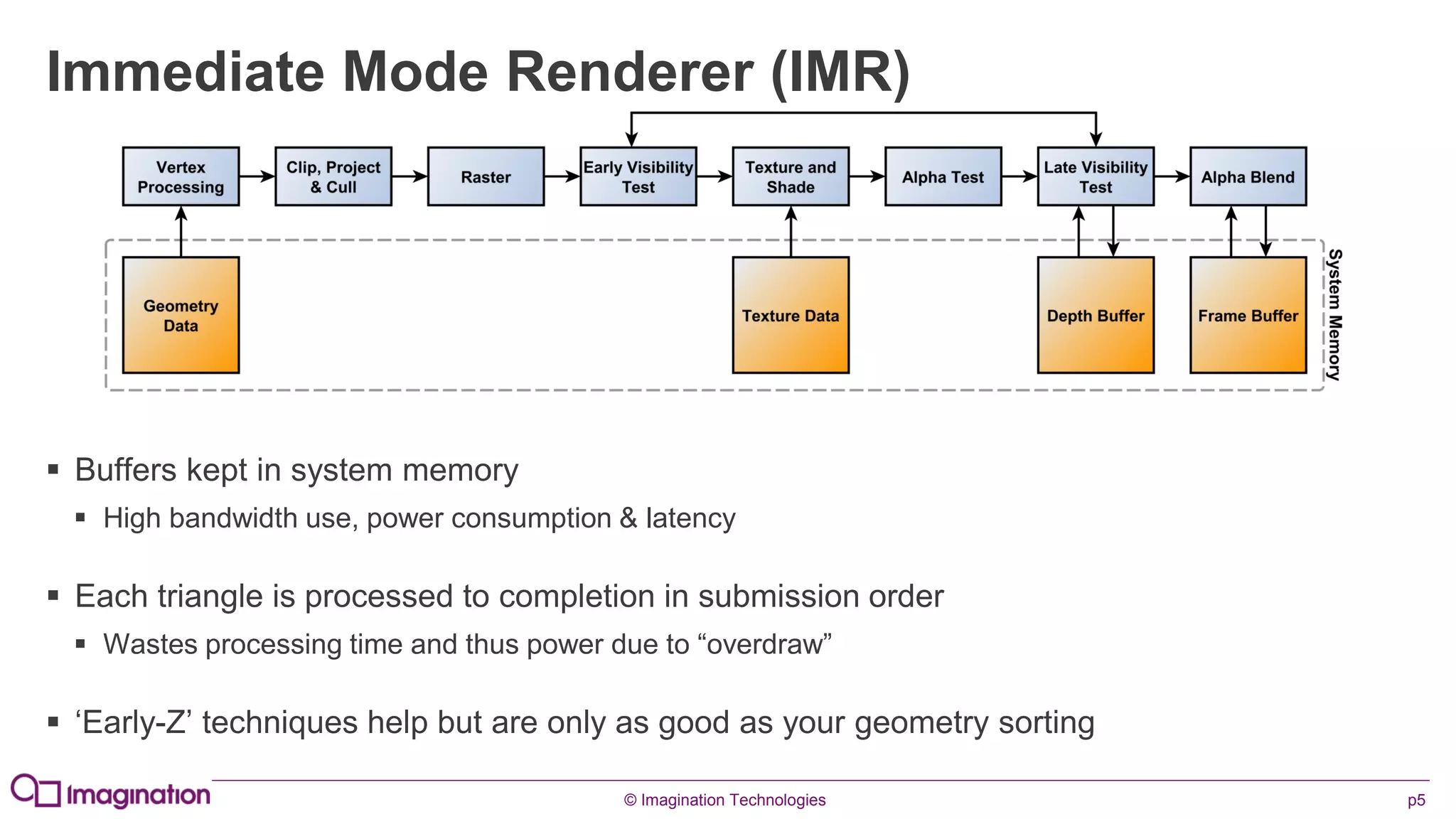

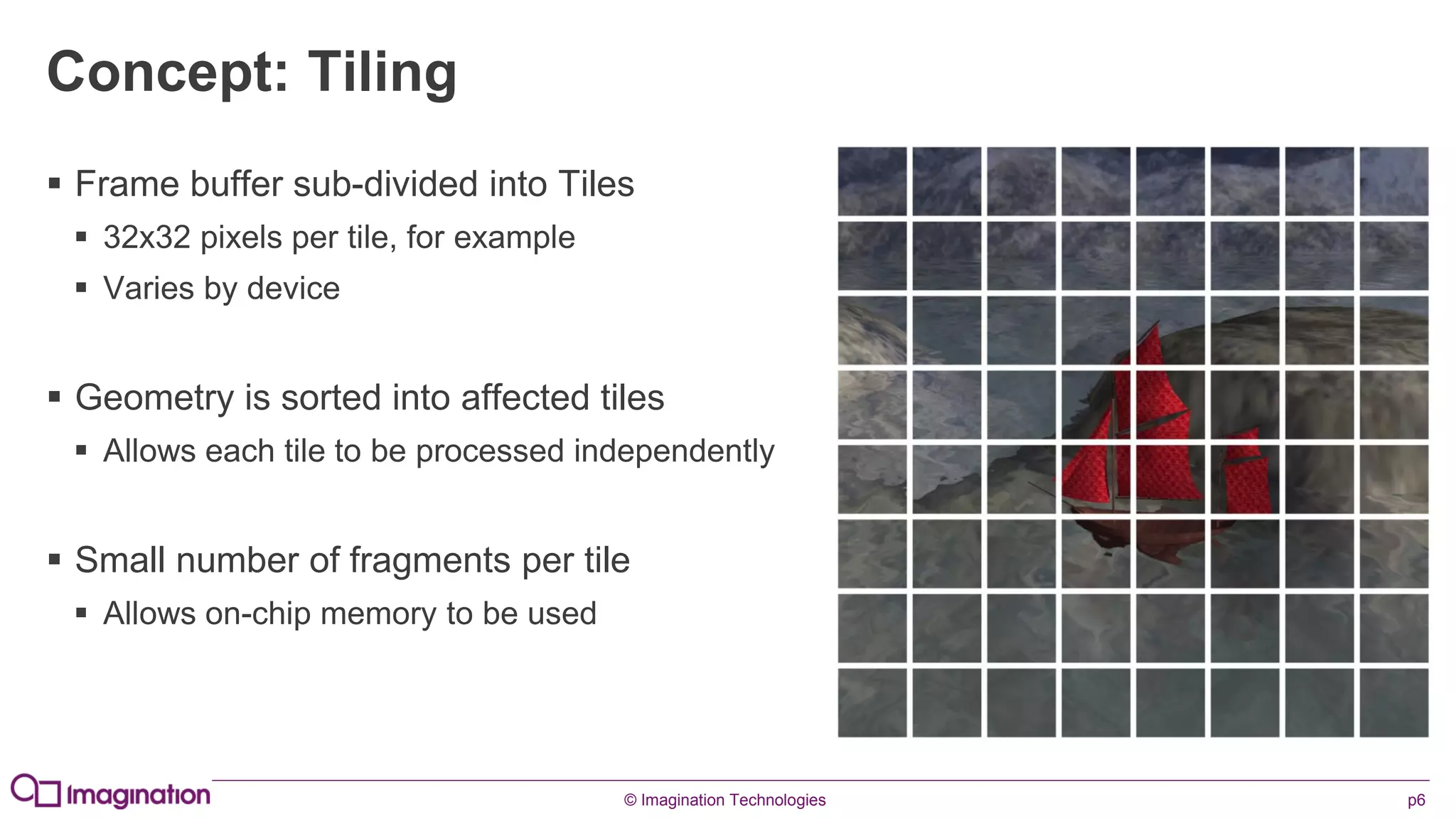

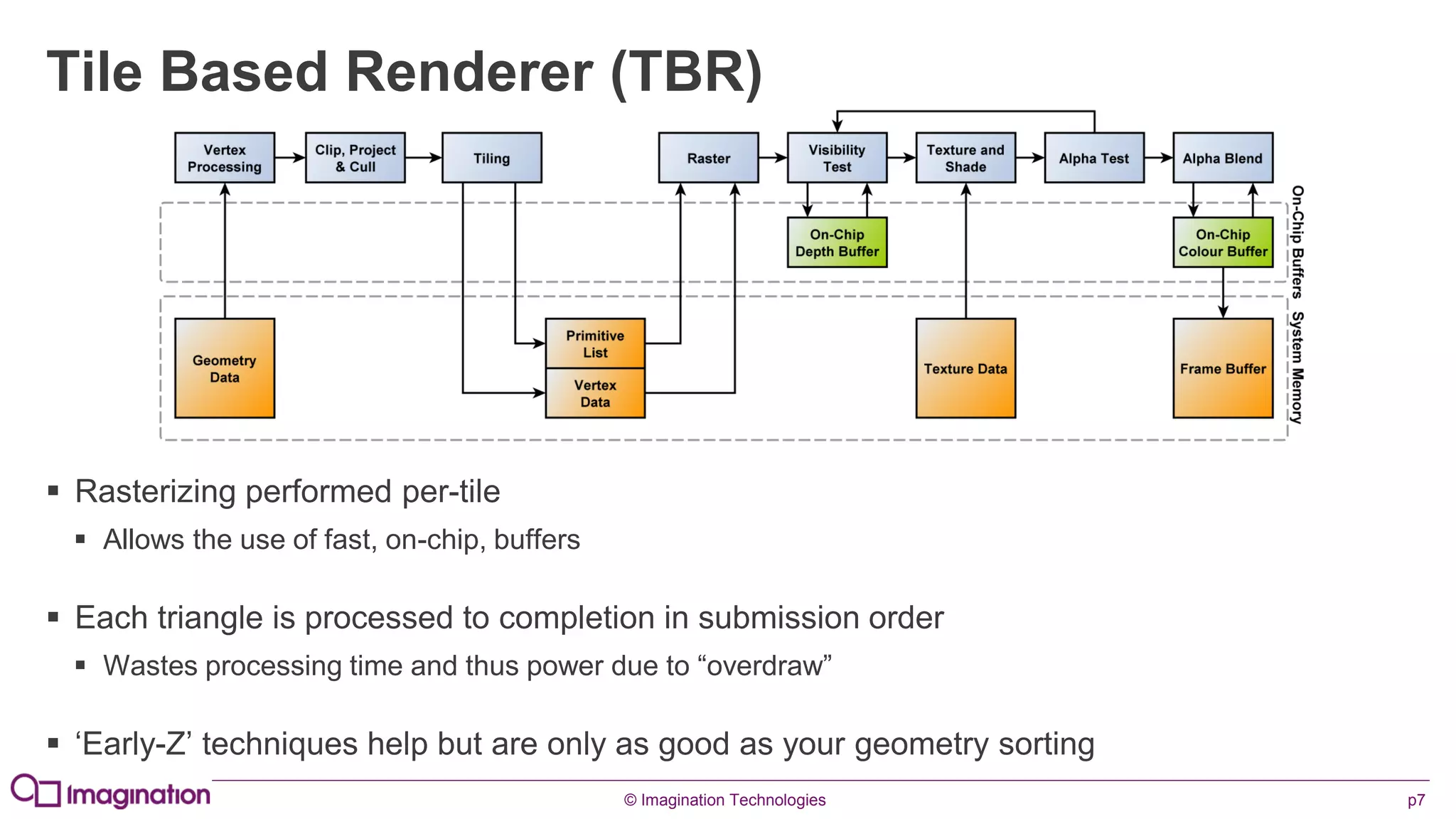

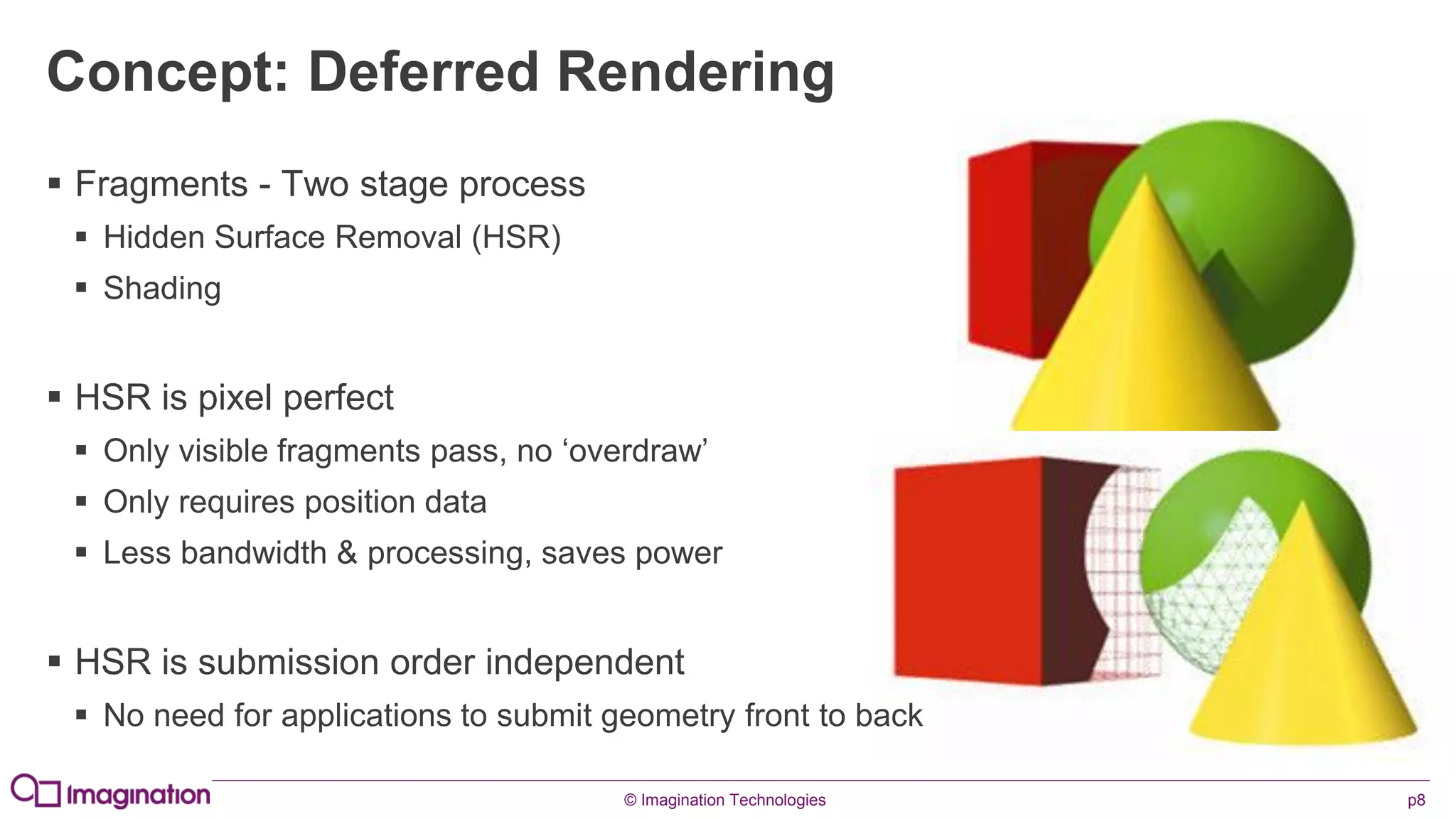

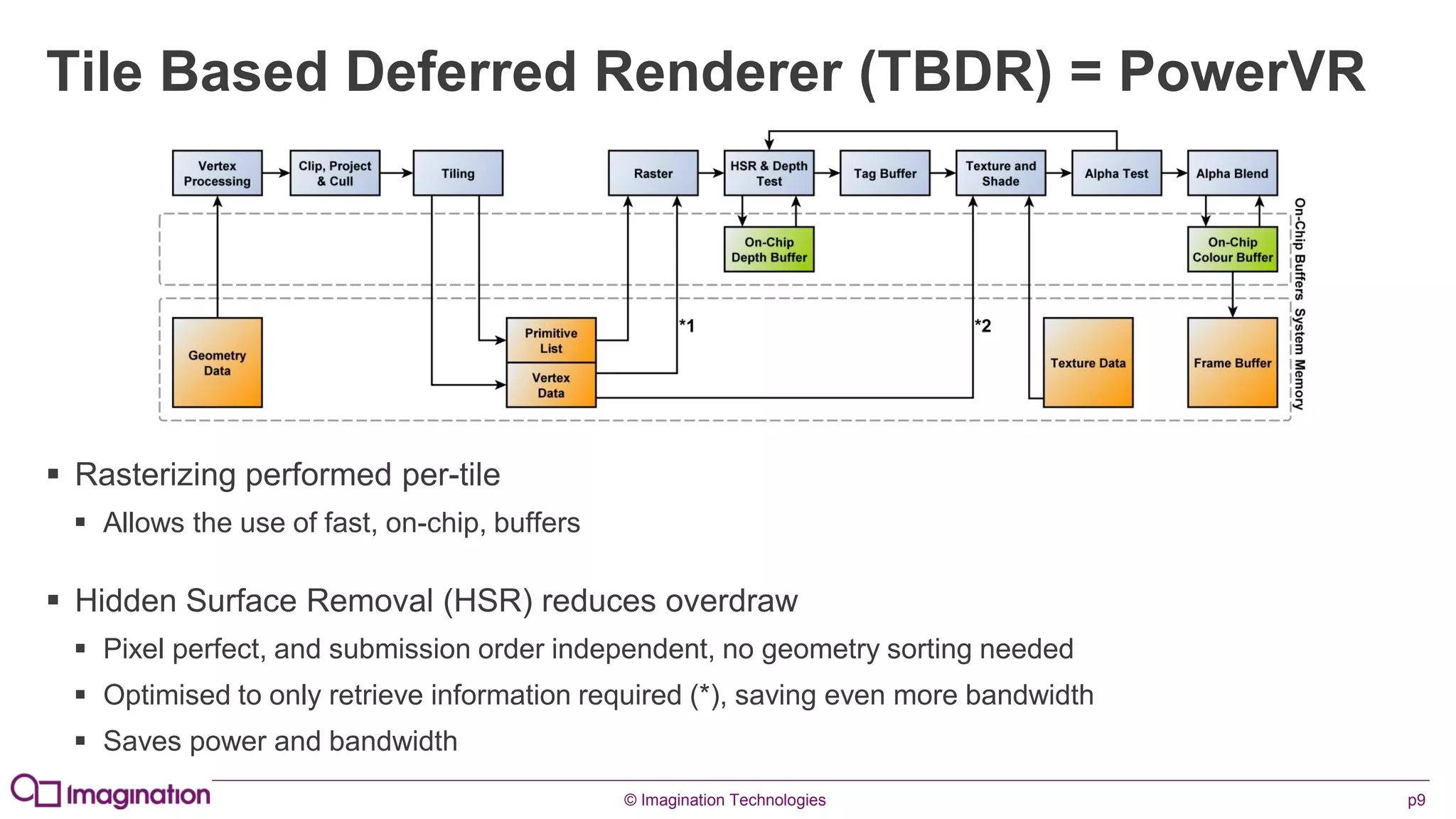

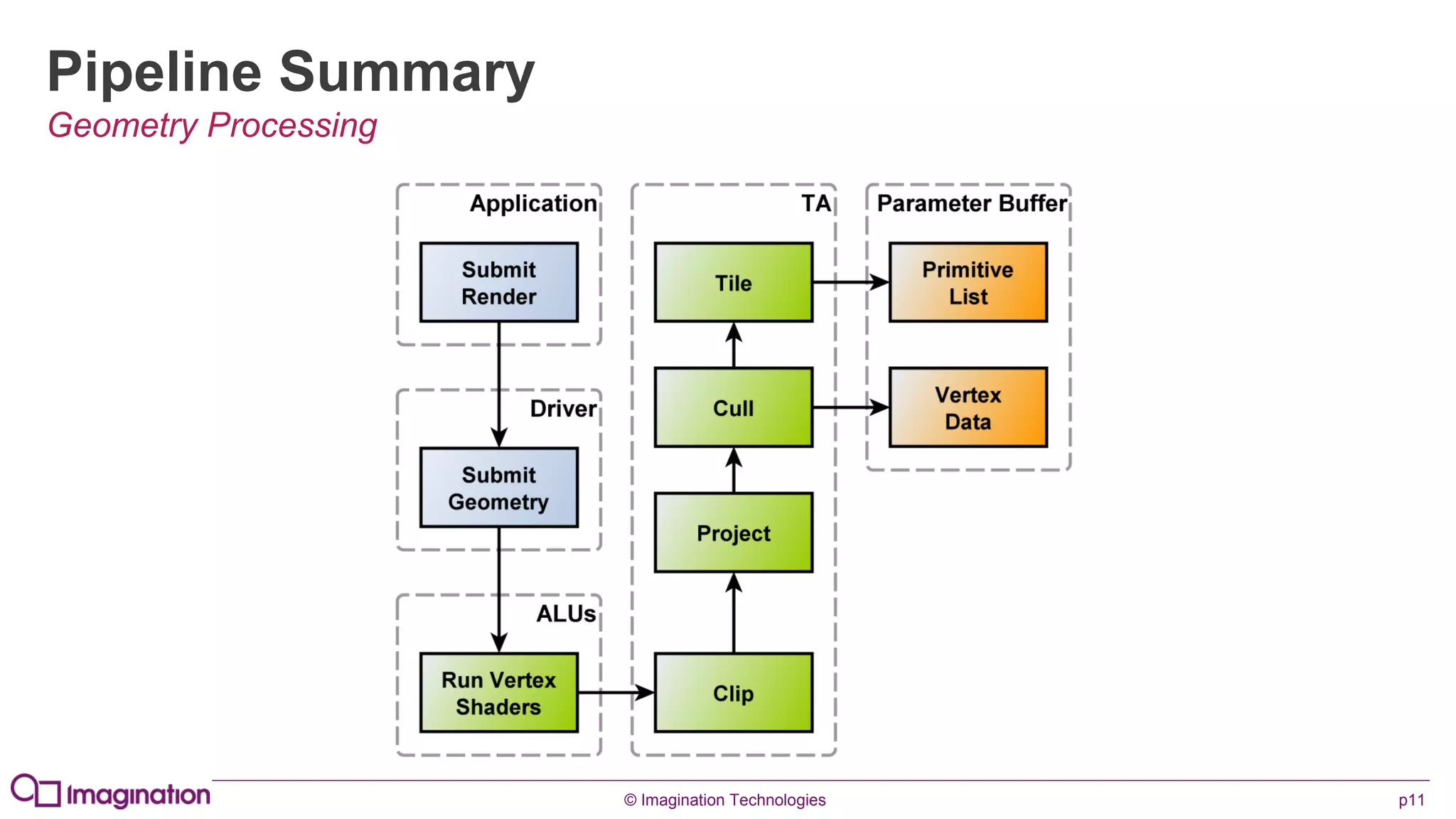

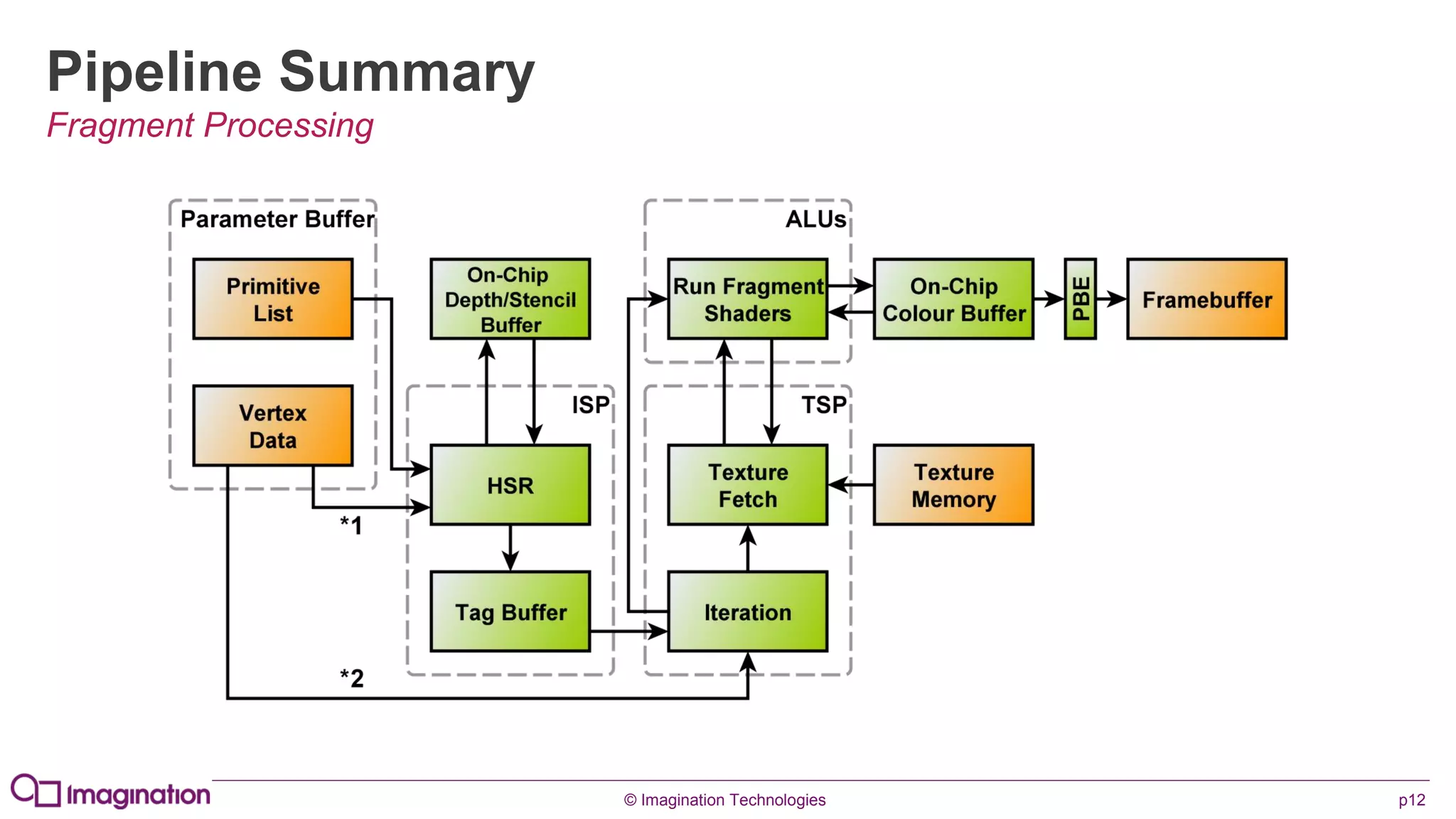

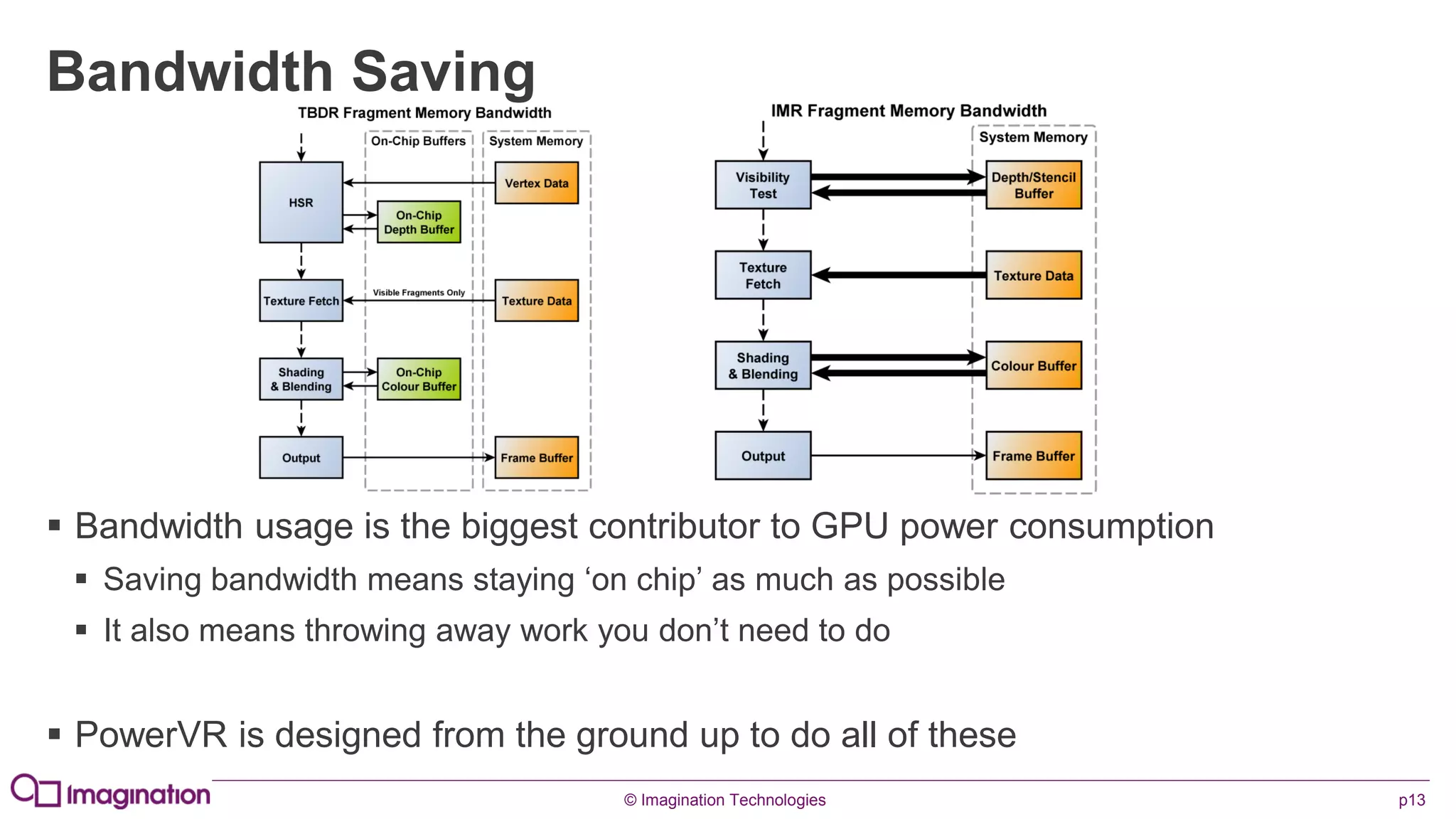

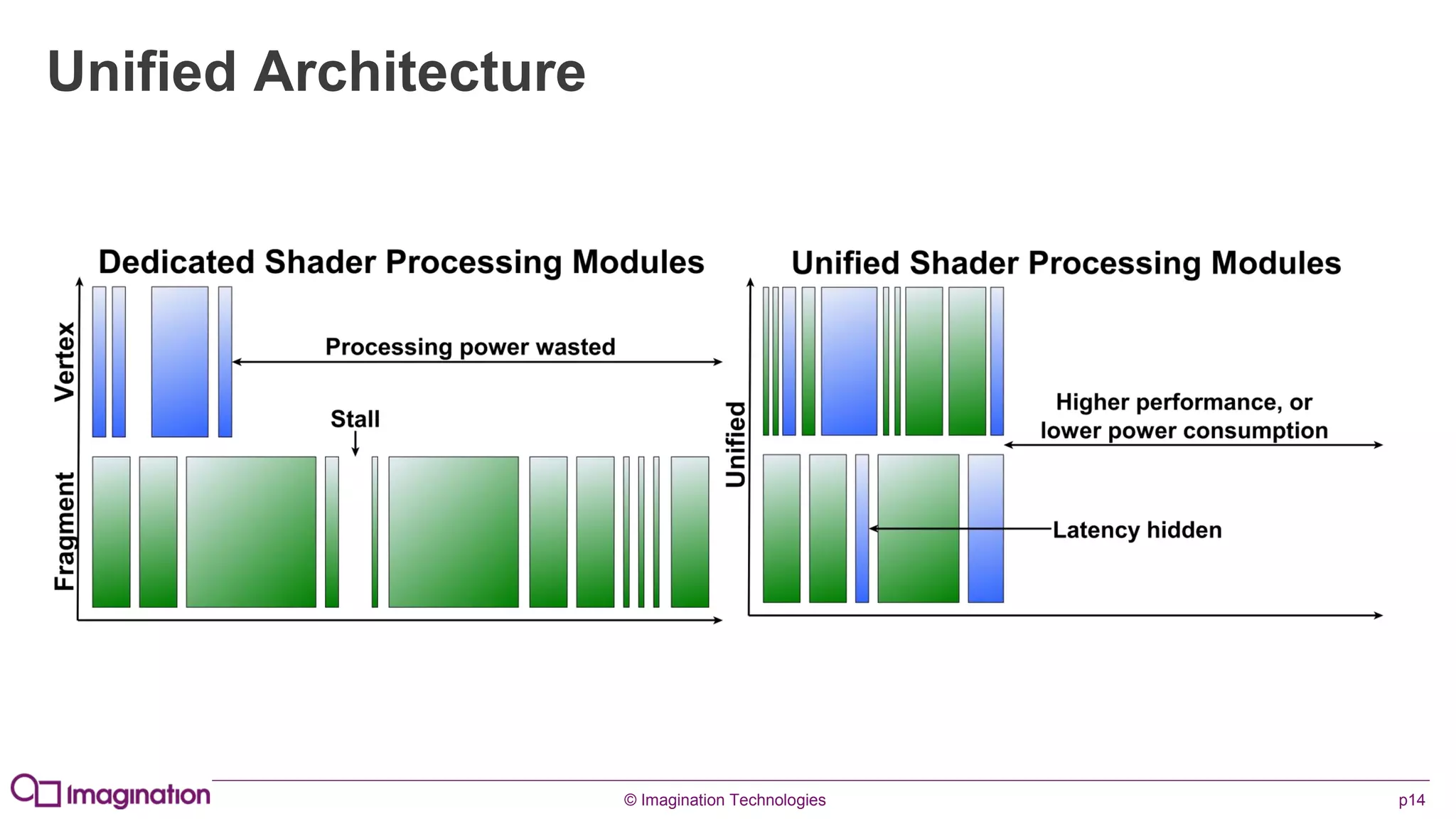

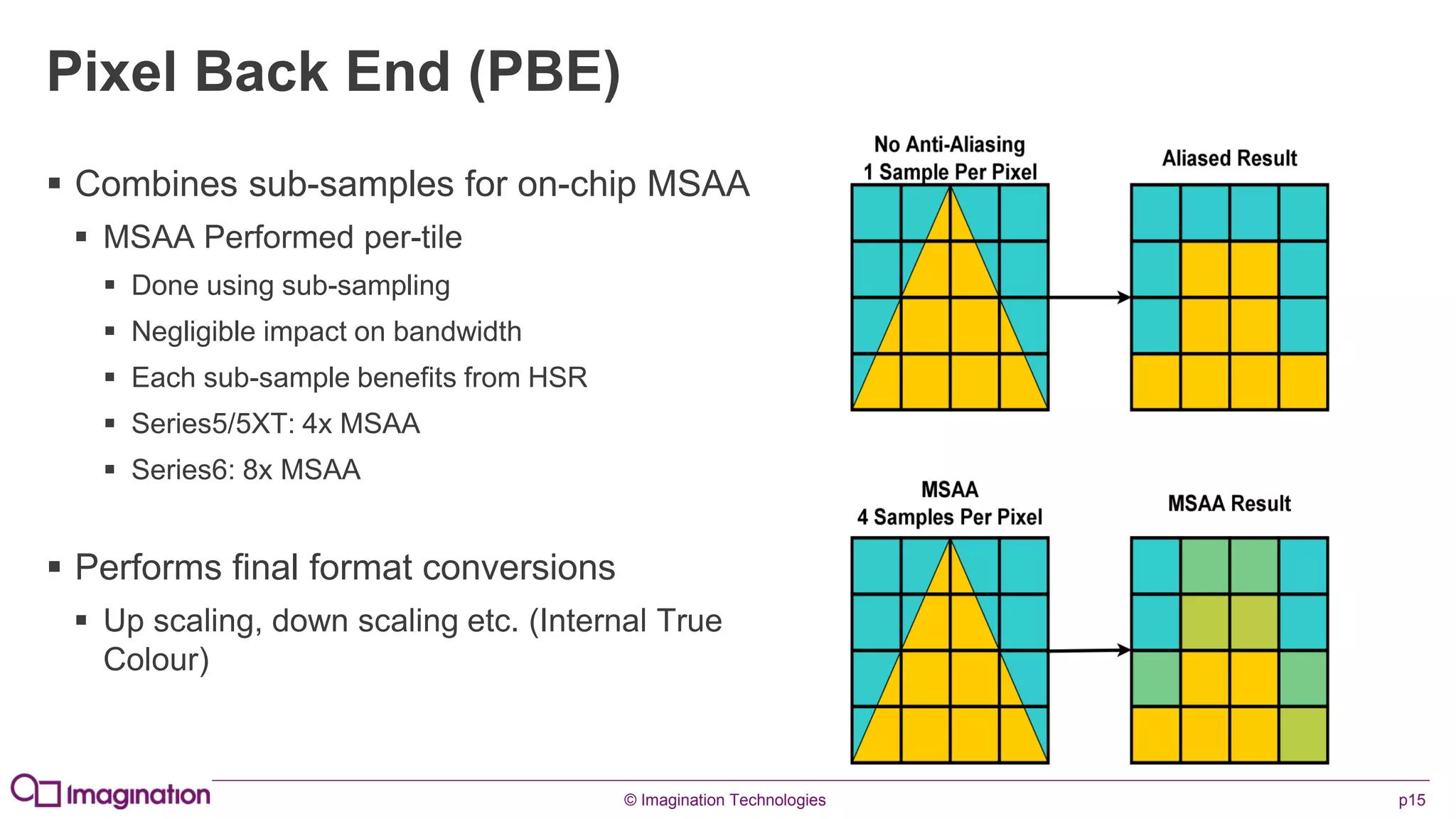

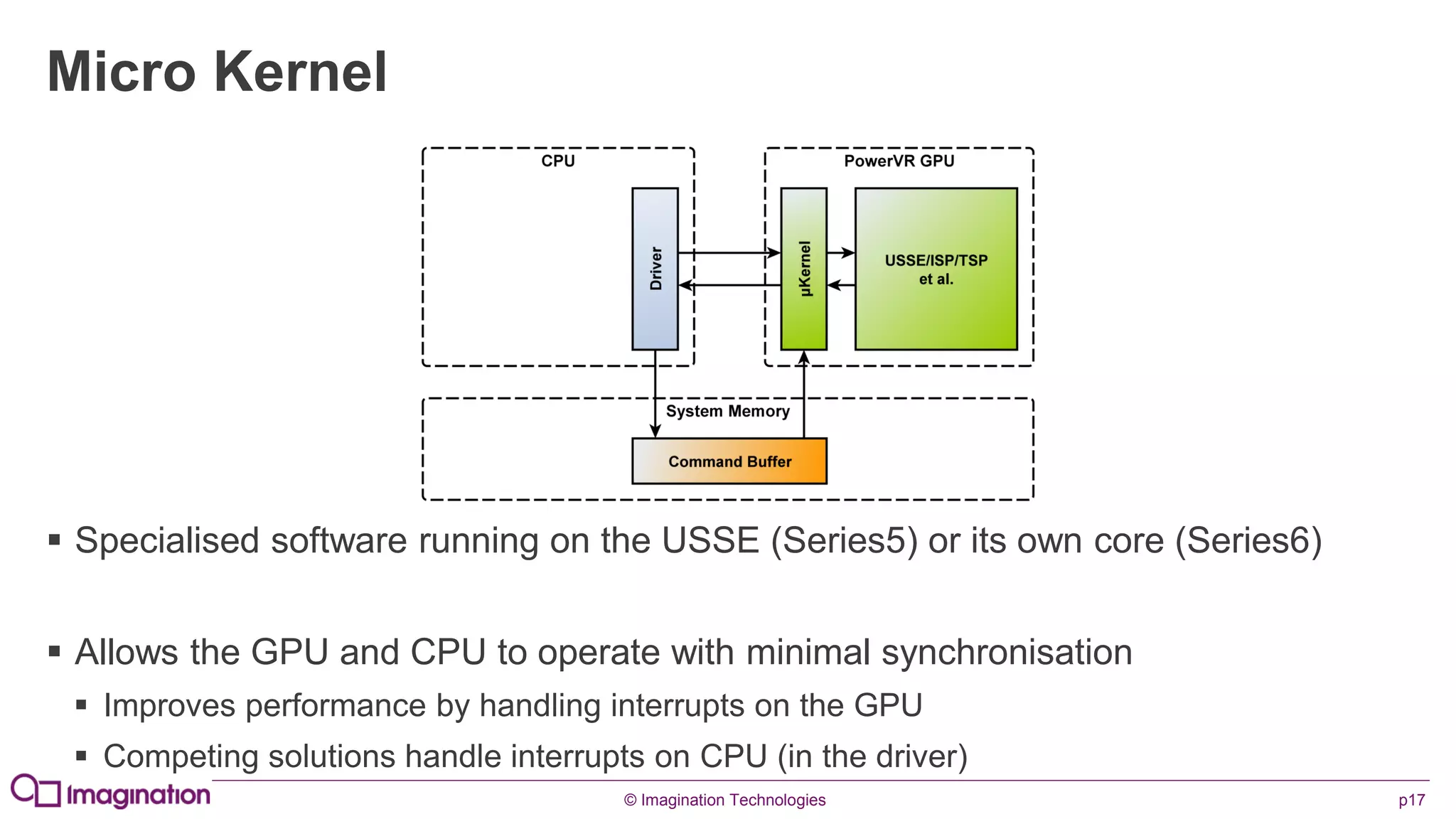

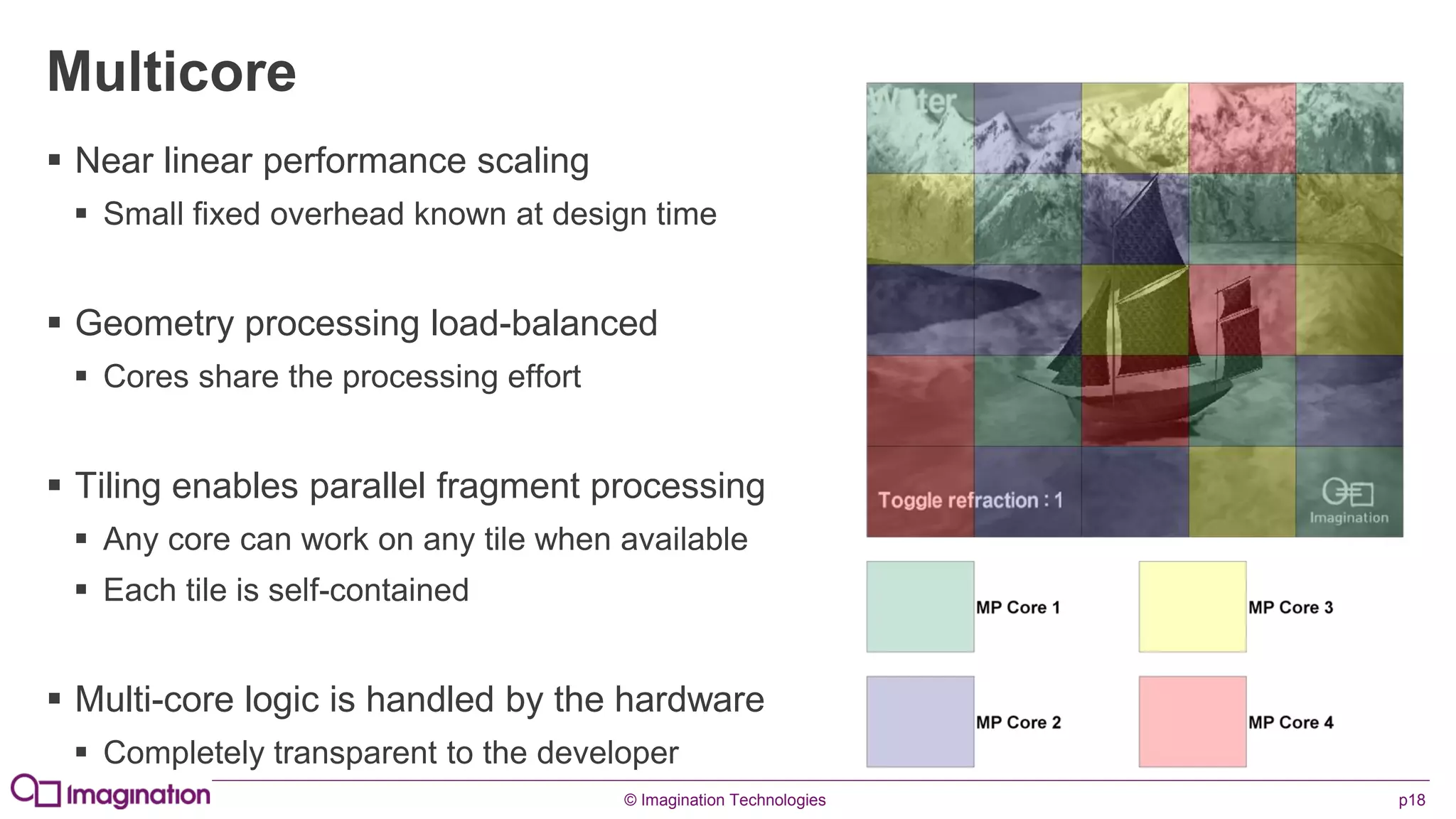

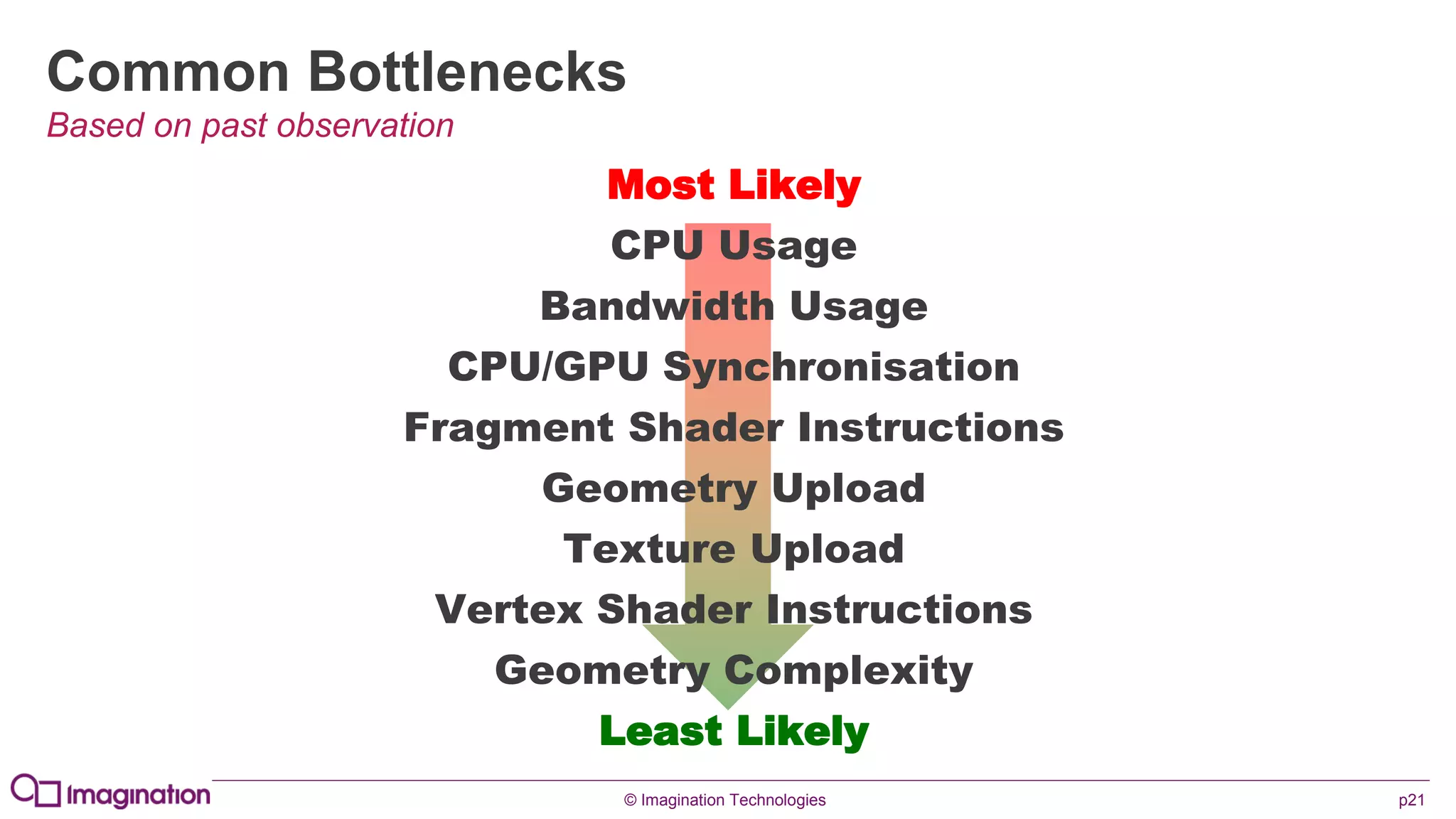

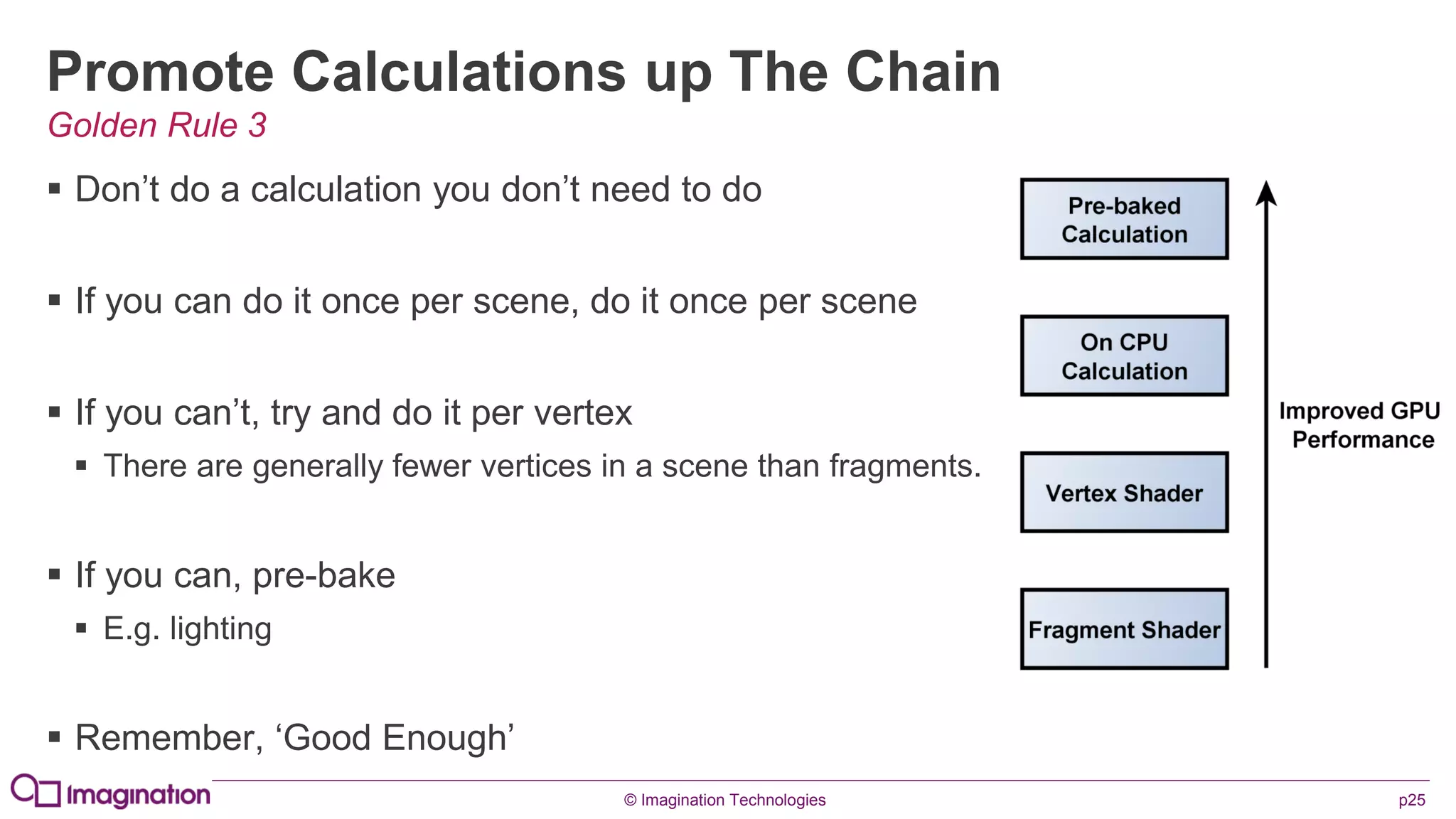

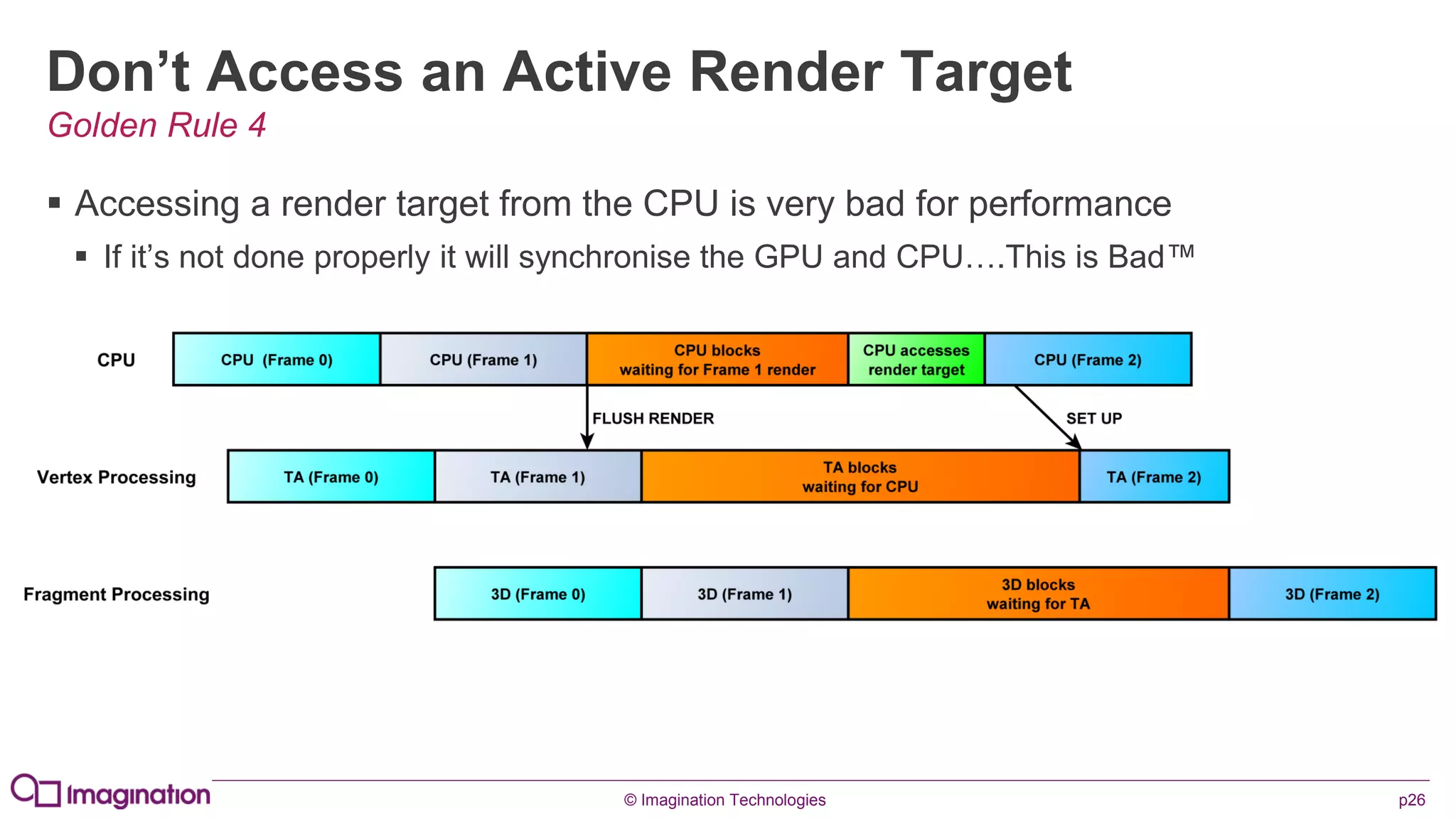

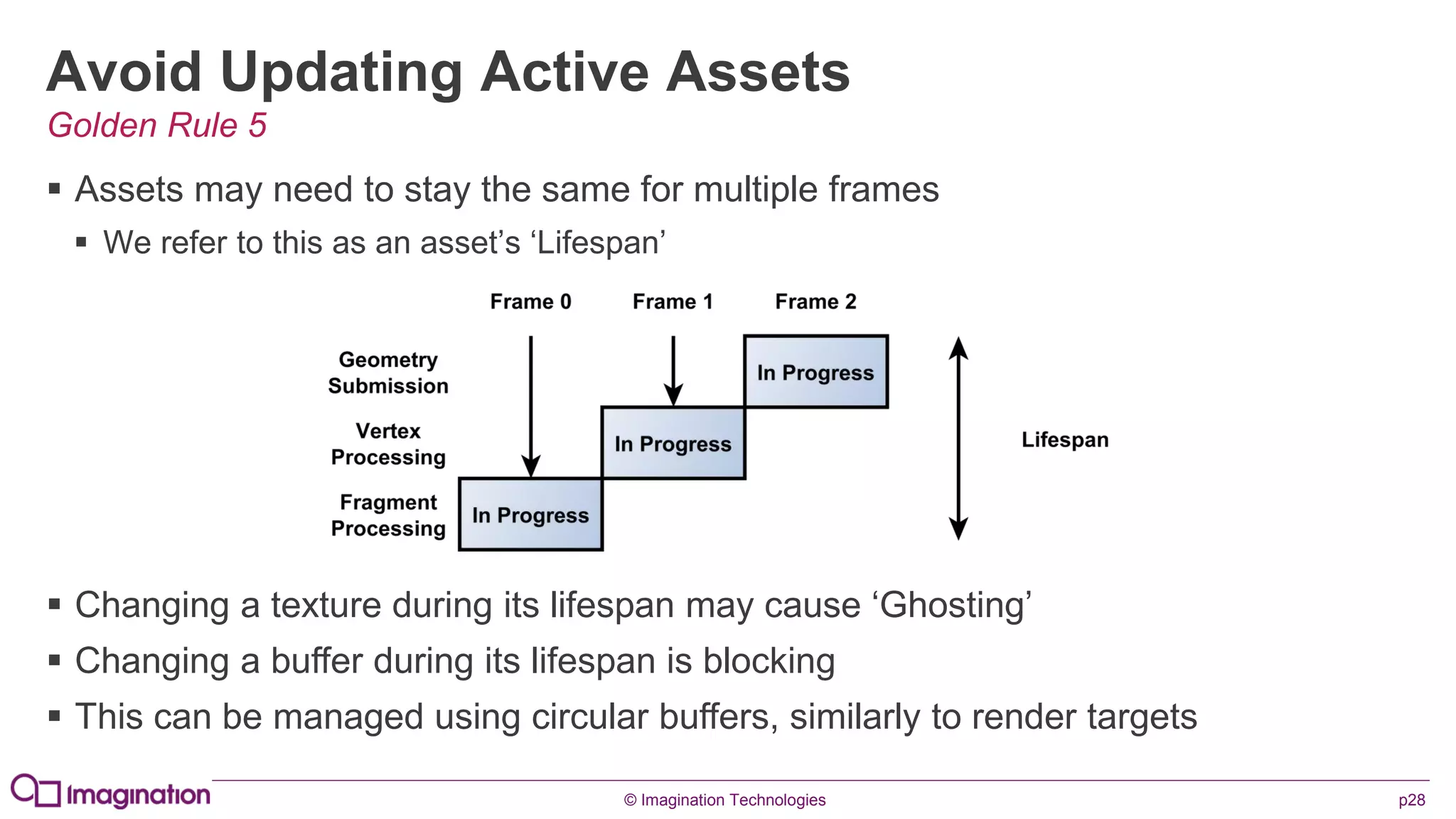

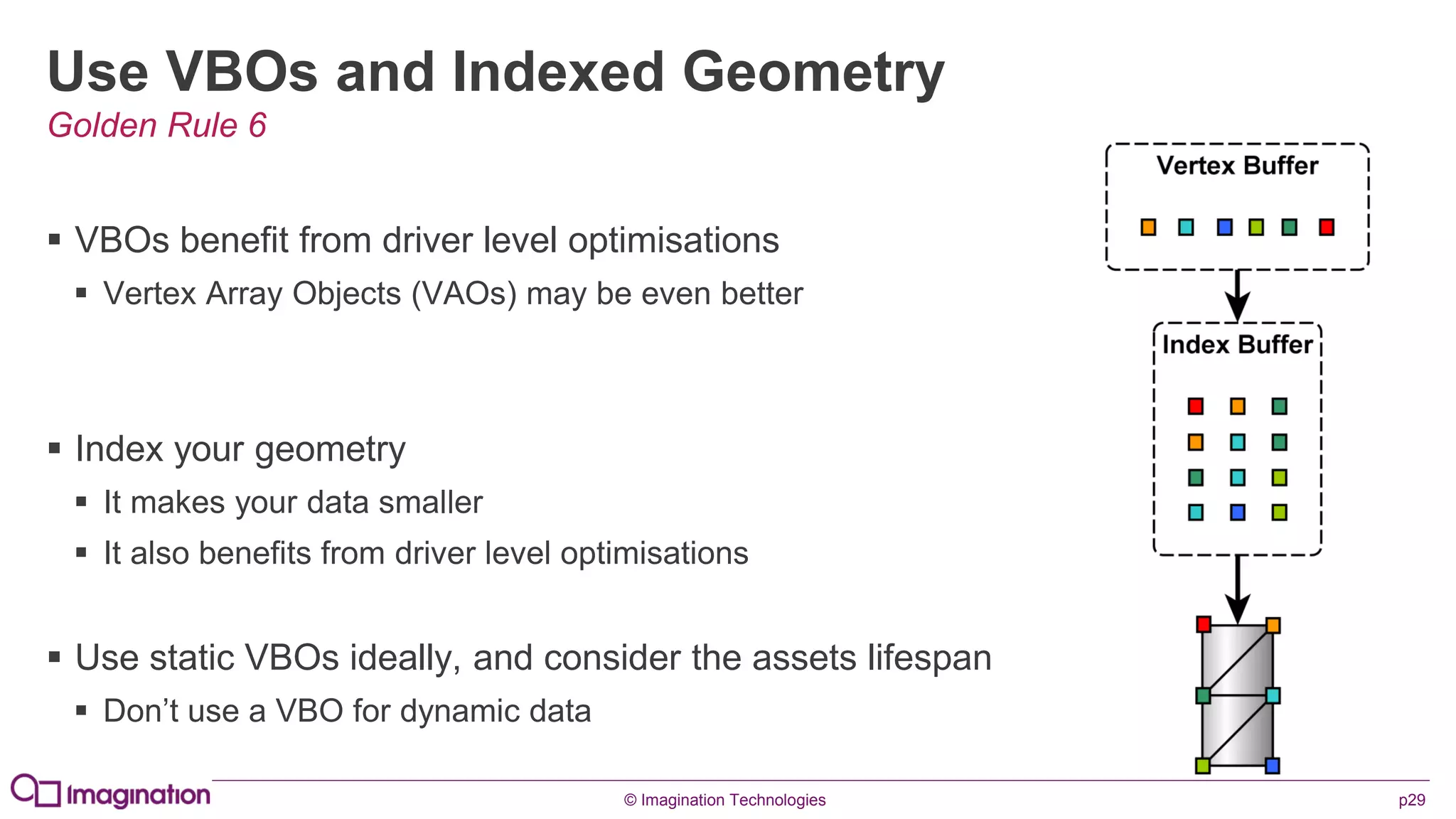

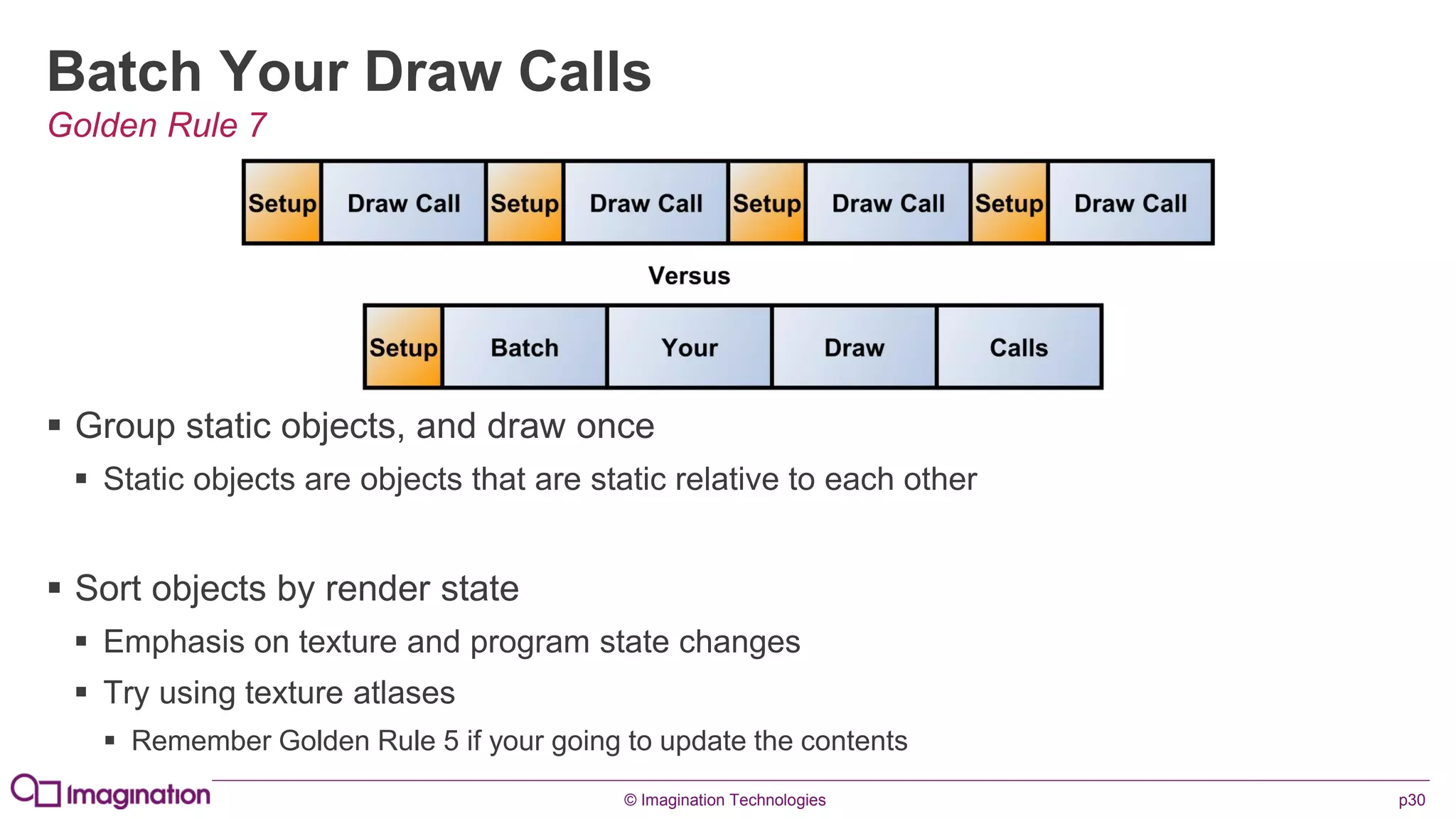

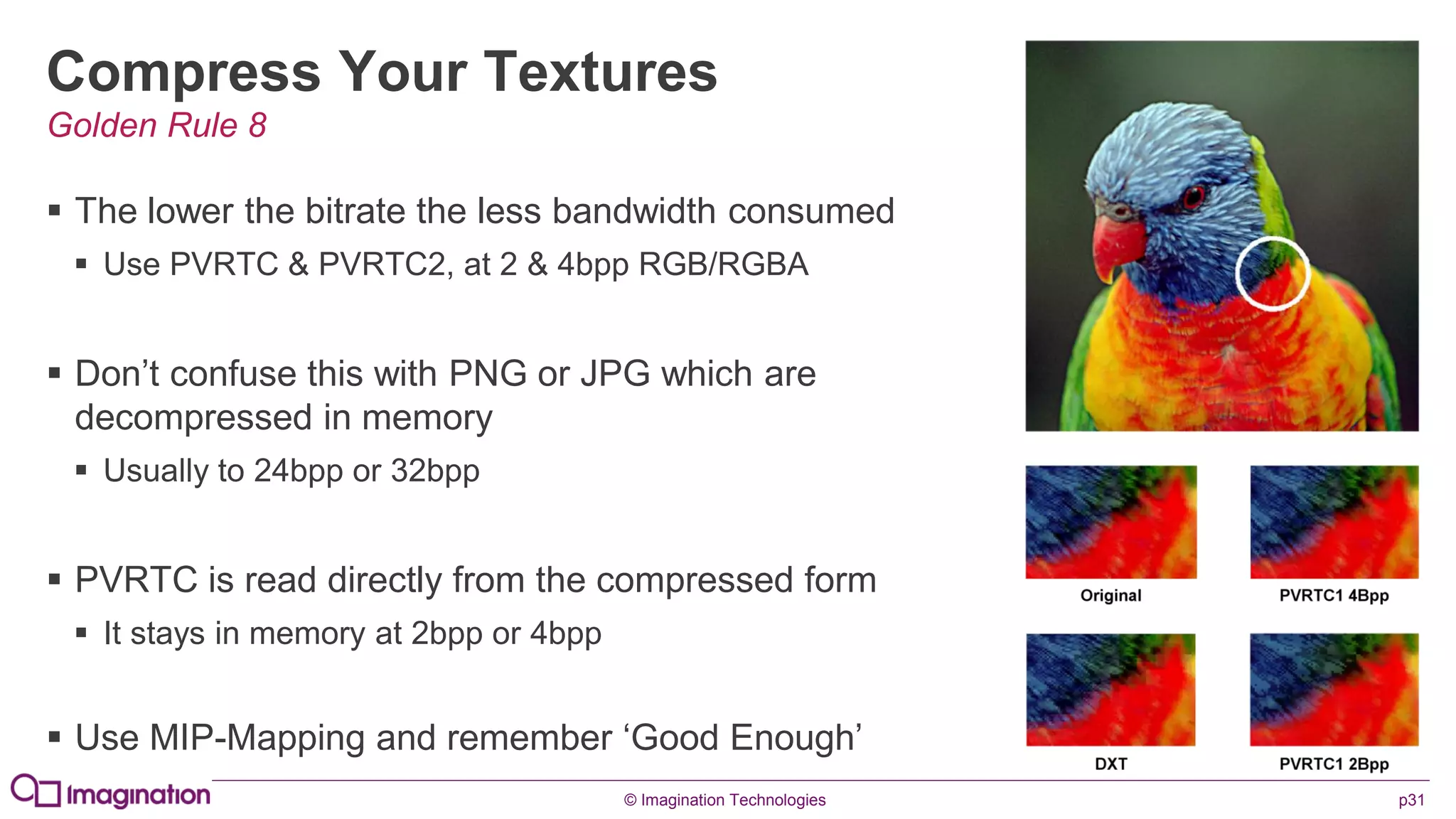

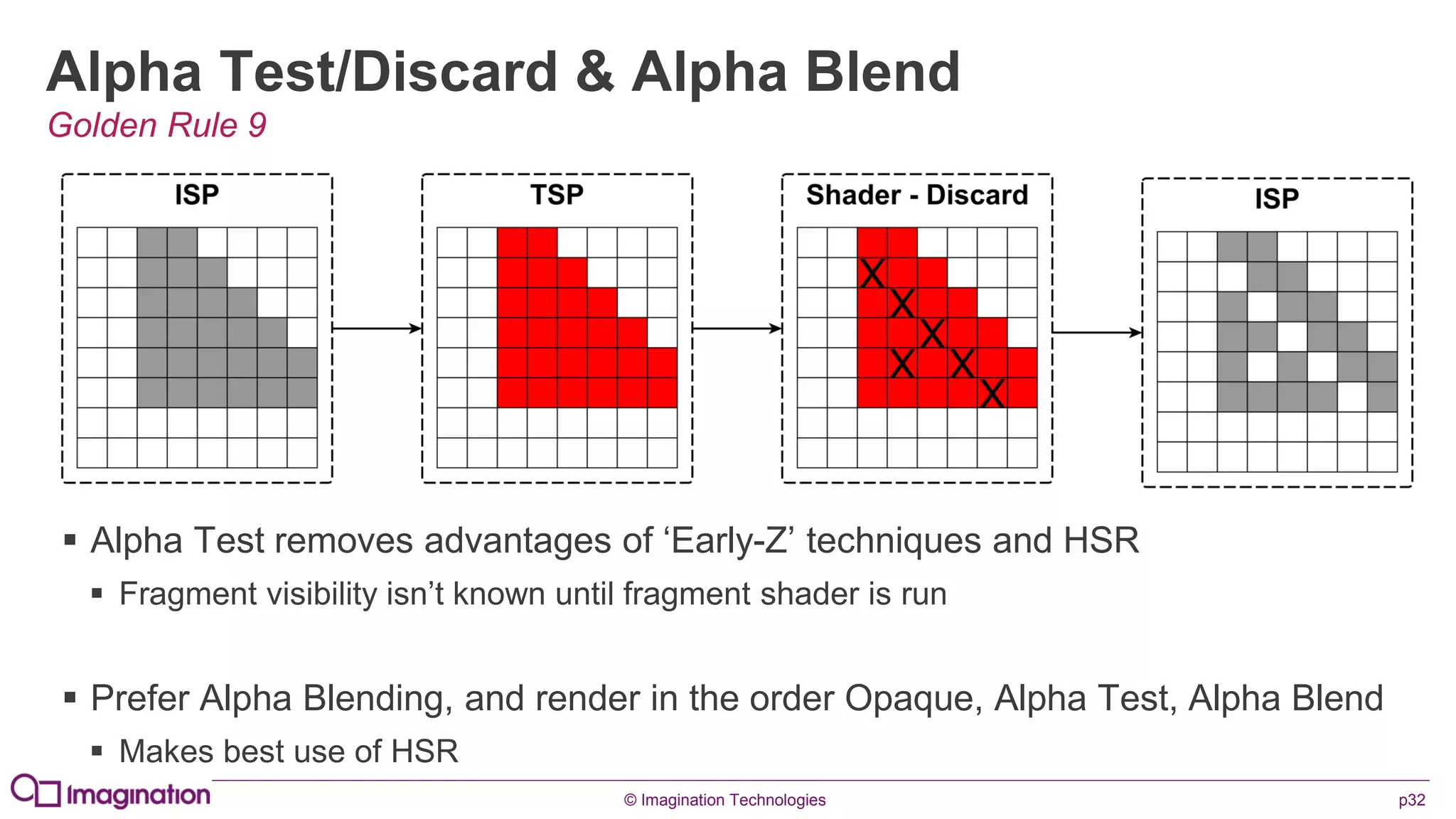

This document provides an overview of graphics processing unit (GPU) architectures and optimization techniques for mobile GPUs. It discusses tile-based deferred rendering architectures like PowerVR, which process graphics per tile to take advantage of on-chip memory. It then provides "golden rules" for optimizing code for mobile GPUs, such as avoiding unnecessary calculations, batching draw calls, using compressed textures, and leveraging the GPU's hidden surface removal capabilities.