This document discusses various concepts in data flow modeling and VHDL, including:

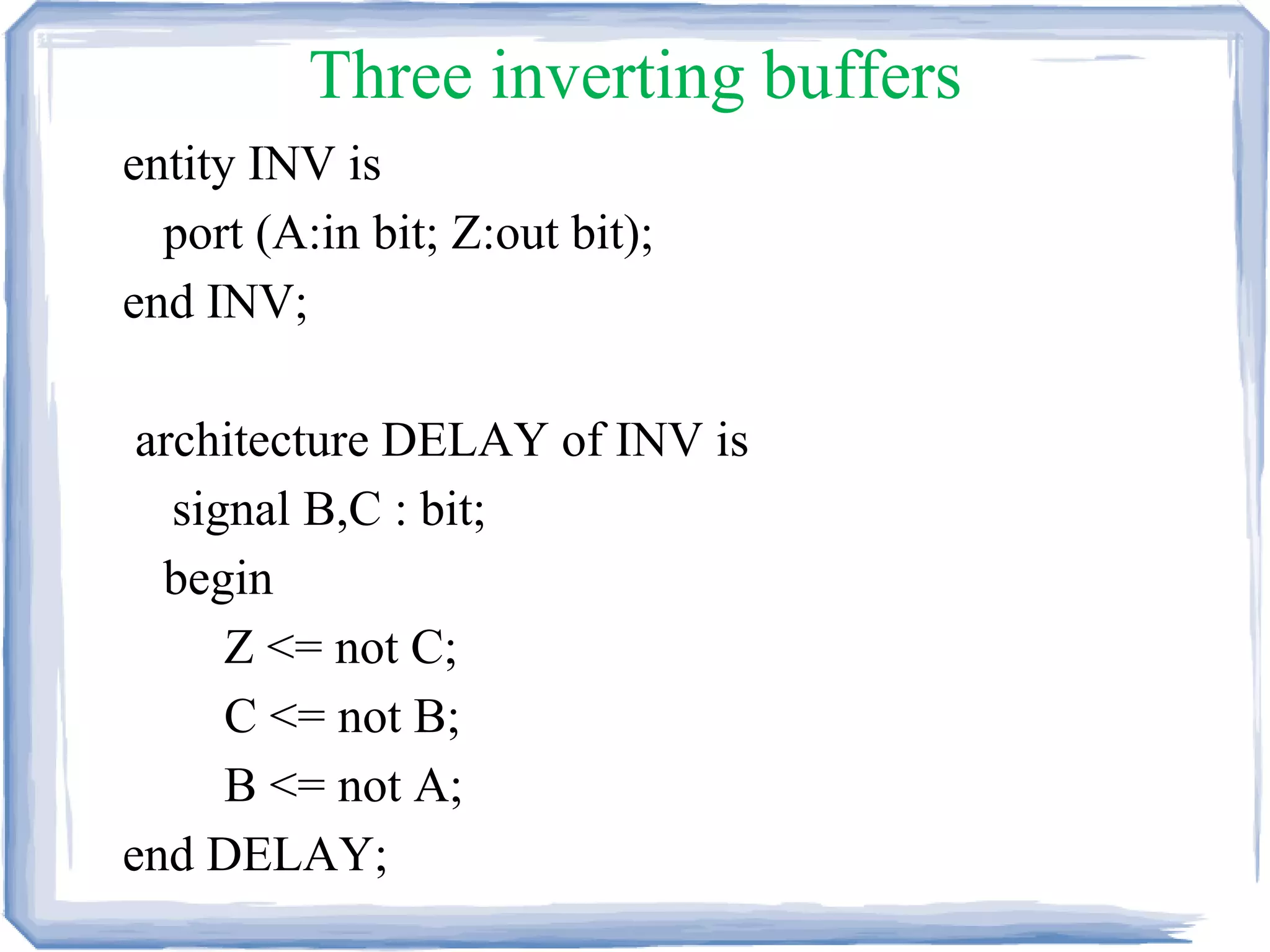

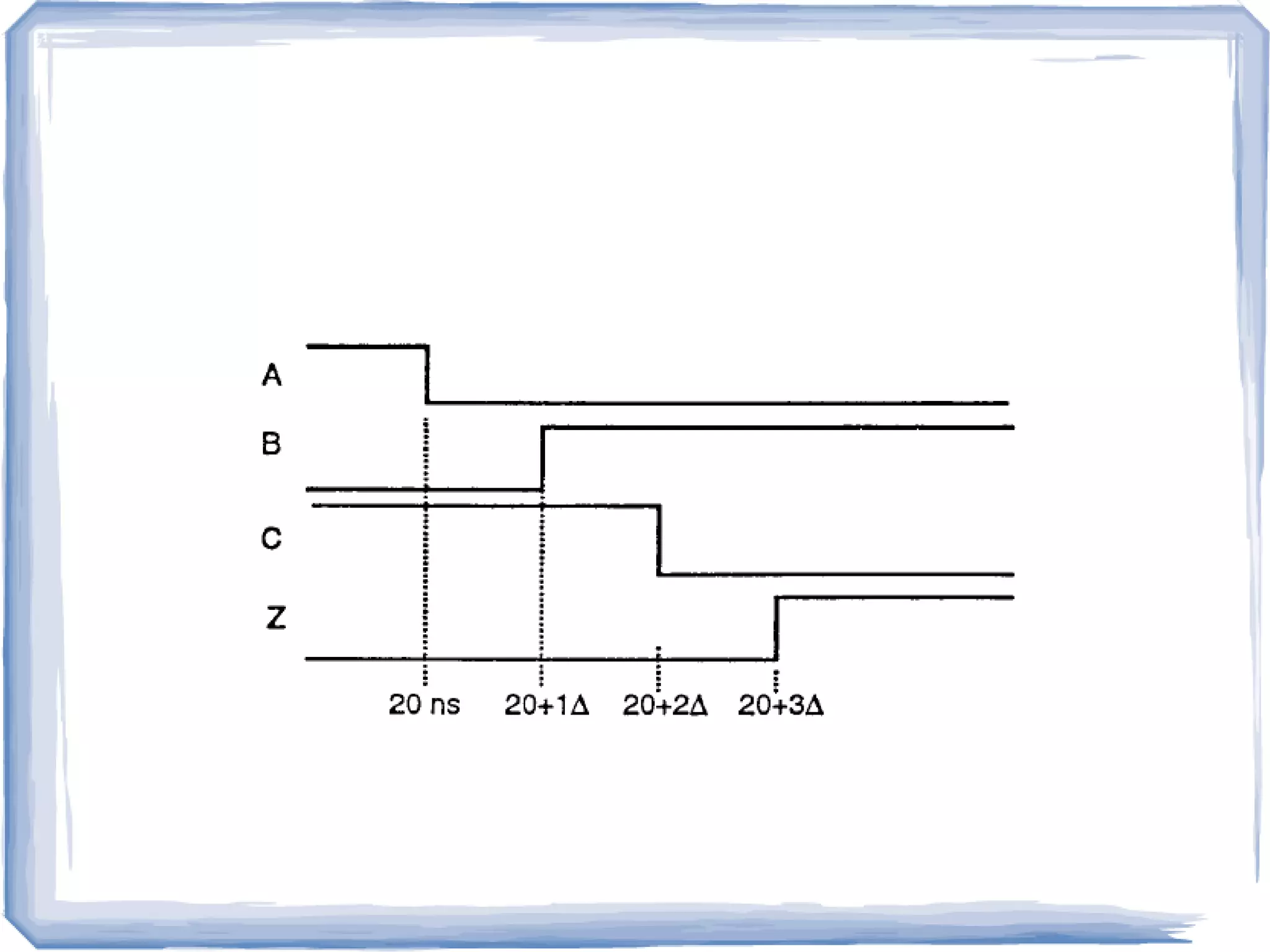

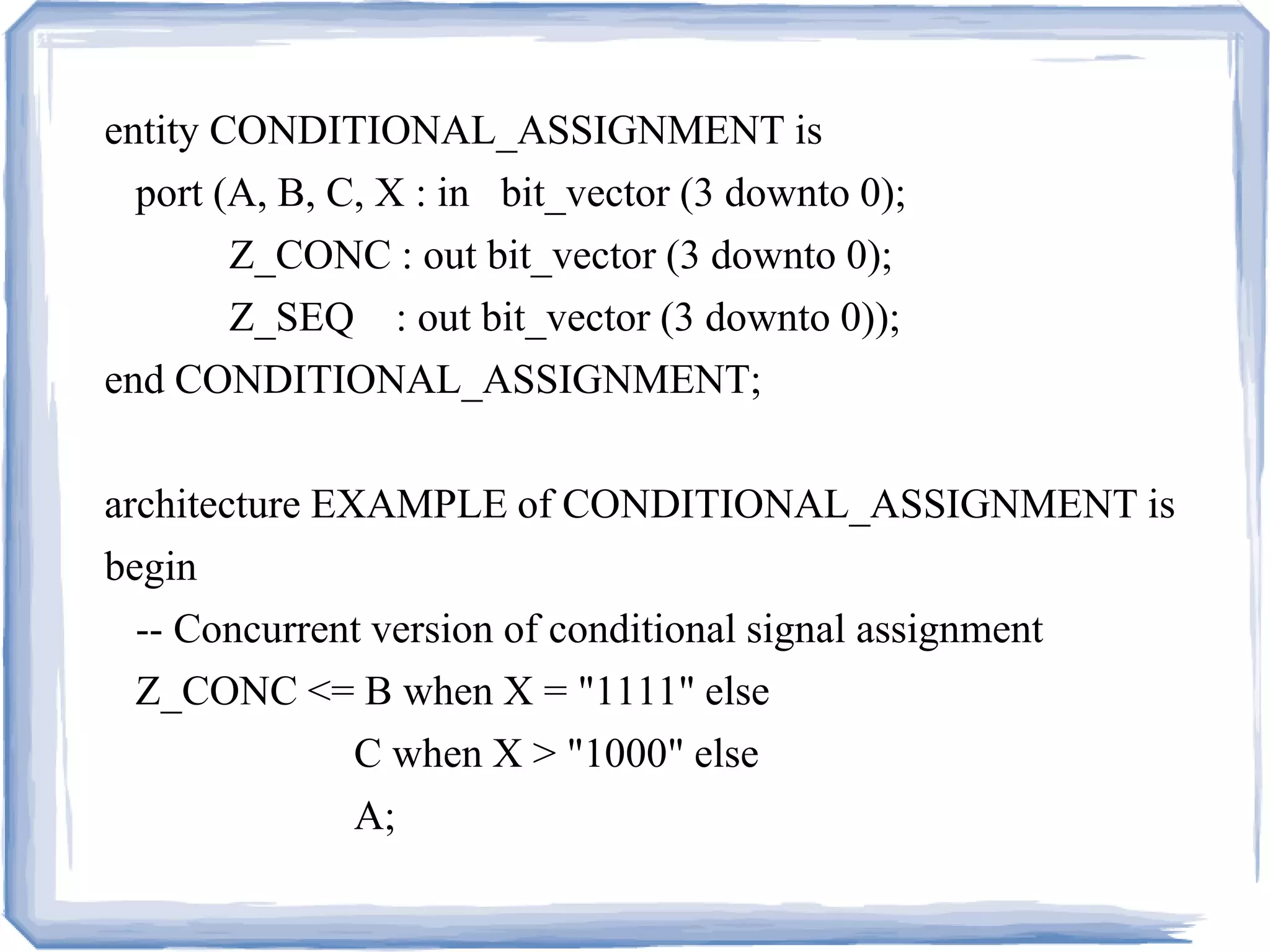

- Using <= to assign signals and define data flow

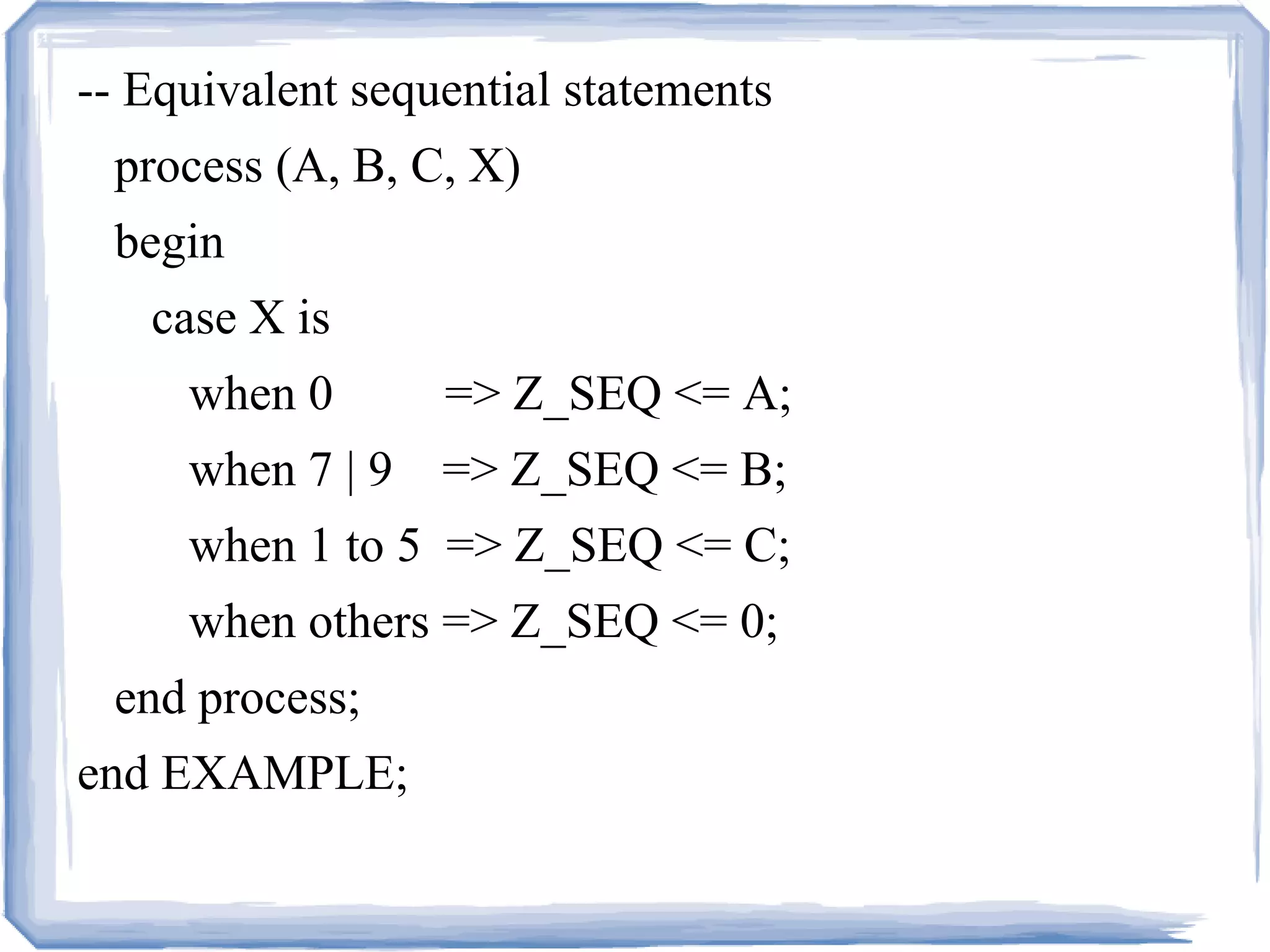

- Concurrent and process modeling

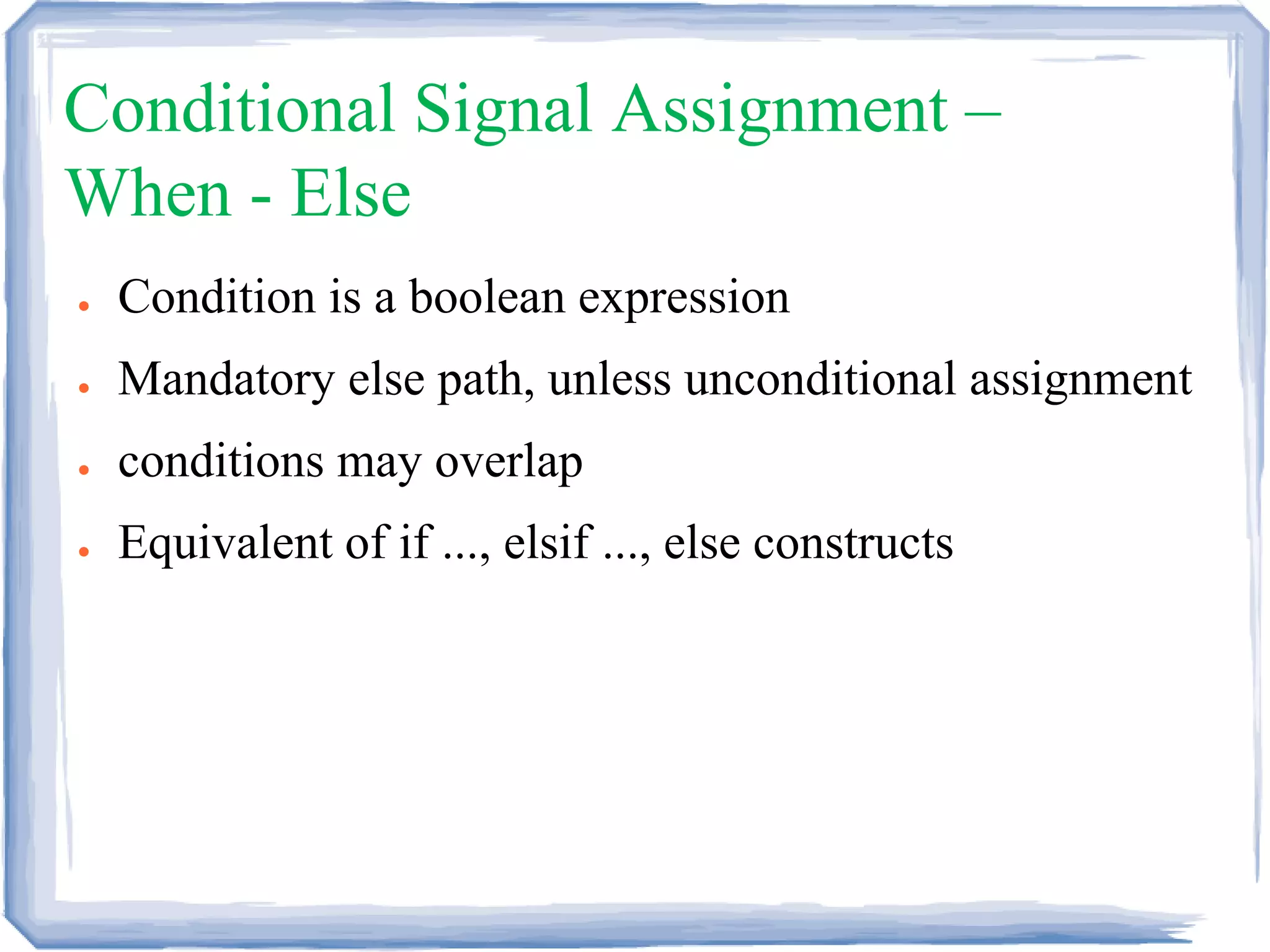

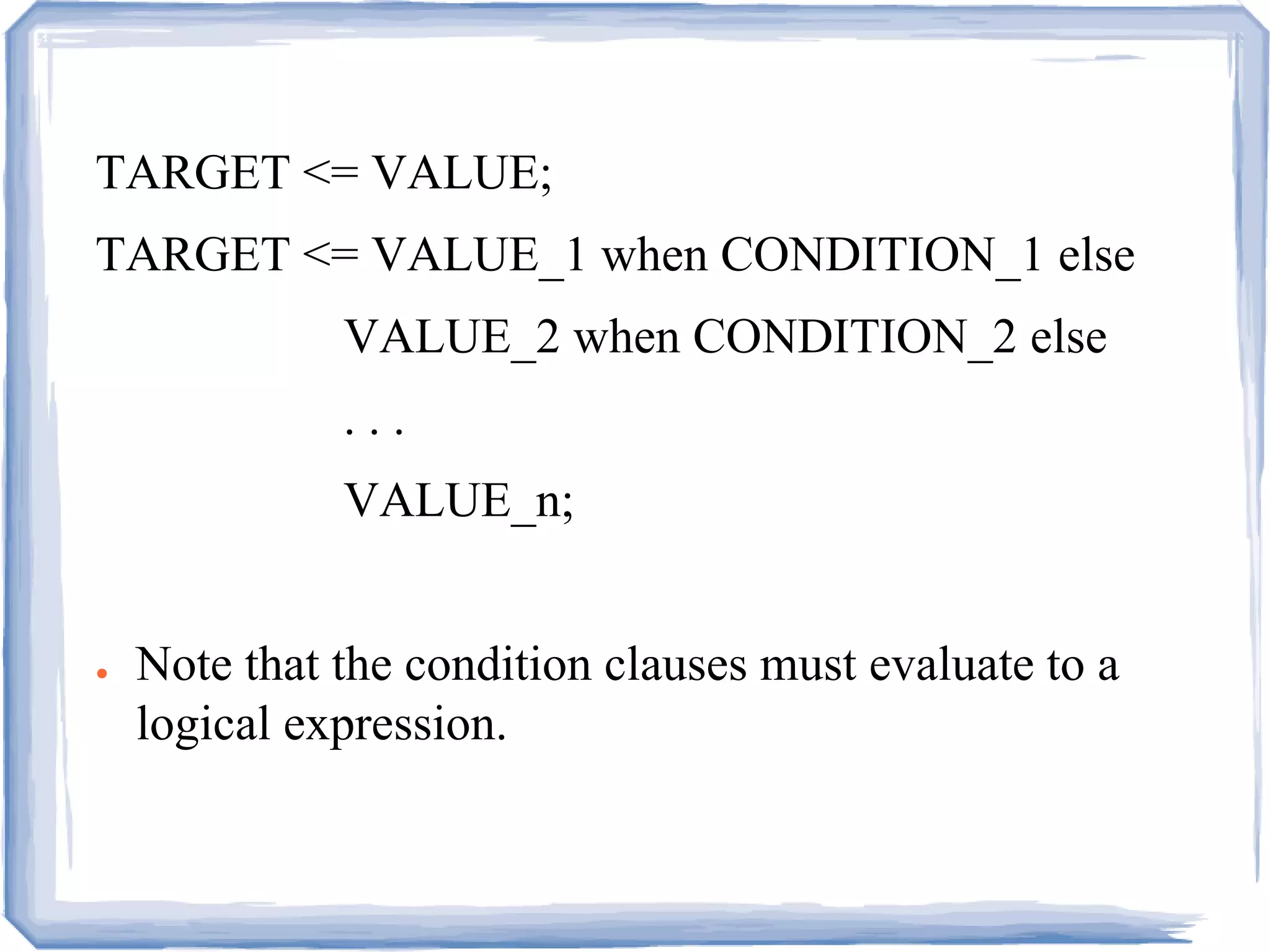

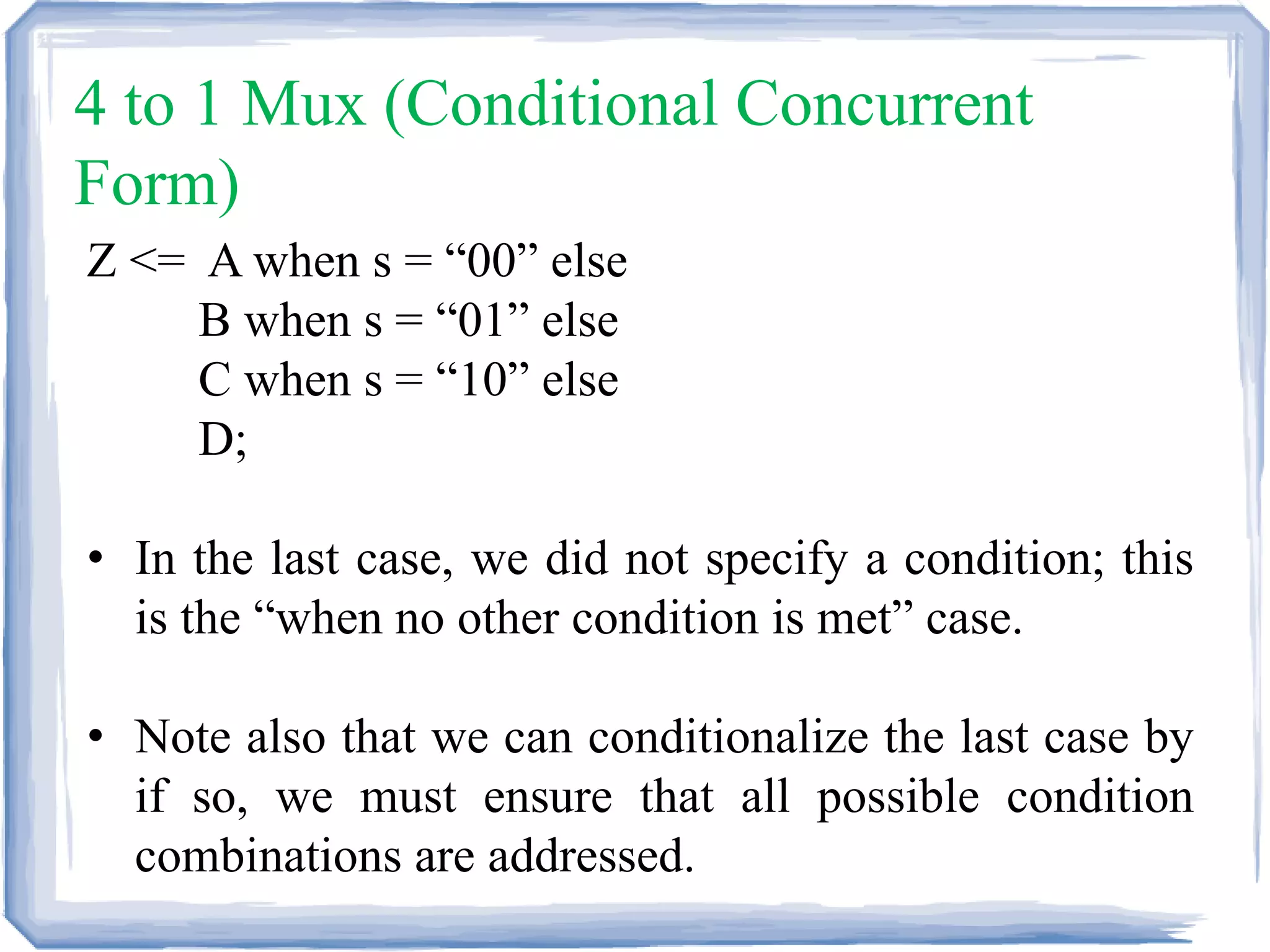

- Conditional signal assignment using when/else and with/select statements

- The unaffected value for conditional assignments

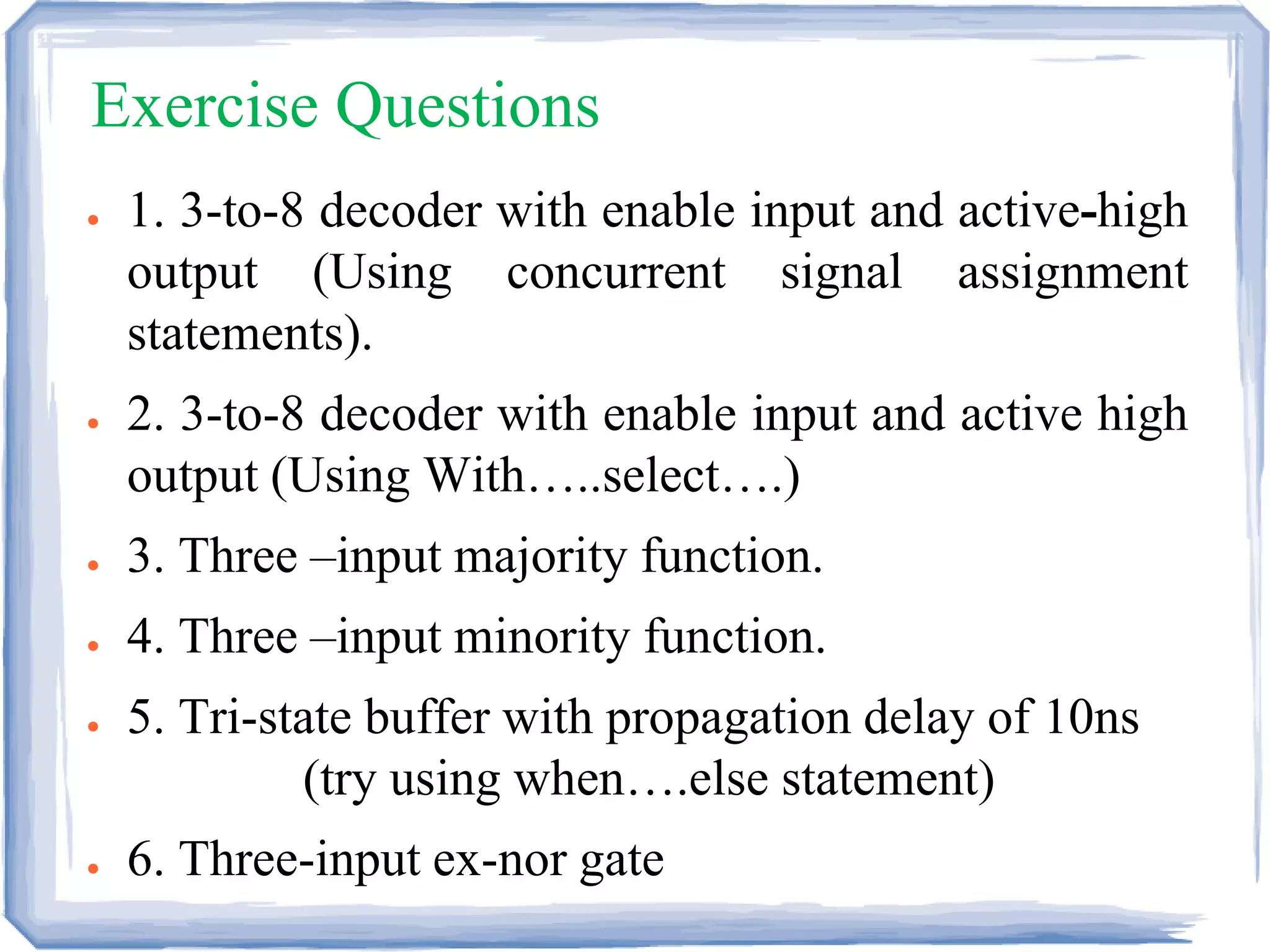

It also provides examples of modeling common logic functions like muxes, decoders, and tri-state buffers in VHDL using these concepts.

![References

● [1]. “Digital Systems Design Using VHDL” by

Charles H Roth, Jr., Thomson Learining,

Brooks/Cole.

● [2]. “VHDL Primer” by J Bhasker, PHI, Third

edition.](https://image.slidesharecdn.com/ddhdl16-160829193729/75/Ddhdl-16-18-2048.jpg)