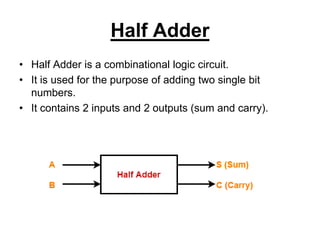

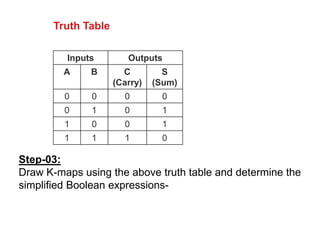

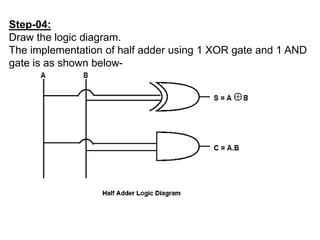

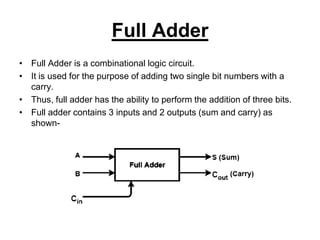

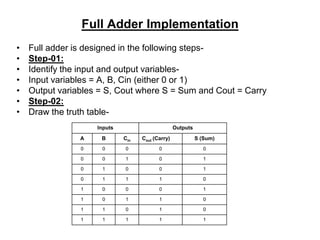

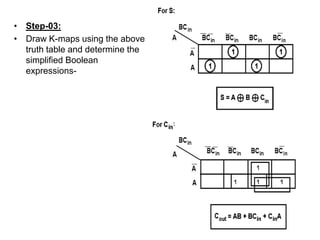

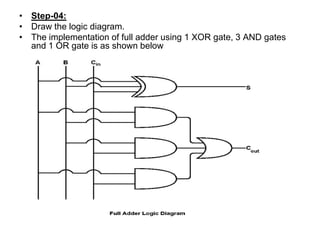

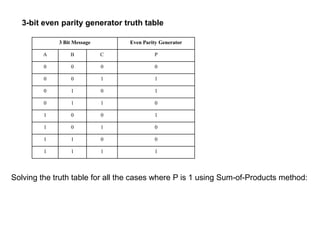

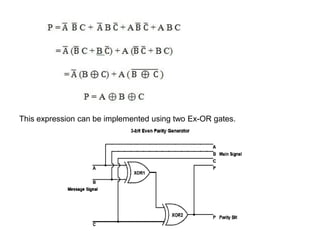

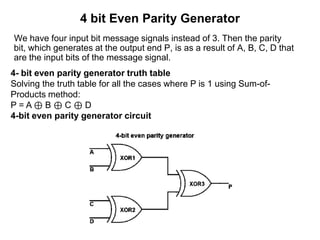

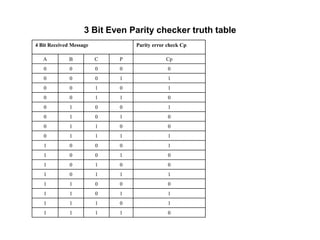

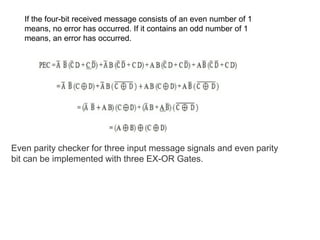

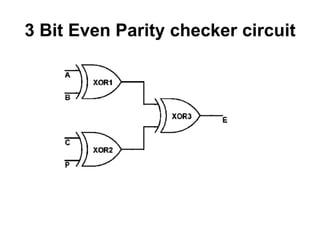

The document discusses digital logic design and describes half adders, full adders, parity generators, and parity checkers. It provides details on their implementation including truth tables and logic diagrams. Specifically, it explains that a half adder can add two single bits but has limitations, while a full adder can add three bits including a carry bit. It also describes how even and odd parity generators work and provides truth tables for 3-bit and 4-bit even parity generators. Finally, it discusses how even parity checkers can detect errors by checking if the total number of 1s is even.