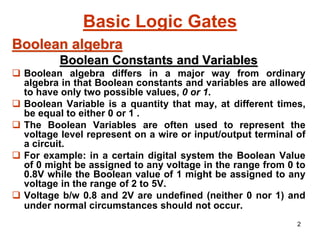

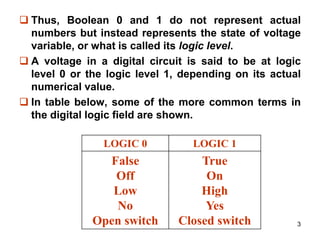

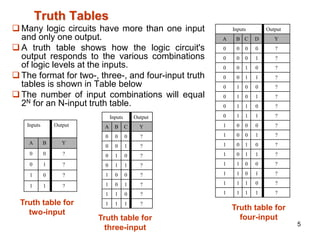

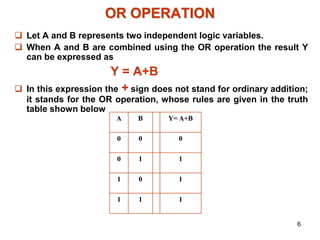

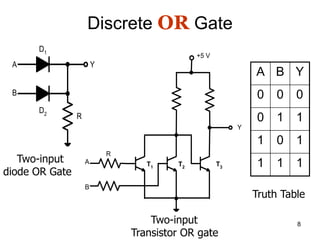

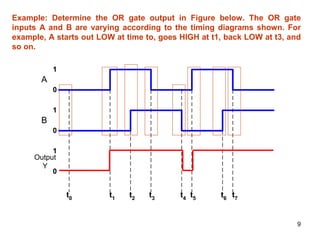

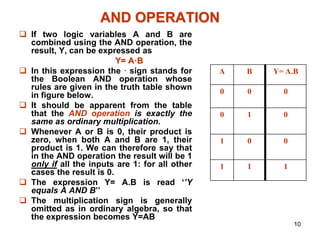

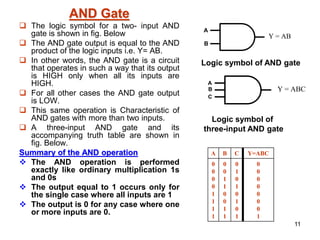

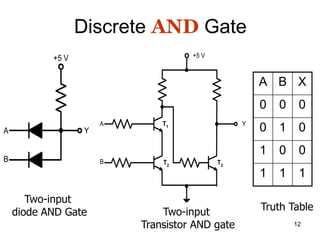

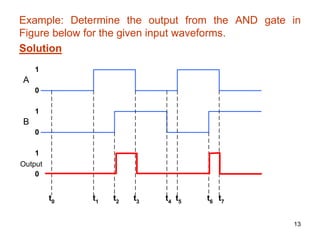

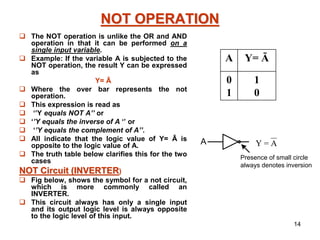

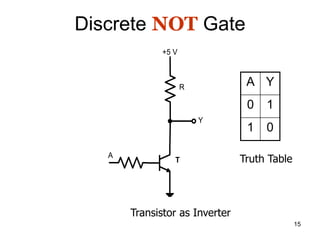

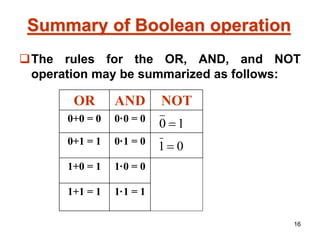

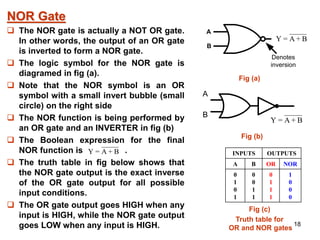

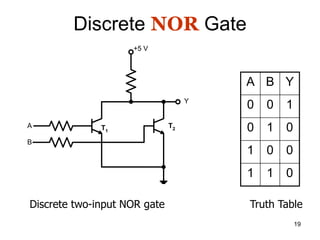

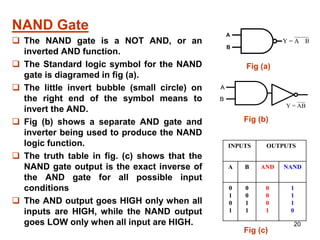

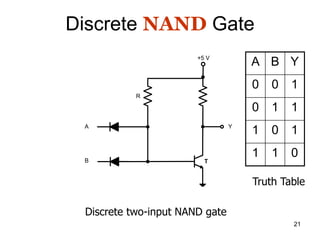

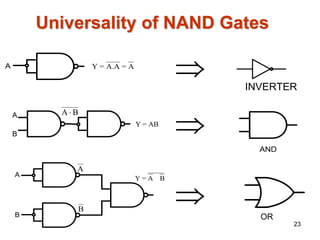

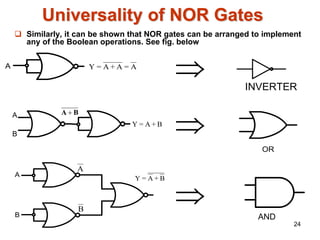

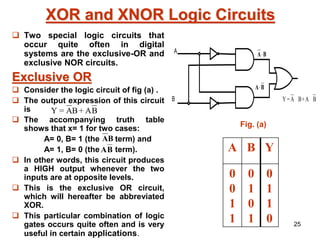

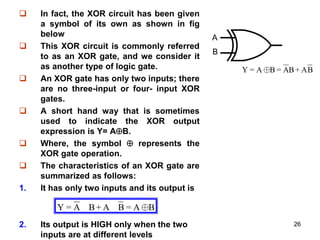

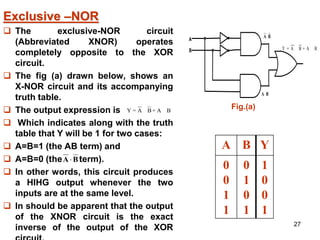

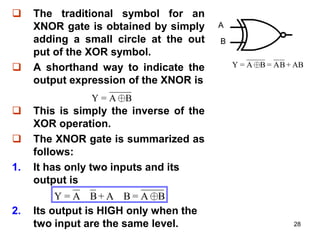

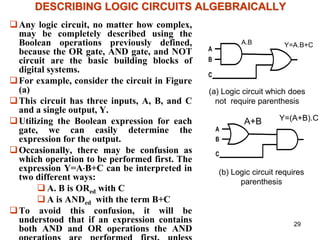

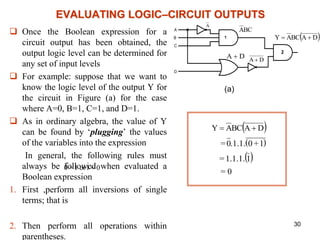

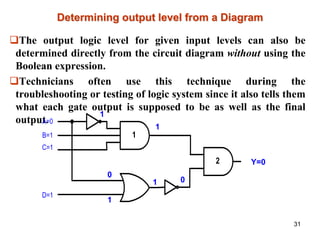

The document explains the fundamentals of Boolean algebra and logic gates, which have only two values (0 and 1) representing voltage levels in digital circuits. It elaborates on basic logic operations such as AND, OR, and NOT, along with derived logic gates like NAND and NOR, and their truth tables. Additionally, the document covers exclusive operations (XOR and XNOR) and discusses the universality of NAND and NOR gates in implementing any Boolean expression.