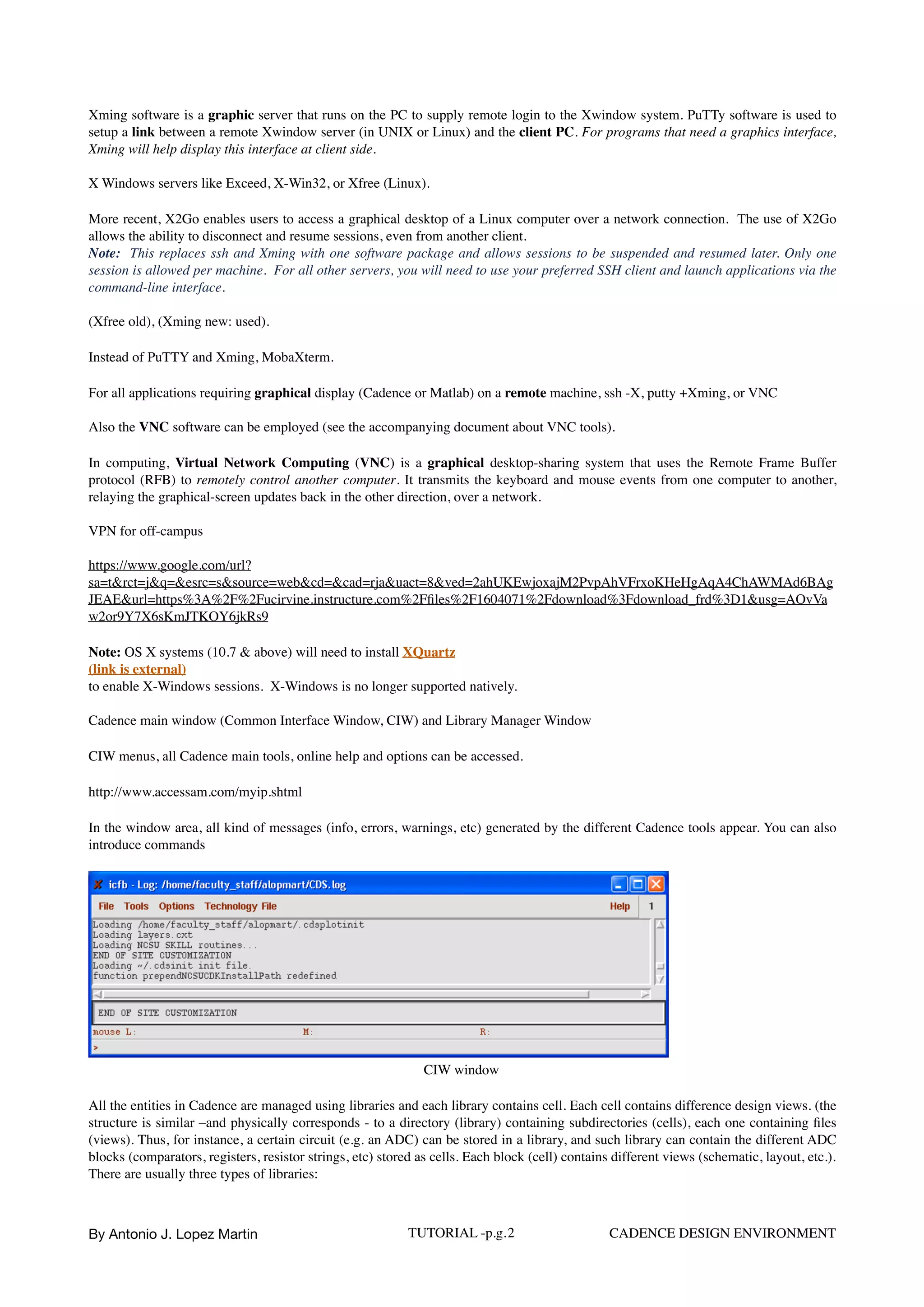

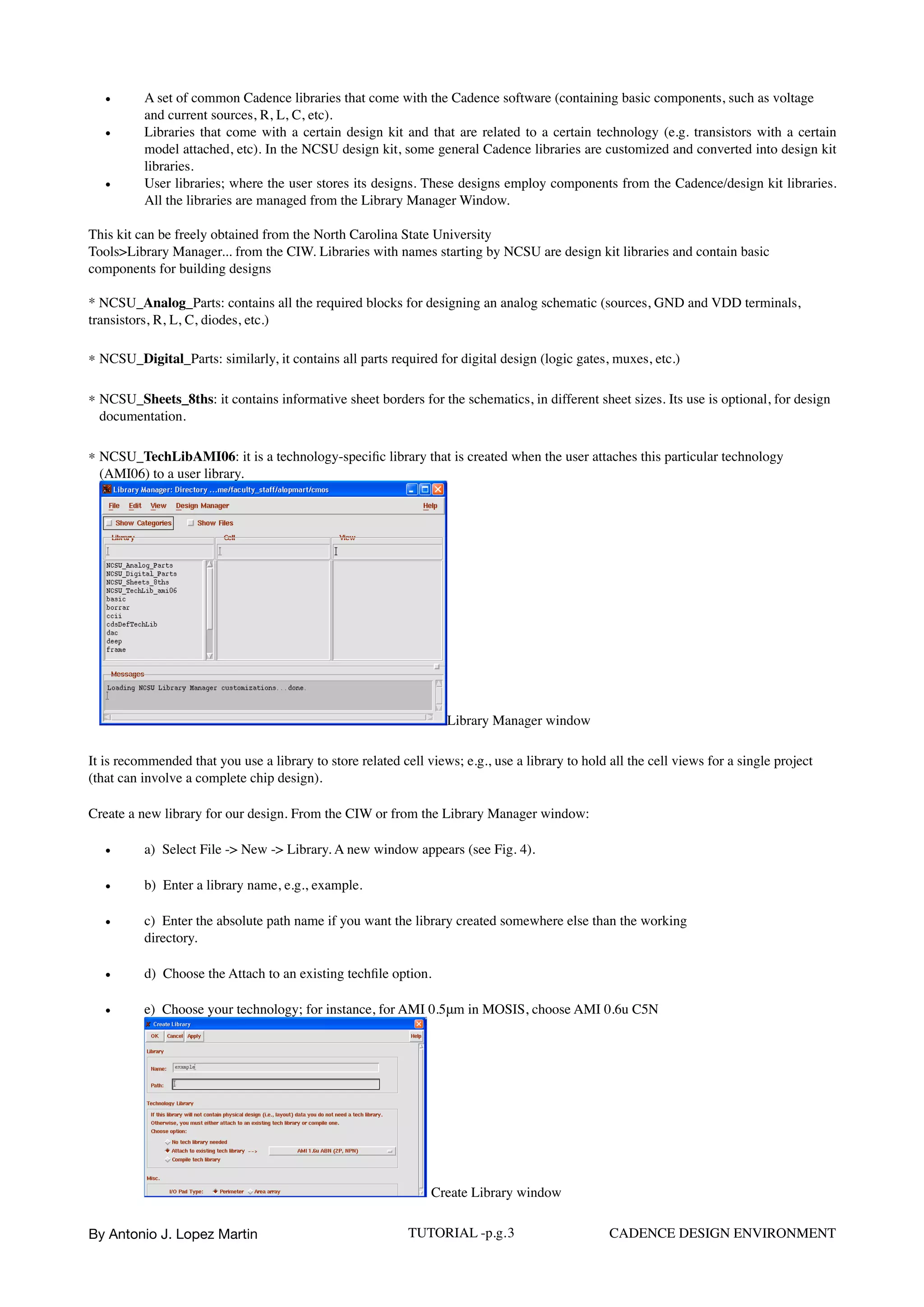

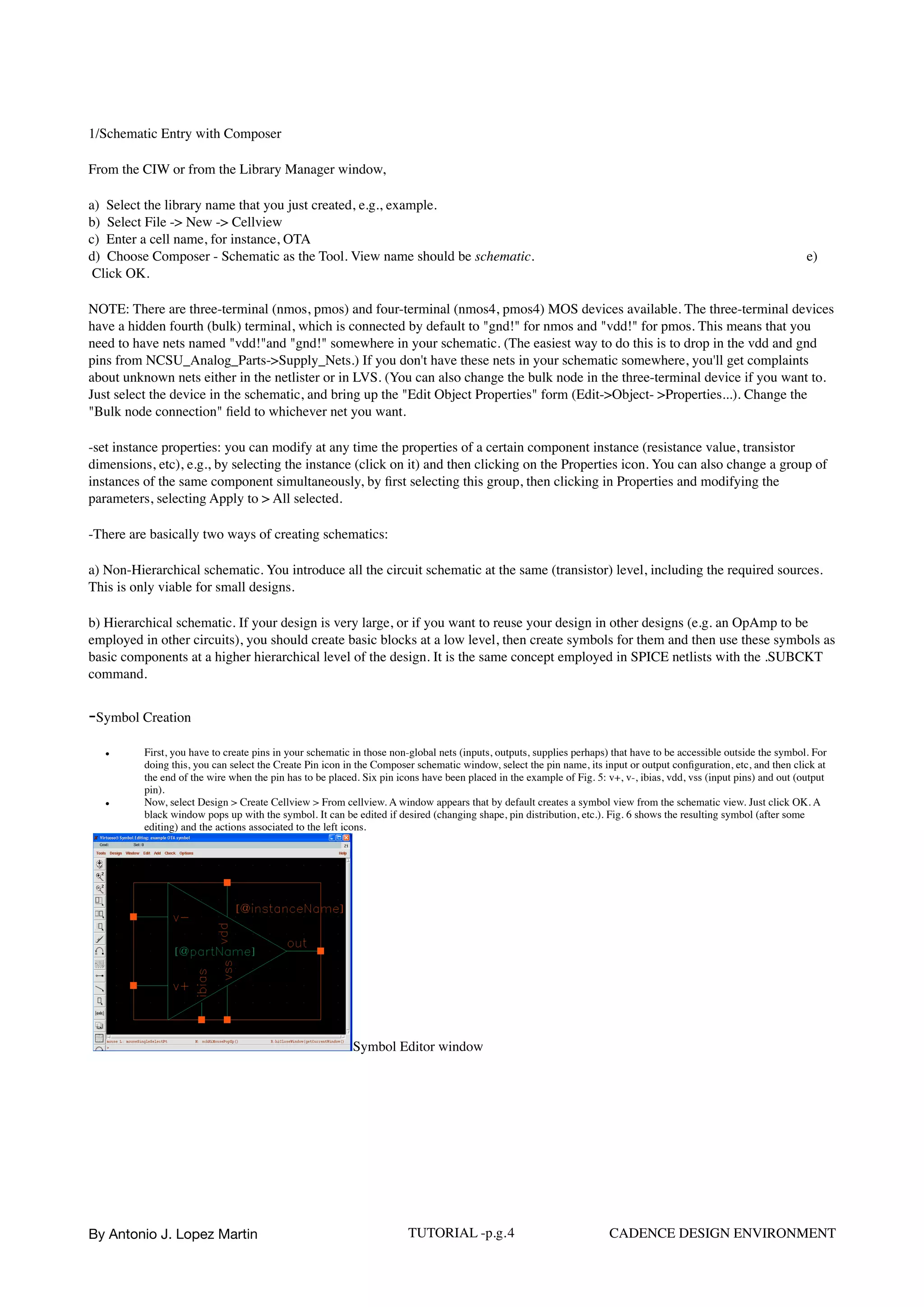

Unix is a family of operating systems derived from the original AT&T Unix developed in the 1970s at Bell Labs. Linux is an open source operating system based on the Linux kernel, which was created by Linus Torvalds in 1991. Xming and PuTTY are software tools used to enable graphical interfaces over remote connections between Windows PCs and Unix/Linux systems. Virtual Network Computing (VNC) is another graphical desktop sharing system that can be used instead of Xming and PuTTY.