The document describes two designs for a 1024-bit shift register: Design A uses a traditional approach with 1024 1-bit registers, while Design B uses an alternative approach with 1024 1-bit enable registers, a 10-bit counter, 1024-to-1 multiplexer, and 10-to-1024 decoder to reduce power consumption at the cost of increased area. A comparison shows that Design B has 72% higher area but 20% lower dynamic power and 39% higher leakage power than Design A. Assumptions made about the power characteristics of components in Design B are also provided.

![© 2003 Karthik Ethirajan, all rights reserved

An Example: Shift Register Power Vs. Area trade-off

Design A is the traditional shift register design and design B is an alternative for better power.

085-059

d q d q d qdin

clk

[1023] [1022] [0]

Design A

dout

d q

en

d q

en

[1023]

d q

en

[1022]

dout

din

clk

[1023]

[0]

[0]

[1022]

[0]

[1022]

[1023]

10 10

10

Design B

d0 d1 d1023 d1024 d1025

d0 d1 d1023 d1024 d1025

0 1 1023 0 1

d0 d1024

d1023

clk

din

dout

en0

en1

en1023

mux_sel

q0

q1 d1 d1025

q1023

C

O

U

N

T

E

R

E

R

E

C

O

D

D

Design A = 1024 x 1-bit register

Design B = 1024 x 1-bit enable registers

+ 10-bit counter -- 10 x 1-bit register + 10-bit adder (interpolate from 8-bit adder)

+ 1024-to-1 mux -- (128 + 16 + 2) x 8-to-1 mux + 1 x 2-to-1 mux

+ 10-to-1024 decoder -- ~ 1024-to-1 mux

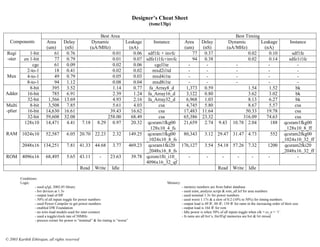

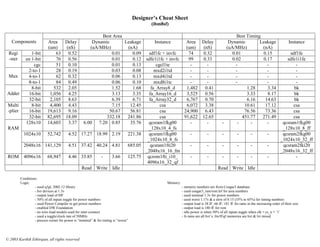

for tsmc13lp process Design A Design B % Change from Design A B

Area (microns) 62,464 107,578 +72%

Dynamic Power (uA/MHz) 10 8 -20%

Leakage Power (nA) 61 85 +39%

Assumptions for Design B:

1. When output of a register is not toggling it consumes 50% less dynamic power

2. Area of 10-to-1024 decoder is the same as 1024-to-1 mux

3. Mux consumes negligible dynamic power since only one input toggles every cycle

4. Dynamic power for the decoder equals 1/8th

that of 146 x 8-to-1 mux from cheatsheet](https://image.slidesharecdn.com/b58d97b8-a22c-4e16-934c-109dc1e1c2ad-161211215133/85/Architect-Cheatsheet-3-320.jpg)