Embed presentation

Download to read offline

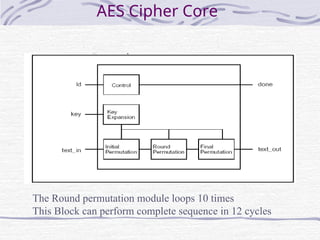

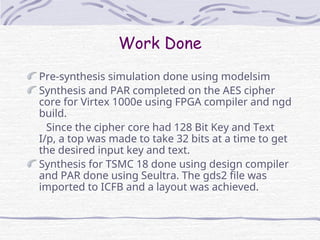

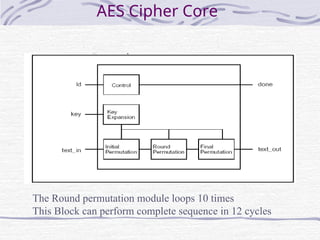

The document discusses the implementation of the Advanced Encryption Standard (AES) using the Rijndael algorithm, detailing its structure, including the AES cipher and inverse cipher core. It highlights the key expansion for a 128-bit key and reports on the synthesis and simulation processes using various tools like ModelSim and FPGA compiler. The document concludes with a mention of layout generation for ASIC using TSMC technology.