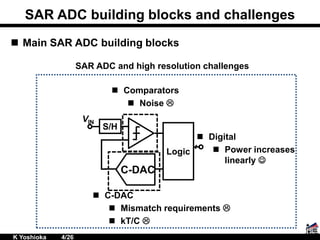

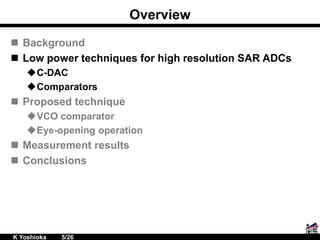

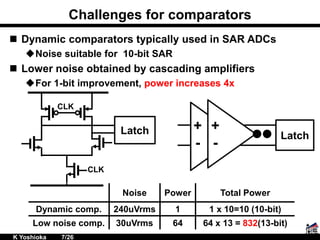

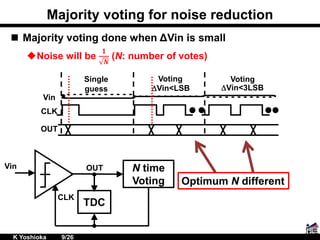

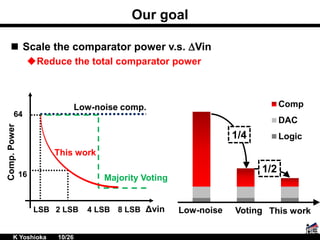

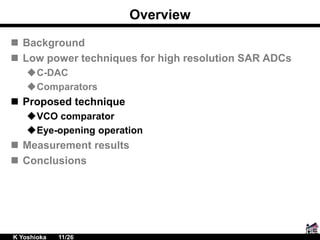

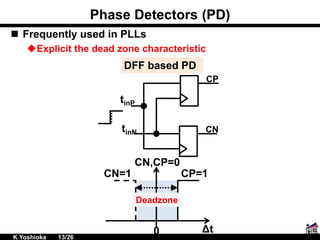

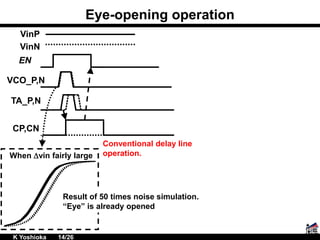

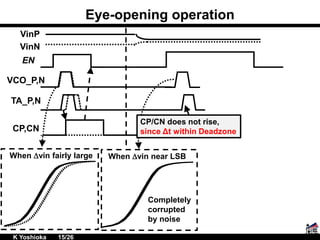

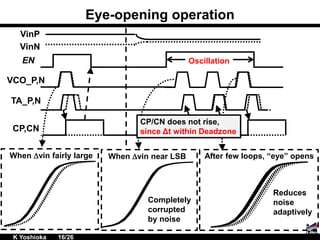

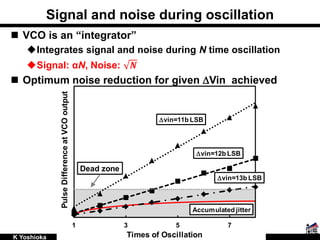

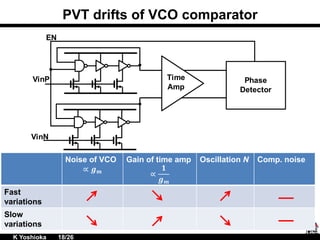

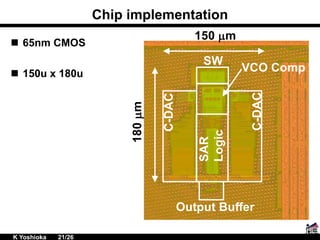

This document presents a low power technique for high resolution SAR ADCs using a VCO comparator with an eye-opening operation. It motivates the need for low power, high resolution ADCs for applications like IoT devices. It then discusses challenges for the main SAR ADC building blocks, particularly the C-DAC and comparators. The proposed technique uses a VCO comparator that automatically scales its noise and power based on the input difference signal, reducing noise when the difference is small through an eye-opening oscillation operation. Measurement results show the implemented 13b SAR ADC achieves 66.4dB SNDR at 45uW power, demonstrating competitive performance compared to prior works.

![Motivation

Low power and high resolution ADCs required

Medical devices

Sensors for “internet of things”

Wearable devices and etc.

Target: SNDR >65dB SAR ADC

0

50

100

150

200

250

2013 2014 2015 2016 2017 2018

IoTMarketinJapan[B$]

http://www.idc.com/

K Yoshioka 3/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-3-320.jpg)

![Low power techniques for C-DAC

Digital calibration to compensate mismatch [1]

Sub-binary radix

Can size C to match kT/C noise

1.8N-1C 1.8C C C

Vin

SAR

Logic

CLK

Transfer Function

With MSB

mismatch

[1] W. Liu, ISSCC 2010

Calibration

Circuit

ADCOUT

K Yoshioka 6/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-6-320.jpg)

![Data driven noise reduction [2]

Event when Δvin < LSB occur only once in SA cycle

Comparator noise requirements relaxed at other cycles

DAC

Dvin 4LSB LSB 3LSB 2LSB

Dvin=|Vinp-Vinn|

[2] P. Harpe, ISSCC 2013

K Yoshioka 8/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-8-320.jpg)

![VCO comparator

Based on time domain comparators [3]

VCO is used instead of a delay line

Time amp[4] amplifies the “time difference” of the pulse

[3] A. Agnes, ISSCC 2008 [4] M. Lee, JSSC 2009.

VinP

VinN

Phase

Detector

EN

Time

Amp

x8

K Yoshioka 12/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-12-320.jpg)

![SAR ADC implementation

SAR ADC based on [1]

13b+2b redundancy

1.8214C 1.82C C

Filtering Cap on 5 MSBs

20C

VCM

C

Perturbation Injection

SAMP

13b+2b C-DAC

SAMPB

VinP

VinN

SAR

Logic

Perturbation Signal

DSAR[14:0]

VCO Comp.

LMS Calibration

Offchip software

DOUT

CLK

C=0.5fF

[1] W. Liu, ISSCC 2010

K Yoshioka 19/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-19-320.jpg)

![FFT spectrum w/peak SNDR

-120

-100

-80

-60

-40

-20

0

0 100 200 300 400 500

Frequency [kHz]

FIN

HD3HD2

fs=1024 kHz

fin=63.625 kHz

SNDR=66.4 dB

SFDR=85.2 dB

After LMS calibrationBefore LMS calibrationFIN

fs=1024 kHz

fin=63.625 kHz

SNDR=48.7 dB

SFDR=61.1 dB

-120

-100

-80

-60

-40

-20

0

0 100 200 300 400 500

Frequency [kHz]

HD3

HD2

Power[dB]

VDD=0.85 V

Vin=0.7 Vpp

VDD=0.85 V

Vin=0.7 Vpp

Only C-DAC calibrated

No tuning is applied to VCO comparator

K Yoshioka 22/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-22-320.jpg)

![Performance and comparison

Liu

ISSCC2010

Harpe

ISSCC2014

Elzakker

ISSCC2008 This work

Technology

[nm]

130 65 65 65

Architecture SAR SAR SAR SAR

fs [MS/s] 45 0.04 1 1

SNDR [dB] 67 62.5 56.2 64.4

Power [uW] 3000 0.097 1.9 45

Calibration Off-chip None None Off-chip

FOM

[fJ/conv.]

36 2.2 4.4 33

FoMS[dB] 165 176 168 164

K Yoshioka 23/26](https://image.slidesharecdn.com/140907presentationyoshiokaup-170814110619/85/A-13b-SAR-ADC-with-Eye-opening-VCO-Based-Comparator-23-320.jpg)