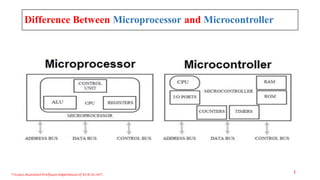

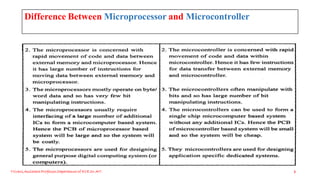

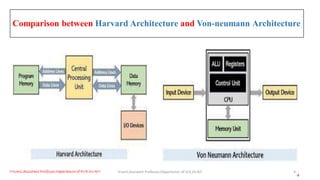

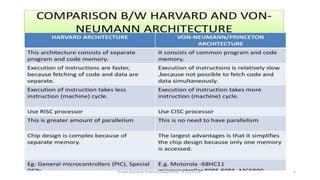

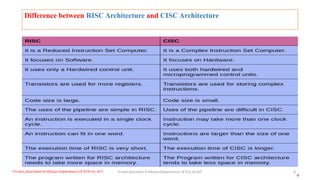

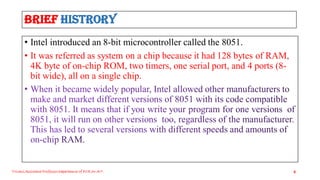

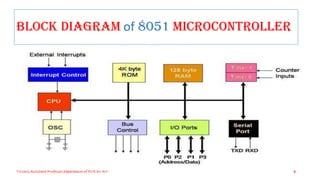

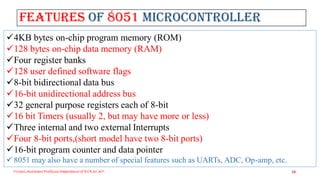

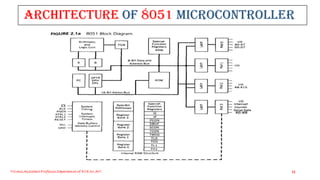

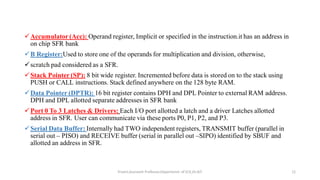

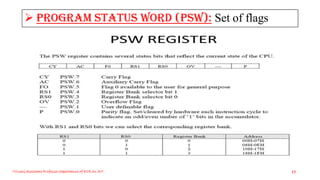

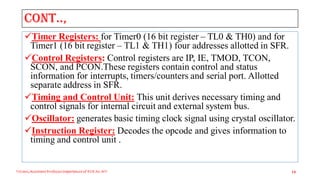

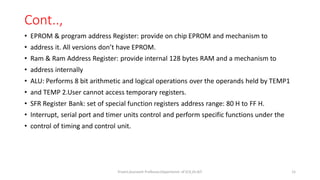

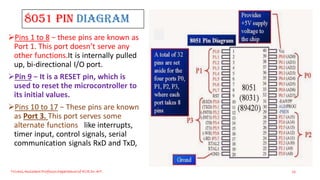

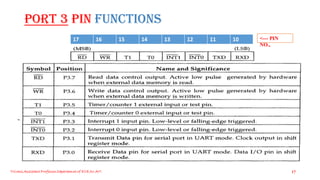

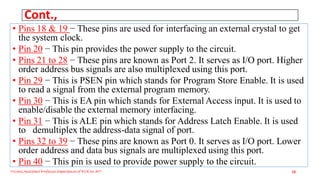

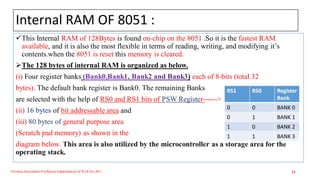

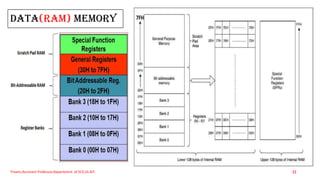

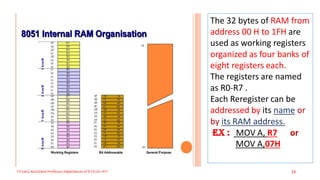

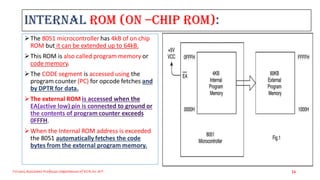

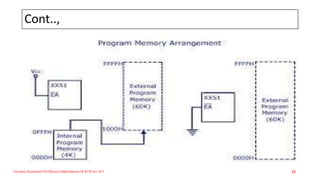

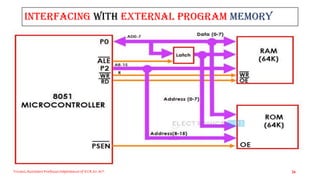

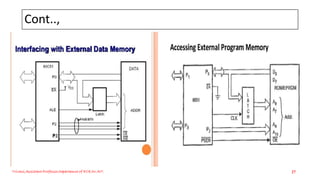

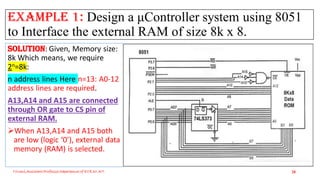

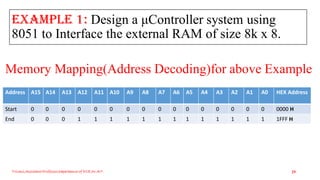

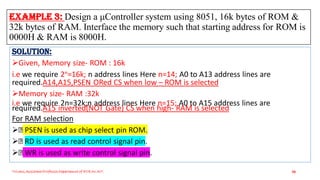

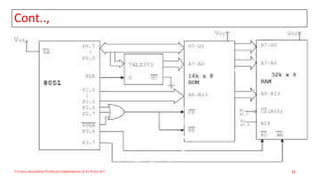

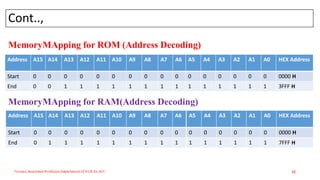

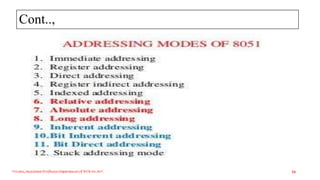

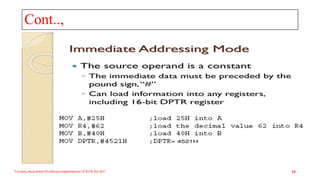

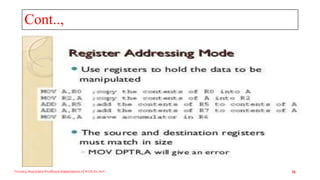

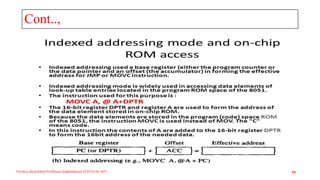

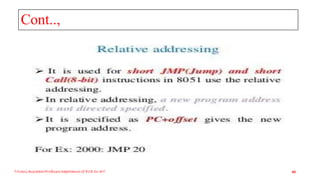

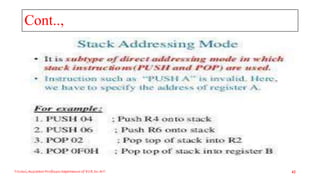

The document discusses the 8051 microcontroller's architecture, features, and its comparison with microprocessors, including the differences between Harvard and Von Neumann architectures. It highlights the internal memory organization, addressing modes, and interfacing options for external RAM and ROM. Additionally, it provides examples of system designs using 8051 for interfacing external memory.