EC8095 VLSI Design Course Outcomes

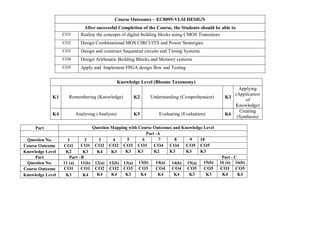

- 1. Course Outcomes – EC8095-VLSI DESIGN After successful Completion of the Course, the Students should be able to CO1 Realize the concepts of digital building blocks using CMOS Transistors CO2 Design Combinational MOS CIRCUITS and Power Stratergies CO3 Design and construct Sequential circuits and Timing Systems CO4 Design Arithmatic Building Blocks and Memory systems CO5 Apply and Implement FPGA design flow and Testing Knowledge Level (Blooms Taxonomy) K1 Remembering (Knowledge) K2 Understanding (Comprehension) K3 Applying (Application of Knowledge) K4 Analysing (Analysis) K5 Evaluating (Evaluation) K6 Creating (Synthesis) Part Question Mapping with Course Outcomes and Knowledge Level Part -A Question No. 1 2 3 4 5 6 7 8 9 10 Course Outcome CO1 CO1 CO2 CO2 CO3 CO3 CO4 CO4 CO5 CO5 Knowledge Level K2 K3 K4 K3 K3 K3 K2 K3 K3 K3 Part Part –B Part - C Question No. 11 (a) 11(b) 12(a) 12(b) 13(a) 13(b) 14(a) 14(b) 15(a) 15(b) 16 (a) 16(b) Course Outcome CO1 CO1 CO2 CO2 CO3 CO3 CO4 CO4 CO5 CO5 CO1 CO5 Knowledge Level K3 K4 K4 K4 K3 K4 K4 K4 K3 K3 K4 K4

- 2. Saveetha Nagar, Thandalam, Chennai – 602105 MODEL EXAM #3 – June 2021 Degree : B.E / Branch : ECE / Semester :VI Sem Date : 10.06.2021/Session :AN/ Duration : 3 hours EC8095/ VLSI DESIGN Time : 4.PM to 7PM Total Marks: 100 PART – A 10X2 = 20 marks 1. Define Logical effort and Electrical effort. 2. A 90 nm long transistor has a gate oxide thickness of 16 𝐴̇. Estimate its gate capacitance per micron of width?(Assume 𝜀𝑟=3.9). 3. Implement a 2 input AND gate using Pass transistor logic. 4. Compare noise margins between Static CMOS and Pseudo NMOS circuits. 5. Define set-up time and hold time of flip flop. 6. Differentiate Latch and Flipflops. 7. What is datapath of the processor? State its functions. 8. What is propagation delay of n-bit ripple carry adder? 9. Define controllability and observability of circuit. 10. Analyze Stuck-at-1 and Stuck-at-0 faults. PART – B 13X5 = 65 marks 11(a) Discuss in detail different types of scaling and their impact on device performance. (or) 11(b) Explain the operation of n-MOS transistor and hence obtain its I-V characteristics. 12(a) (i) Sketch the schematic of Pseudo NMOS gate that implements the function Analyze the advantages and disadvantages of Pseudo –NMOS circuits ( 6 Marks) Implement the function F in (i) using Static CMOS circuit and analyse its advantages over Pseudo NMOS (7 Marks). (or)

- 3. 12(b) Explain in detail implementation of combinational circuits using Pass transistor, Transmission gate and CPL logic families with suitable examples and analyze their performances in terms of power, speed and area 13(a) Write short notes on: (i) Multiplexer-Based Latches (7 Marks) (ii) Low-Voltage Static Latches.(6 Marks) (or) 13(b) Explain in detail the construction and working of Sense amplifier based registers in detail. 14(a) Explain in detail the operation of 16 bit Kogge stone Lookahead Logarithimic adder (or) 14(b) Explain the principle and working of 6T CMOS SRAM cell Read and Write operations. 15 (a) (i) Explain the general architecture of Xilinx FPGA ( 4 Marks) (ii)Explain in detail the architecture of Xilinx XC2000 and Xilinx XC3000 FPGA.s (9 Marks) (or) 15 (b) (i)Explain in detail the routing procedure in Actel ACT1 FPGA ( 6 Marks ) (ii) Explain in detail the routing procedure in Xilinx XC4000 FPGA ( 7 Marks ) PART – C 15X1 = 15 marks 16 (a) (i) Realize a 4 bit Array multiplier and hence analyse its operation.(7) (ii) Construct analyze and obtain propagation delay of a 4 bit Carry Save multiplier.(8) (or) 16 (b) (i)Realize the schematic and working of a master slave negative edge triggered register that is insensitive to Clock skew.(5Marks) (ii)Discuss how the negative edge triggered register is skew insensitive during 0-0 overlap and 1-1 overlap with neat diagrams(6 Marks) (iii) Explain the operation of True Single-Phase Clocked Register (TSPCR) ( 4)