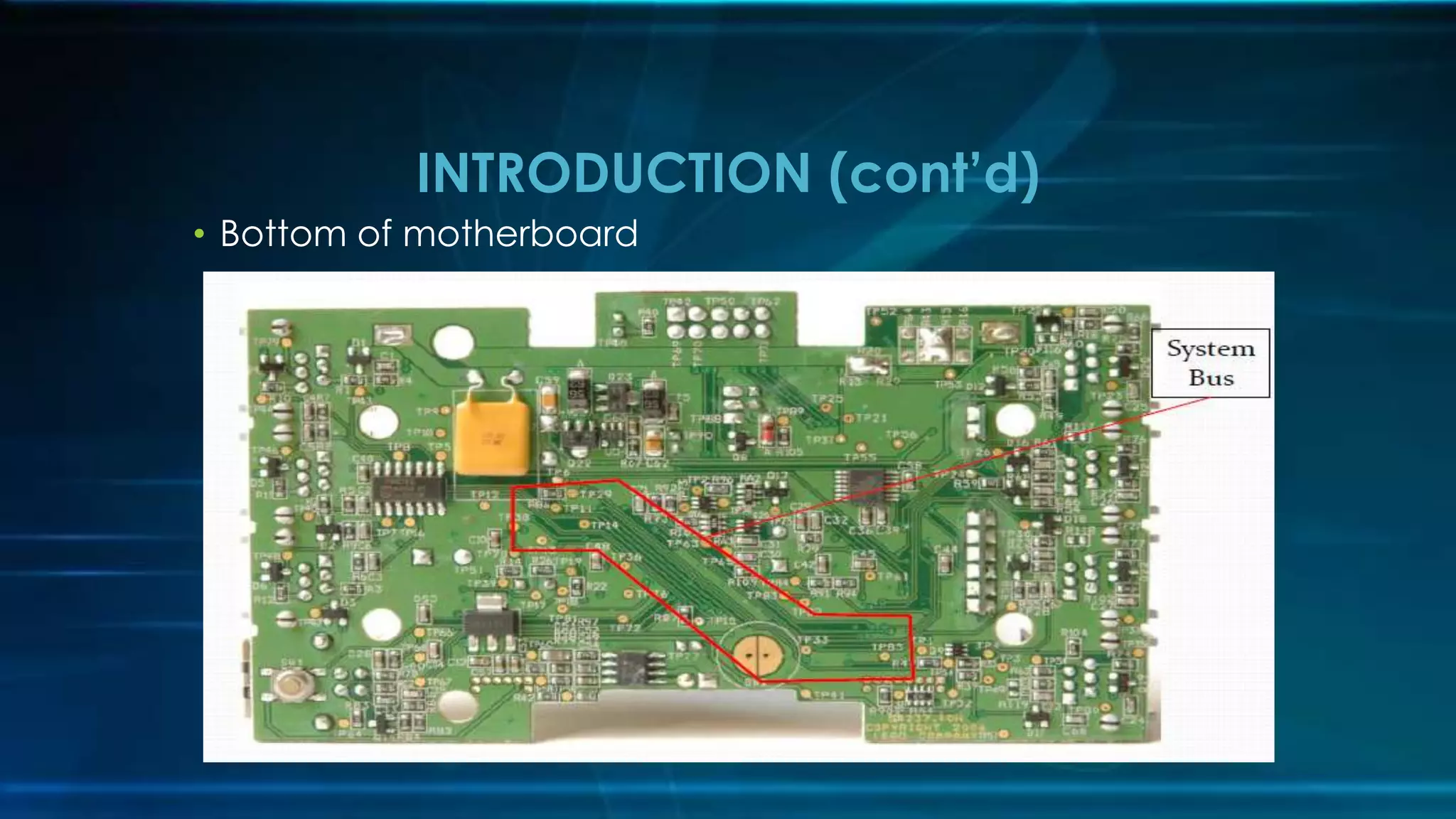

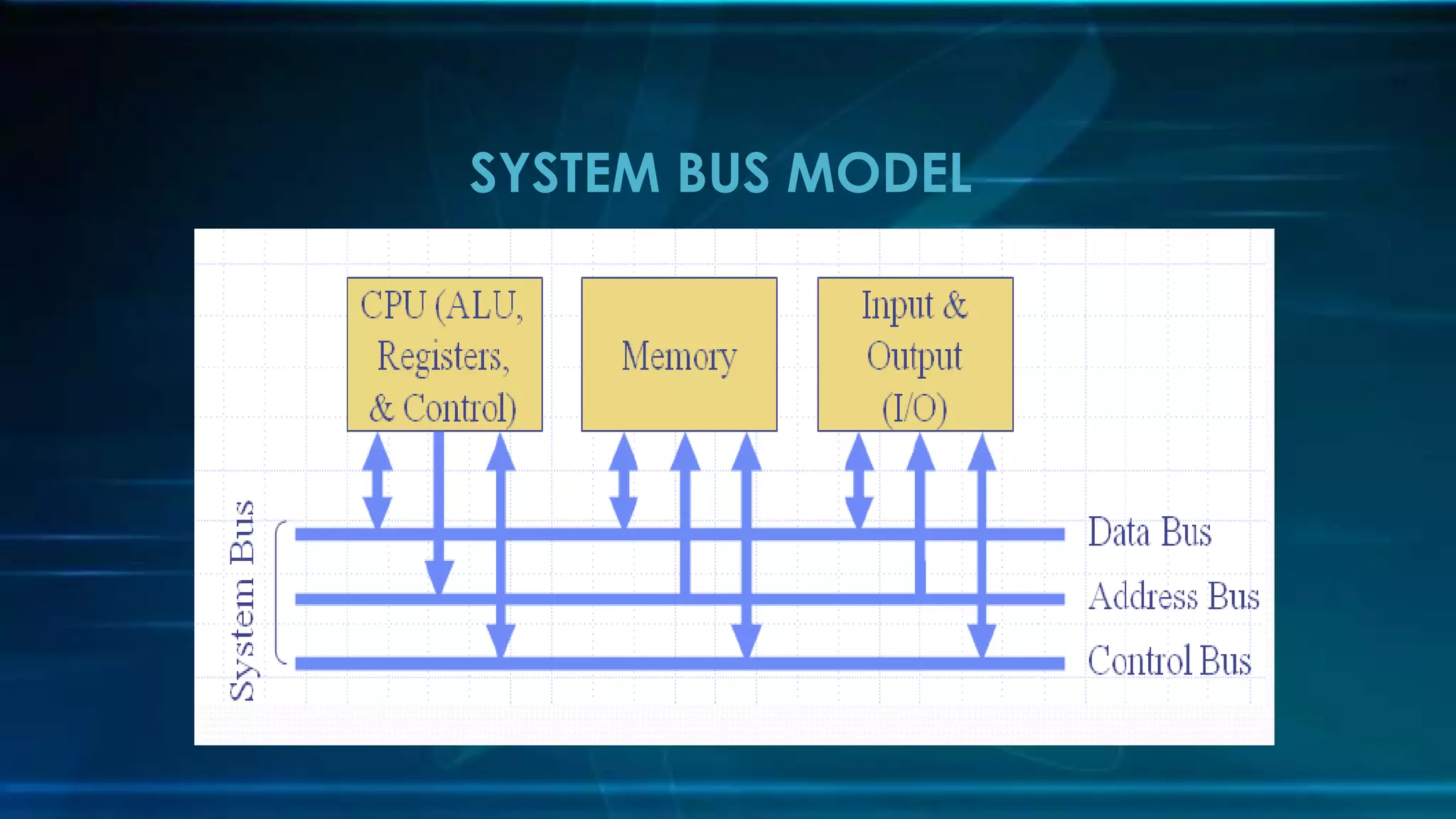

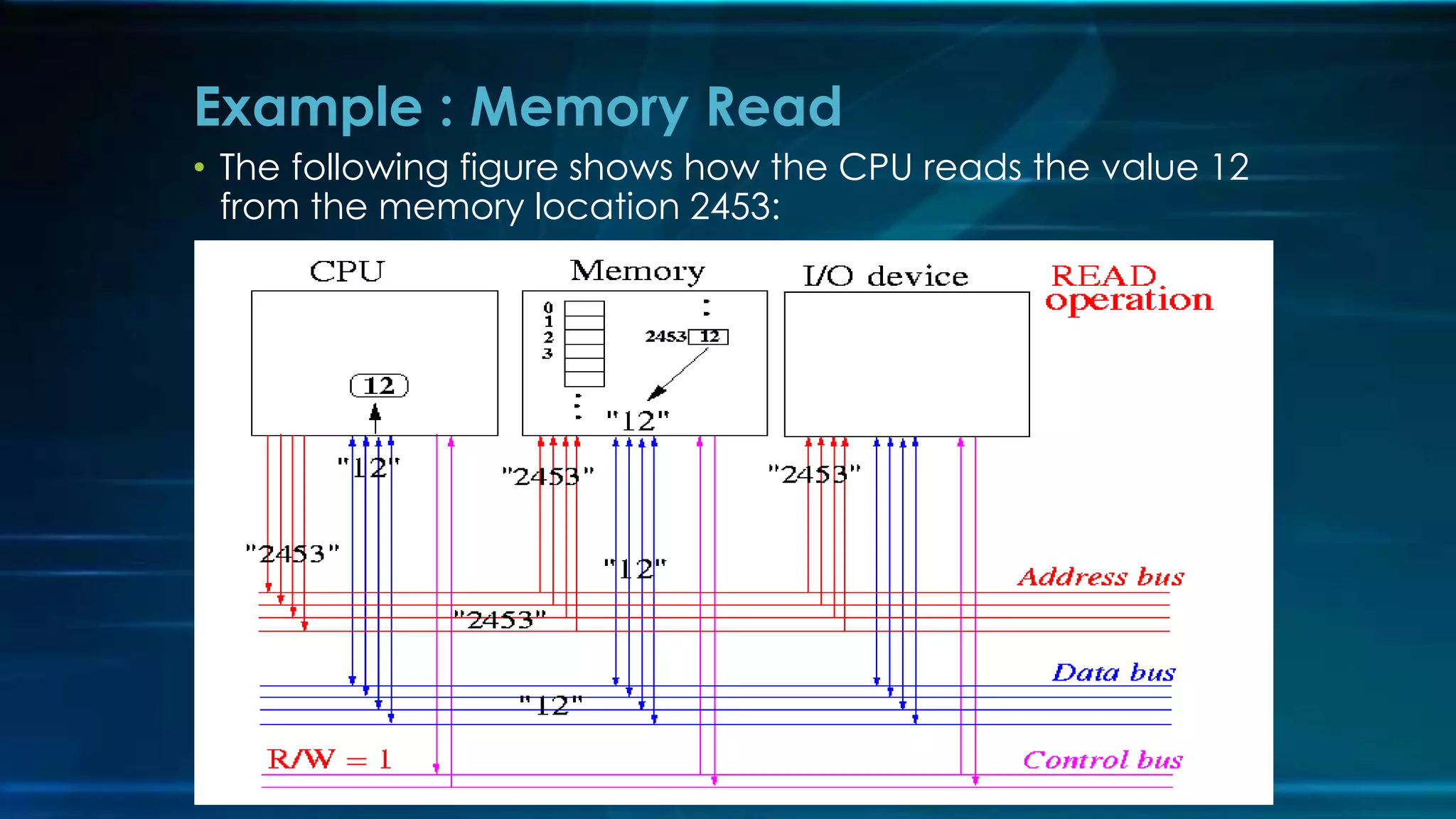

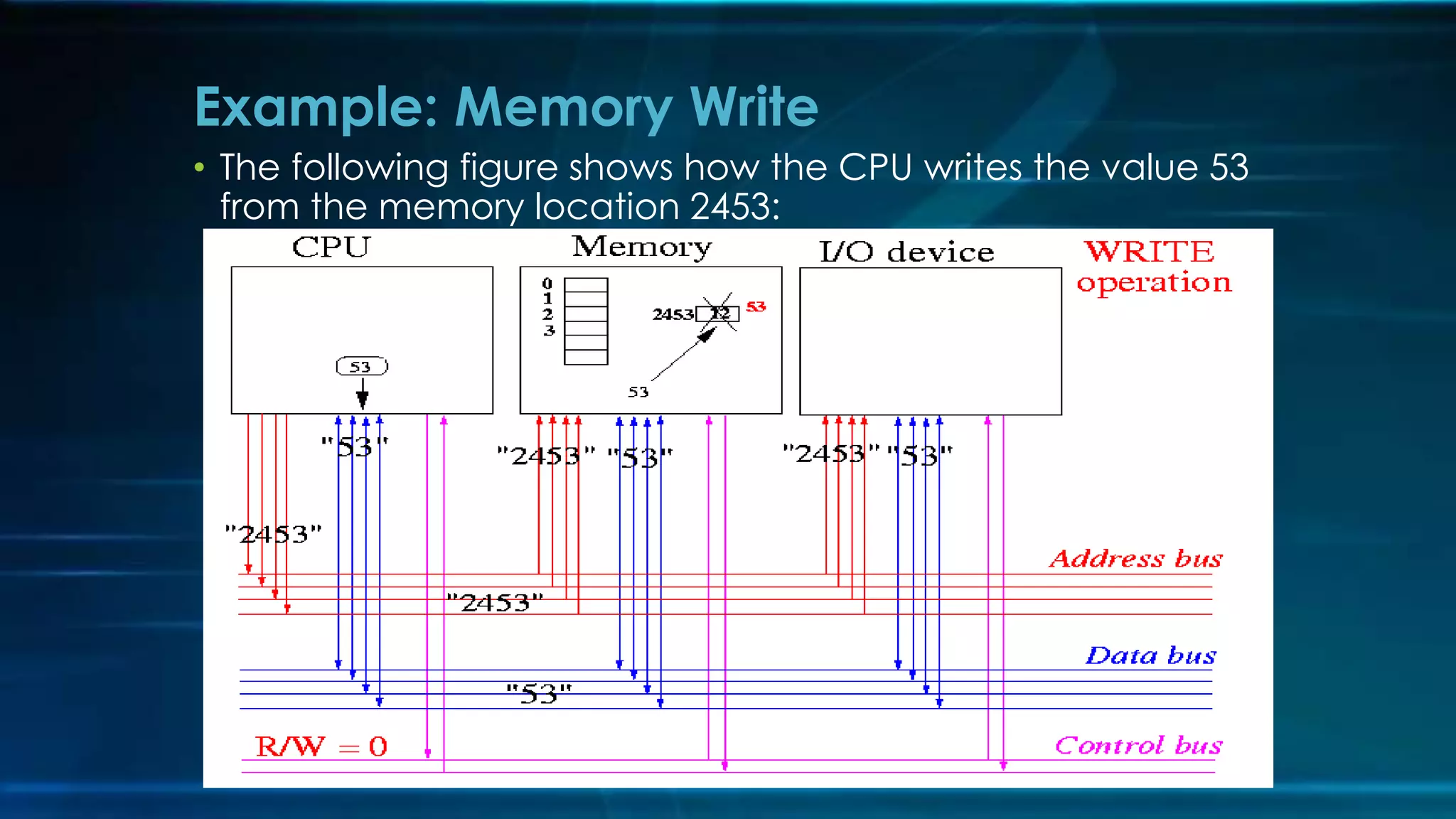

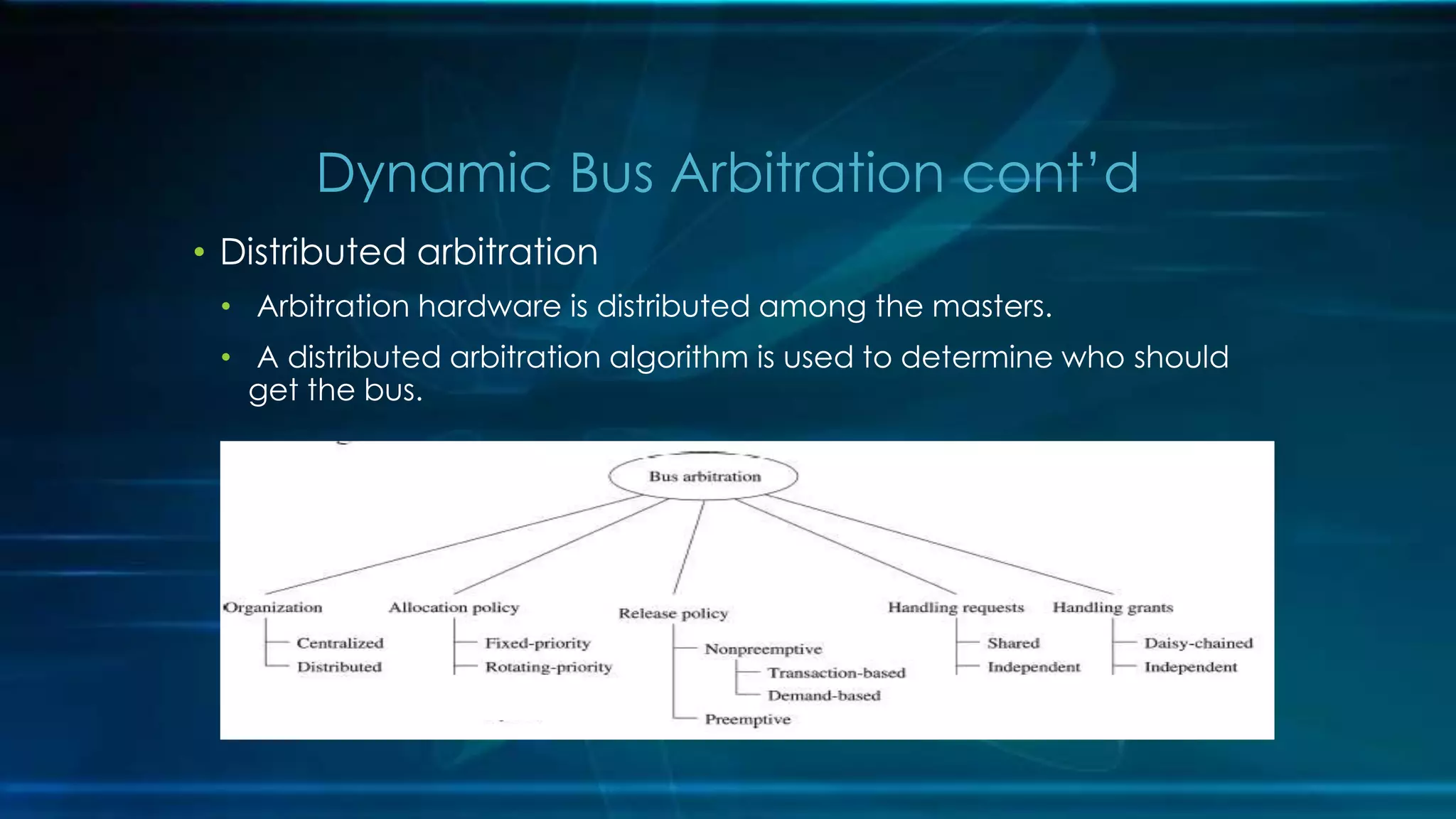

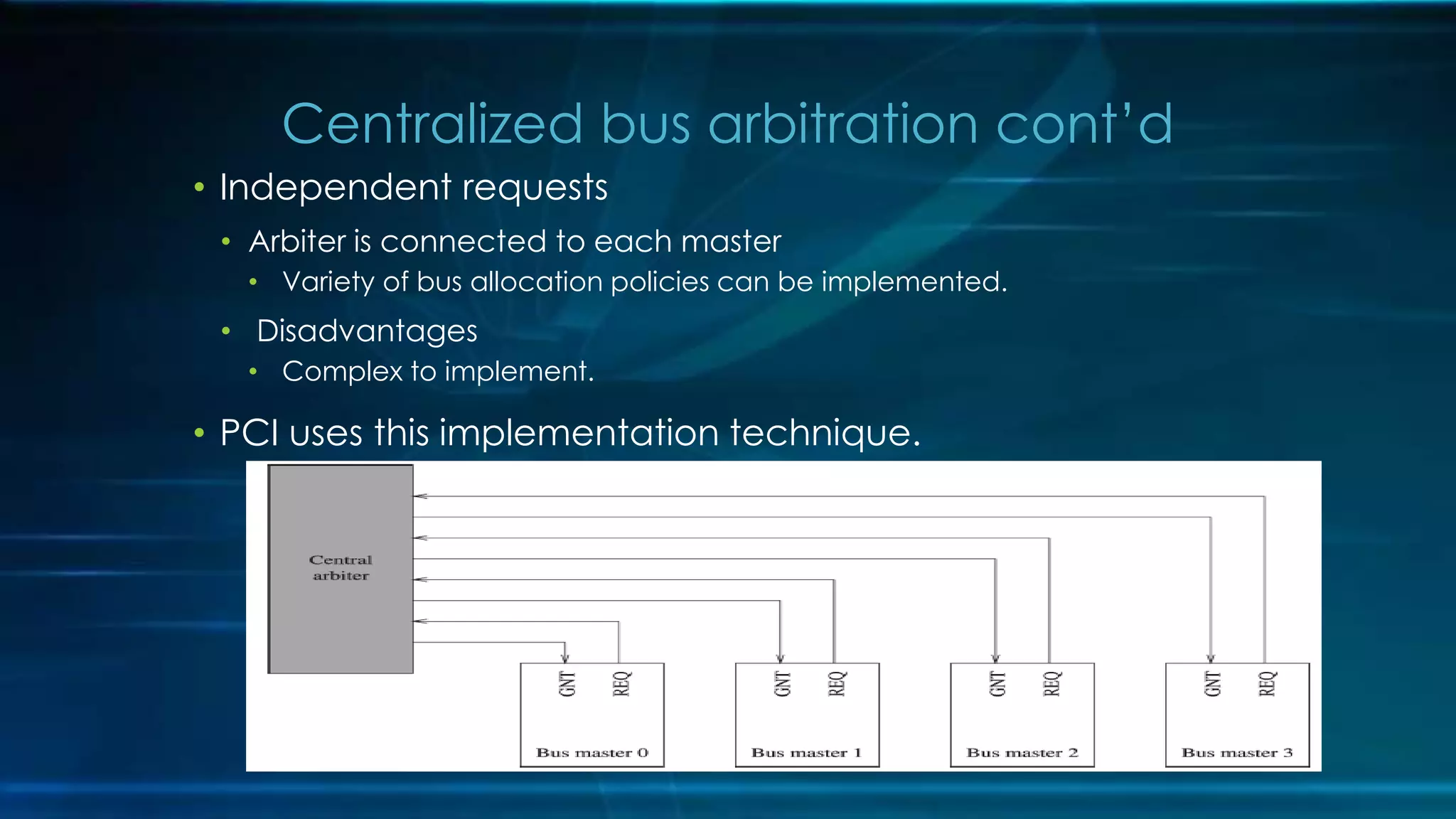

The system bus connects the central components of a computer system, including the CPU, memory, and input/output devices. It consists of three main buses - the data bus, which transfers data; the address bus, which specifies memory locations; and the control bus, which coordinates signals. The buses allow components to communicate by transferring data and commands in parallel via electrical pathways on the motherboard. Arbitration determines which device gains control of the shared bus at any given time to prevent signals from overlapping.