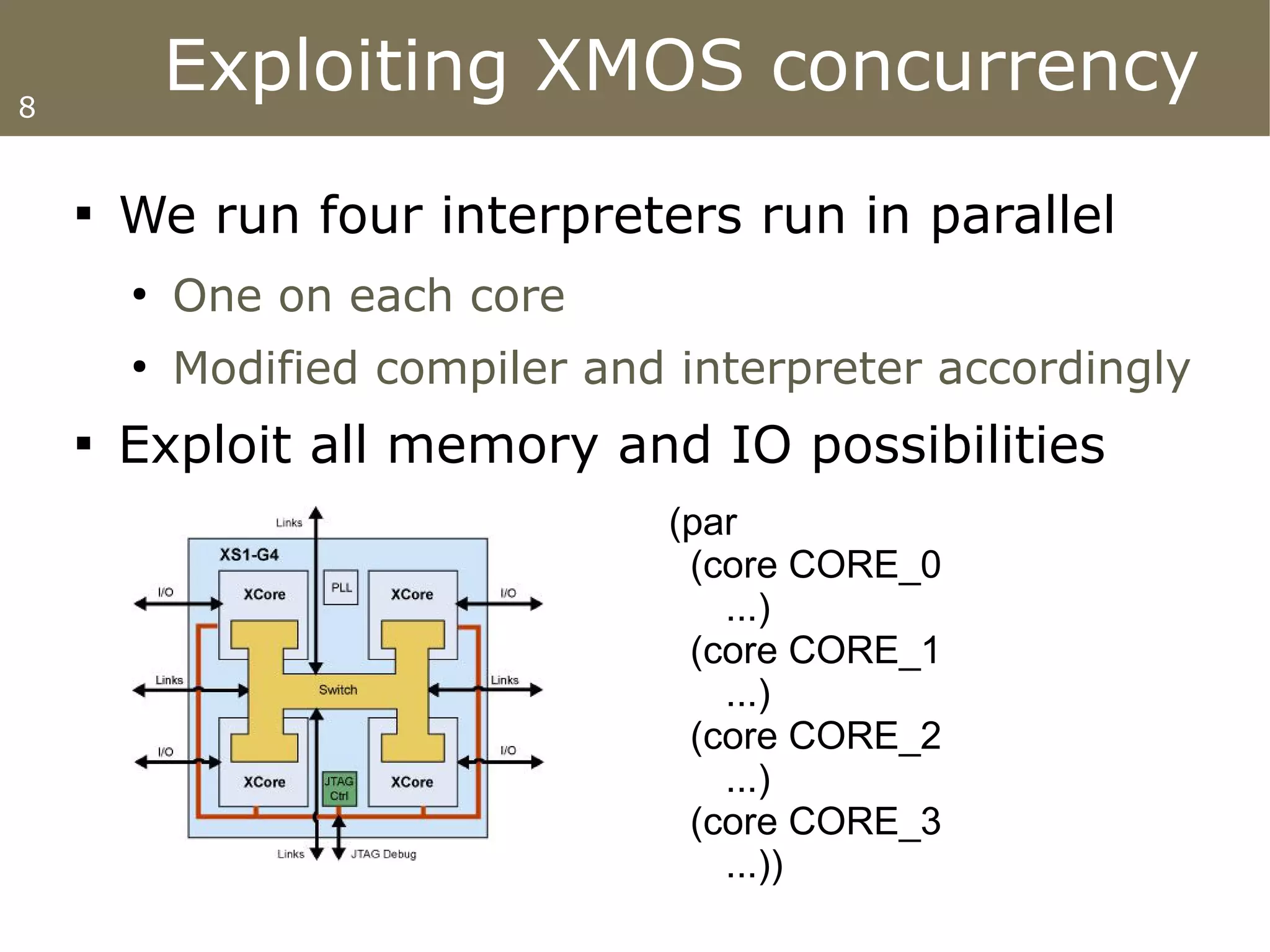

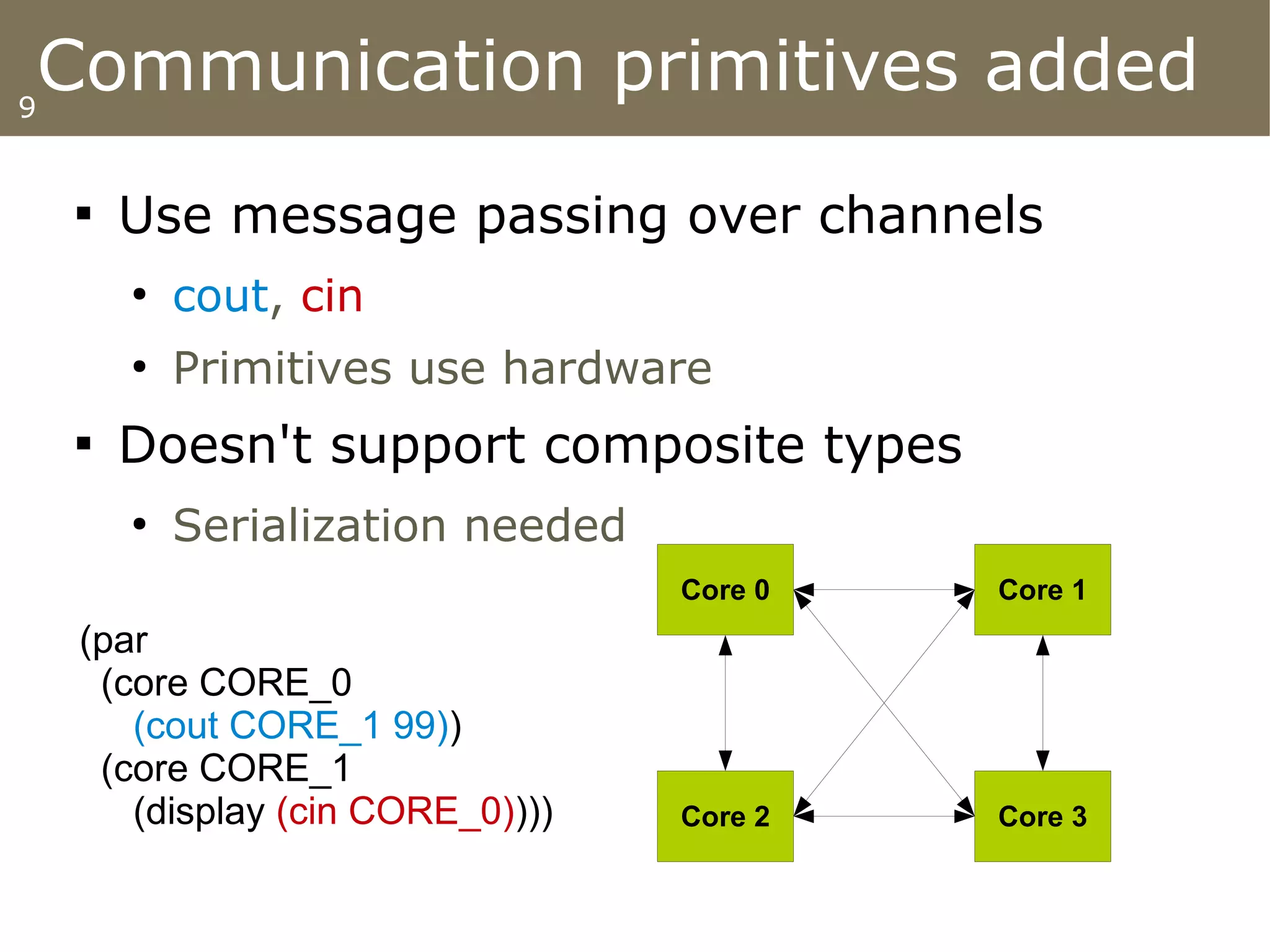

This document discusses implementing concurrency abstractions for programming multi-core embedded systems in Scheme. It describes modifying the Bit Scheme interpreter to support the event-driven XMOS chip. New primitives were added for message passing, I/O, and time to exploit the chip's concurrency. The modified interpreter and compiler allow hardware to be programmed from Scheme and were demonstrated with an LED pulse width modulation application.