Application of gates

•Download as DOCX, PDF•

1 like•1,734 views

Application of gates

Report

Share

Report

Share

Recommended

Performance evaluation of SEPIC, Luo and ZETA converter

Performance evaluation of SEPIC, Luo and ZETA converterInternational Journal of Power Electronics and Drive Systems

More Related Content

What's hot

Performance evaluation of SEPIC, Luo and ZETA converter

Performance evaluation of SEPIC, Luo and ZETA converterInternational Journal of Power Electronics and Drive Systems

What's hot (20)

Bipolar junction transistors working principle and applications

Bipolar junction transistors working principle and applications

Space Vector Pulse Width Modulation Technique Applied to Two Level Voltage So...

Space Vector Pulse Width Modulation Technique Applied to Two Level Voltage So...

Performance evaluation of SEPIC, Luo and ZETA converter

Performance evaluation of SEPIC, Luo and ZETA converter

Viewers also liked

Application of Stack, Link list , and Queue in Programming .

Application of Stack, Link list , and Queue in Programming .Mechanical Engineering at COMSATS Sahiwal

jet engine, working, uses, typesNew microsoft office word document

jet engine, working, uses, typesNew microsoft office word documentMechanical Engineering at COMSATS Sahiwal

Viewers also liked (11)

Application of Stack, Link list , and Queue in Programming .

Application of Stack, Link list , and Queue in Programming .

Advantage & disadvantages of four types of thermometry.

Advantage & disadvantages of four types of thermometry.

jet engine, working, uses, typesNew microsoft office word document

jet engine, working, uses, typesNew microsoft office word document

Similar to Application of gates

Similar to Application of gates (20)

A 20 gbs injection locked clock and data recovery circuit

A 20 gbs injection locked clock and data recovery circuit

Three Phase Digitally Controlled Power Factor Improvement System

Three Phase Digitally Controlled Power Factor Improvement System

IRJET- Design and Implementation of Three Phase Grid Simulator

IRJET- Design and Implementation of Three Phase Grid Simulator

MITIGATION OF SOFT ERRORS ON 65NM COMBINATIONAL LOGIC GATES VIA BUFFER GATE

MITIGATION OF SOFT ERRORS ON 65NM COMBINATIONAL LOGIC GATES VIA BUFFER GATE

Design and Implementation of Schmitt Trigger using Operational Amplifier

Design and Implementation of Schmitt Trigger using Operational Amplifier

International Refereed Journal of Engineering and Science (IRJES)

International Refereed Journal of Engineering and Science (IRJES)

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

Cro cathode ray oscilloscope working and applications

Cro cathode ray oscilloscope working and applications

Recently uploaded

Call Girls Service Nagpur Tanvi Call 7001035870 Meet With Nagpur Escorts

Call Girls Service Nagpur Tanvi Call 7001035870 Meet With Nagpur EscortsCall Girls in Nagpur High Profile

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur EscortsCall Girls in Nagpur High Profile

Recently uploaded (20)

(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...![(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...

Model Call Girl in Narela Delhi reach out to us at 🔝8264348440🔝

Model Call Girl in Narela Delhi reach out to us at 🔝8264348440🔝

(ANJALI) Dange Chowk Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...![(ANJALI) Dange Chowk Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![(ANJALI) Dange Chowk Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

(ANJALI) Dange Chowk Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...

Introduction to IEEE STANDARDS and its different types.pptx

Introduction to IEEE STANDARDS and its different types.pptx

Call Girls Delhi {Jodhpur} 9711199012 high profile service

Call Girls Delhi {Jodhpur} 9711199012 high profile service

247267395-1-Symmetric-and-distributed-shared-memory-architectures-ppt (1).ppt

247267395-1-Symmetric-and-distributed-shared-memory-architectures-ppt (1).ppt

Sheet Pile Wall Design and Construction: A Practical Guide for Civil Engineer...

Sheet Pile Wall Design and Construction: A Practical Guide for Civil Engineer...

VIP Call Girls Service Hitech City Hyderabad Call +91-8250192130

VIP Call Girls Service Hitech City Hyderabad Call +91-8250192130

Biology for Computer Engineers Course Handout.pptx

Biology for Computer Engineers Course Handout.pptx

Call Girls Service Nagpur Tanvi Call 7001035870 Meet With Nagpur Escorts

Call Girls Service Nagpur Tanvi Call 7001035870 Meet With Nagpur Escorts

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

Coefficient of Thermal Expansion and their Importance.pptx

Coefficient of Thermal Expansion and their Importance.pptx

VIP Call Girls Service Kondapur Hyderabad Call +91-8250192130

VIP Call Girls Service Kondapur Hyderabad Call +91-8250192130

Application of gates

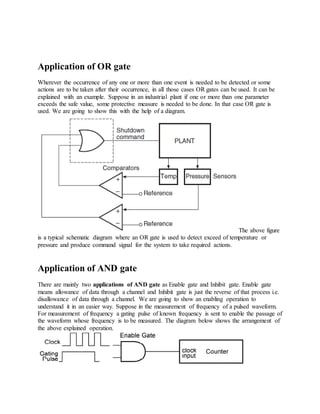

- 1. Application of OR gate Wherever the occurrence of any one or more than one event is needed to be detected or some actions are to be taken after their occurrence, in all those cases OR gates can be used. It can be explained with an example. Suppose in an industrial plant if one or more than one parameter exceeds the safe value, some protective measure is needed to be done. In that case OR gate is used. We are going to show this with the help of a diagram. The above figure is a typical schematic diagram where an OR gate is used to detect exceed of temperature or pressure and produce command signal for the system to take required actions. Application of AND gate There are mainly two applications of AND gate as Enable gate and Inhibit gate. Enable gate means allowance of data through a channel and Inhibit gate is just the reverse of that process i.e. disallowance of data through a channel. We are going to show an enabling operation to understand it in an easier way. Suppose in the measurement of frequency of a pulsed waveform. For measurement of frequency a gating pulse of known frequency is sent to enable the passage of the waveform whose frequency is to be measured. The diagram below shows the arrangement of the above explained operation.

- 2. Application of Ex-OR/Ex-NOR gate These type of logic gates are used in generation of parity generation and checking units. The two diagrams below shows the even and odd parity generator circuits respectively for a four data. With the help of these gates parity check operation can be also performed. The diagrams below show even and odd parity check. Figure (a) shows the parity check using Ex-OR gates and the figure (b) shows the parity check using Ex- NOR gates. Application of NOT gate or Inverters

- 3. NOT gates are also known as inverter because they invert the output given to them and show the reverse result. Now the CMOS inverters are commonly used to build square wave oscillators which are used for generating clock signals. The advantage of using these is they consume low power and their interfacing is very easy compared to other logic gates. The above figure shows the most fundamental circuit made of ring configuration to generate square wave oscillator. The frequency of this type generator is given by Where n represents the number of inverters and tp shows the propagation delay per gate.