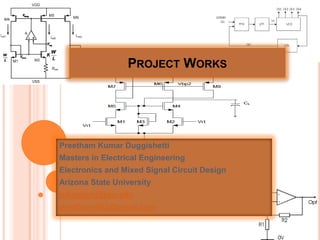

ASU Electrical Engineering Masters Project Works by Preetham Kumar Duggishetti

•Download as PPTX, PDF•

0 likes•278 views

The document outlines Preetham Kumar Duggishetti's Masters projects in electrical engineering focusing on circuit design, including projects developing a Phase Locked Loop at 1.6GHz, a low power 32-bit ALU, an oversampling Sigma Delta ADC for WLAN systems, and more. The projects involved designing circuits in Cadence and developing behavioral models in VerilogA and MATLAB to meet various power, speed, and dynamic range requirements. Preetham's work demonstrates expertise in analog and mixed-signal circuit design.

Report

Share

Report

Share

Recommended

PARASITICS REDUCTION FOR RFIC CMOS LAYOUT AND IIP3 VS Q-BASED DESIGN ANALYSI...

PARASITICS REDUCTION FOR RFIC CMOS LAYOUT AND IIP3 VS Q-BASED DESIGN ANALYSI...Ilango Jeyasubramanian

PARASITIC-AWARE FULL PHYSICAL CHIP DESIGN OF LNA RFIC AT 2.45GHZ USING IBM 13...

PARASITIC-AWARE FULL PHYSICAL CHIP DESIGN OF LNA RFIC AT 2.45GHZ USING IBM 13...Ilango Jeyasubramanian

Recommended

PARASITICS REDUCTION FOR RFIC CMOS LAYOUT AND IIP3 VS Q-BASED DESIGN ANALYSI...

PARASITICS REDUCTION FOR RFIC CMOS LAYOUT AND IIP3 VS Q-BASED DESIGN ANALYSI...Ilango Jeyasubramanian

PARASITIC-AWARE FULL PHYSICAL CHIP DESIGN OF LNA RFIC AT 2.45GHZ USING IBM 13...

PARASITIC-AWARE FULL PHYSICAL CHIP DESIGN OF LNA RFIC AT 2.45GHZ USING IBM 13...Ilango Jeyasubramanian

Cmos VLSI Design By umakant bhaskar gohatre

Cmos VLSI Design By umakant bhaskar gohatreSmt. Indira Gandhi College of Engineering, Navi Mumbai, Mumbai

More Related Content

What's hot

Cmos VLSI Design By umakant bhaskar gohatre

Cmos VLSI Design By umakant bhaskar gohatreSmt. Indira Gandhi College of Engineering, Navi Mumbai, Mumbai

What's hot (20)

A fast acquisition all-digital delay-locked loop using a starting-bit predict...

A fast acquisition all-digital delay-locked loop using a starting-bit predict...

Low power and area-efficient shift register using pulsed latches

Low power and area-efficient shift register using pulsed latches

Original N-channel MOSFET MMF70R900P 70R900P 70R900 750V 5A TO-220 New MagnaC...

Original N-channel MOSFET MMF70R900P 70R900P 70R900 750V 5A TO-220 New MagnaC...

ACCURATE Q-PREDICTION FOR RFIC SPIRAL INDUCTORS USING THE 3DB BANDWIDTH

ACCURATE Q-PREDICTION FOR RFIC SPIRAL INDUCTORS USING THE 3DB BANDWIDTH

Original PNP Transistor KTA200-Y-AT A200 TO-92 New KEC

Original PNP Transistor KTA200-Y-AT A200 TO-92 New KEC

RF Module Design - [Chapter 5] Low Noise Amplifier![RF Module Design - [Chapter 5] Low Noise Amplifier](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![RF Module Design - [Chapter 5] Low Noise Amplifier](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

RF Module Design - [Chapter 5] Low Noise Amplifier

ECE 17 Final Presentation Portable Ultrasound Driver

ECE 17 Final Presentation Portable Ultrasound Driver

Similar to ASU Electrical Engineering Masters Project Works by Preetham Kumar Duggishetti

Similar to ASU Electrical Engineering Masters Project Works by Preetham Kumar Duggishetti (20)

Efficient signal acquisition in multi channel neural systems

Efficient signal acquisition in multi channel neural systems

Implementing AI: Hardware Challenges: Heterogeneous and Adaptive Computing fo...

Implementing AI: Hardware Challenges: Heterogeneous and Adaptive Computing fo...

A low cost low-power ring oscillator-based truly random number generator for ...

A low cost low-power ring oscillator-based truly random number generator for ...

4---glynn-and-devlin---an-x-band-gan-pa-mmic-for-p.pdf

4---glynn-and-devlin---an-x-band-gan-pa-mmic-for-p.pdf

Performance Analysis of Encoder in Different Logic Techniques for High-Speed ...

Performance Analysis of Encoder in Different Logic Techniques for High-Speed ...

CMOS Analog IC design by Dr GS Javed - Refresher Course - Batch 1

CMOS Analog IC design by Dr GS Javed - Refresher Course - Batch 1

Challenges of Parallel Simulation of Power Systems_english

Challenges of Parallel Simulation of Power Systems_english

IEEE CASE 2011, Italy - Conference Paper Presentation

IEEE CASE 2011, Italy - Conference Paper Presentation

Development of a Single Stage C-Band Pulsed Power Amplifier for RADAR Transmi...

Development of a Single Stage C-Band Pulsed Power Amplifier for RADAR Transmi...

ASU Electrical Engineering Masters Project Works by Preetham Kumar Duggishetti

- 1. Project Works Preetham Kumar Duggishetti Masters in Electrical Engineering Electronics and Mixed Signal Circuit Design Arizona State University pduggish@asu.edu preetham463@gmail.com

- 3. Cadence (Spectre ) , VerilogA, MATLAB.

- 4. Generated 4 equally spaced clocks at 1.6GHz with CMOS full-swing (1.8V), achieved 300ns lock time for 1.6GHz oscillation.

- 7. Requirement : Power consumption to be least with a delay constraint of 10 nS, output transition time lower than 200pS with a load of 30 fF at the -10%Vdd and Slow-Slow Design corner.

- 8. Understood various design techniques for Low Power and procedures to choose the right logic style.

- 10. Cadence (Spectre ) , MATLAB/SIMULINK, VerilogA .

- 13. Dc gain > 50dB, Ft = 70MHz with CL = 1pF, Tail current source < 110uA.

- 15. Cadence (Spectre ) .

- 16. Understood IC biasing circuits and their variations with supply and temperature.

- 18. Cadence (Spectre , Virtuso Layout Editor )

- 19. High gain, UGF of 25 MHz with 15pF capacitive load, input referred noise of 10nV/sqHz, Quiescent Power dissipation of 1.2mW, Slew rate of 10V/usec with 5pF cap load, PSRR and CMRR of 55dB at 10 KHz and Phase margin of 60 degrees with 5pF capacitive load.

- 21. Matlab/Simulink tools were used and a resolution of 14 bit and 12 bit respectively were achieved.