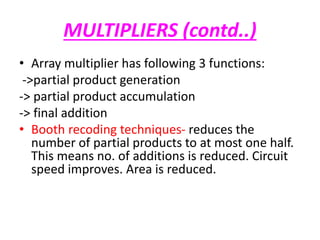

Adder circuits are fundamental building blocks in processors. The ripple carry adder is the simplest implementation but has increasing delay as the number of bits increases due to carry propagation. Faster adders like carry lookahead and carry select optimize the carry logic to reduce delay. Multipliers perform multiplication through generating and accumulating partial products using adders. Techniques like Booth recoding can reduce the number of partial products and additions to improve speed and reduce area of multiplier circuits.