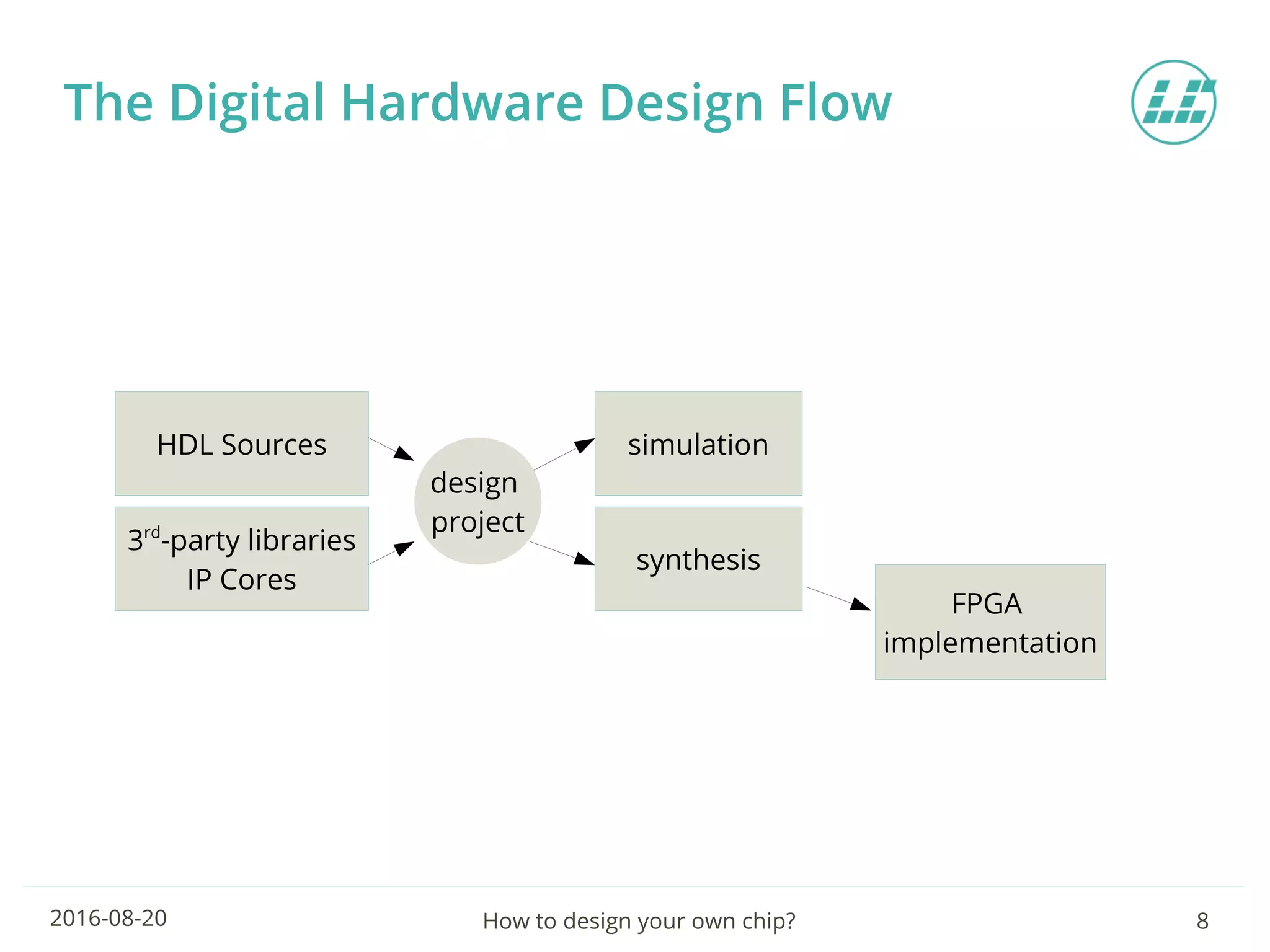

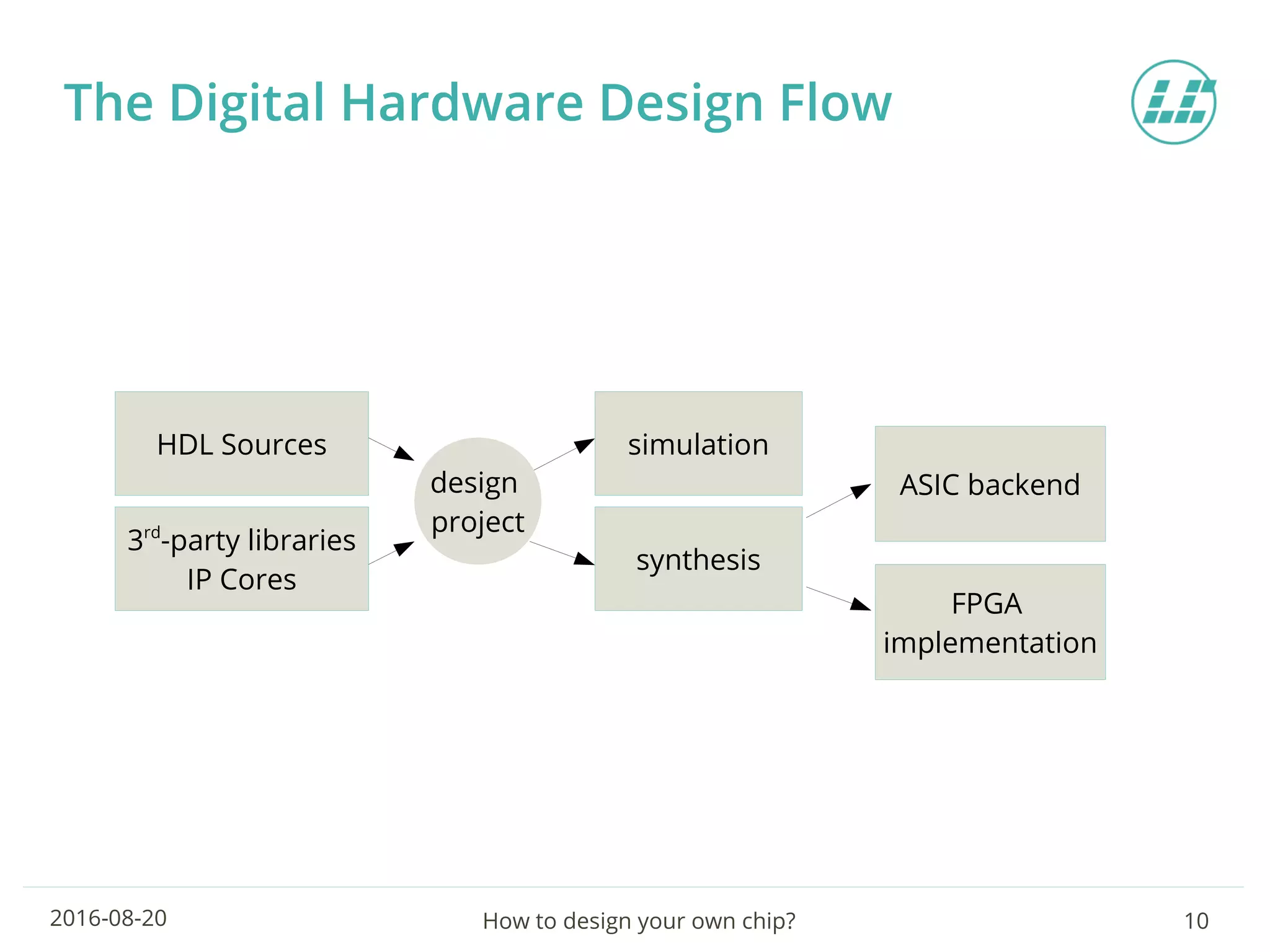

This document provides a comprehensive guide on designing a chip, covering various methodologies for simulation, FPGA, and ASIC design while highlighting the differences between free and open-source hardware options. It discusses essential tools and resources necessary for chip design, such as different hardware description languages, simulators, and licensing options. Additionally, it emphasizes community involvement through platforms like LibreCores for collaboration and resource sharing in digital hardware design.

![How to design your own chip? 302016-08-20

Got Money?

[[user:]]viaWikimediaCommons,CCBY-SA](https://image.slidesharecdn.com/20160820-froscon-fossi-160820135544/75/How-to-design-your-own-chip-30-2048.jpg)