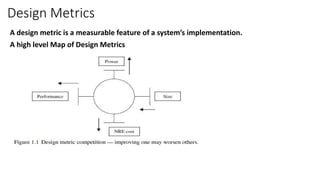

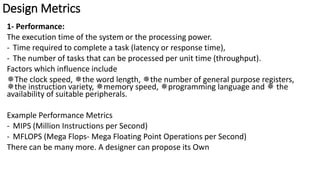

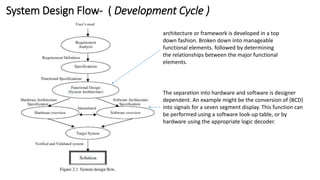

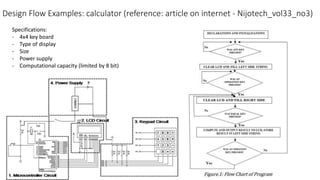

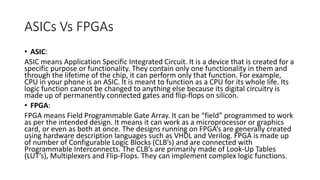

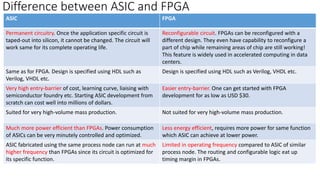

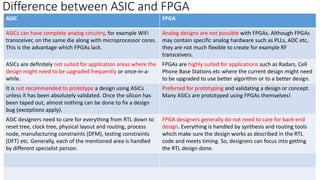

This document outlines the fundamental concepts of digital system design, including types of implementations such as processor-based, microcontroller, and FPGA systems. It discusses the analysis and design processes, design metrics such as performance and power efficiency, and the comparison between ASICs and FPGAs, highlighting their respective use cases, advantages, and entry barriers. Additionally, it provides insights into design flows for both ASIC and FPGA, emphasizing the importance of design tools and methodologies.