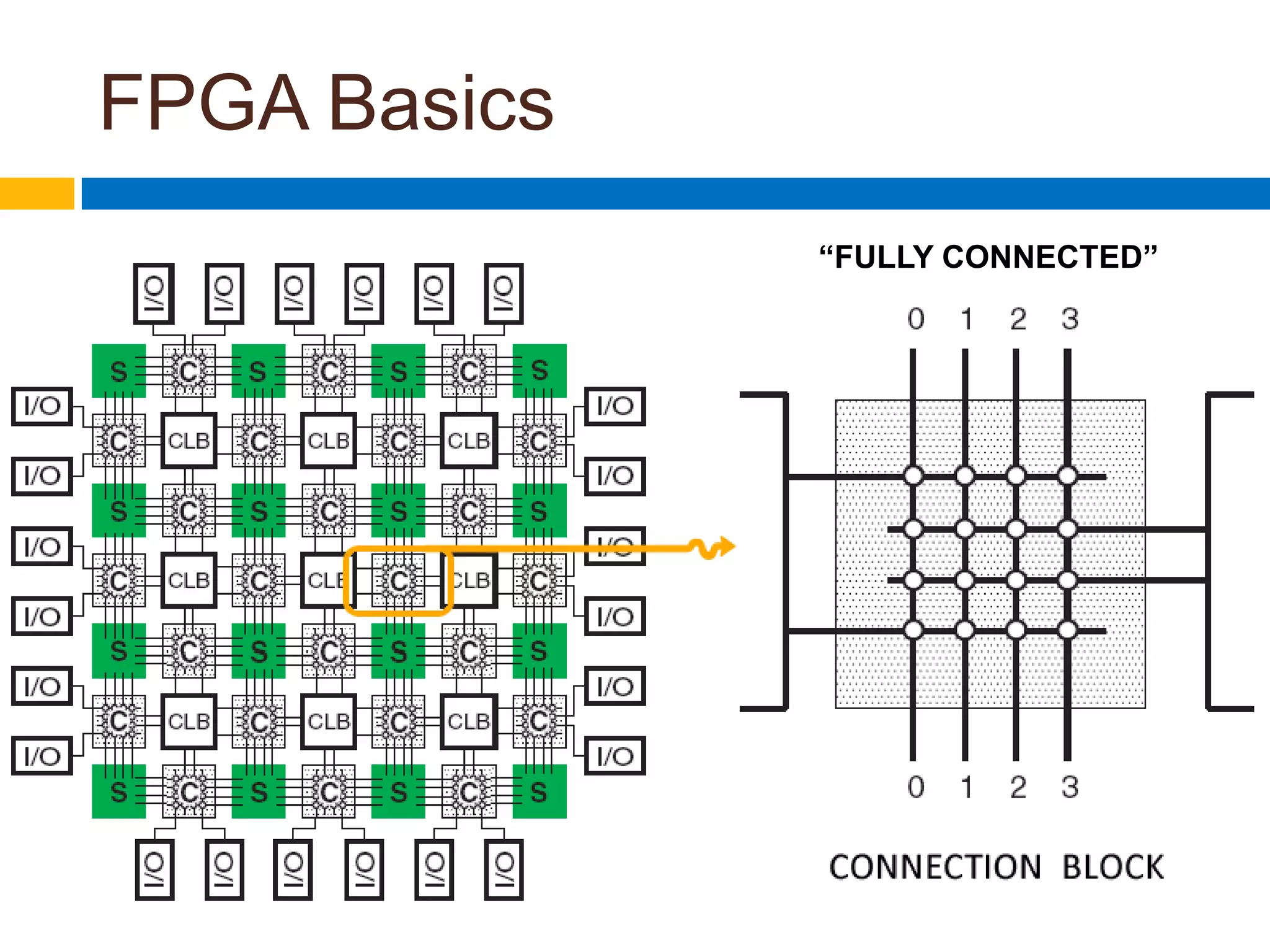

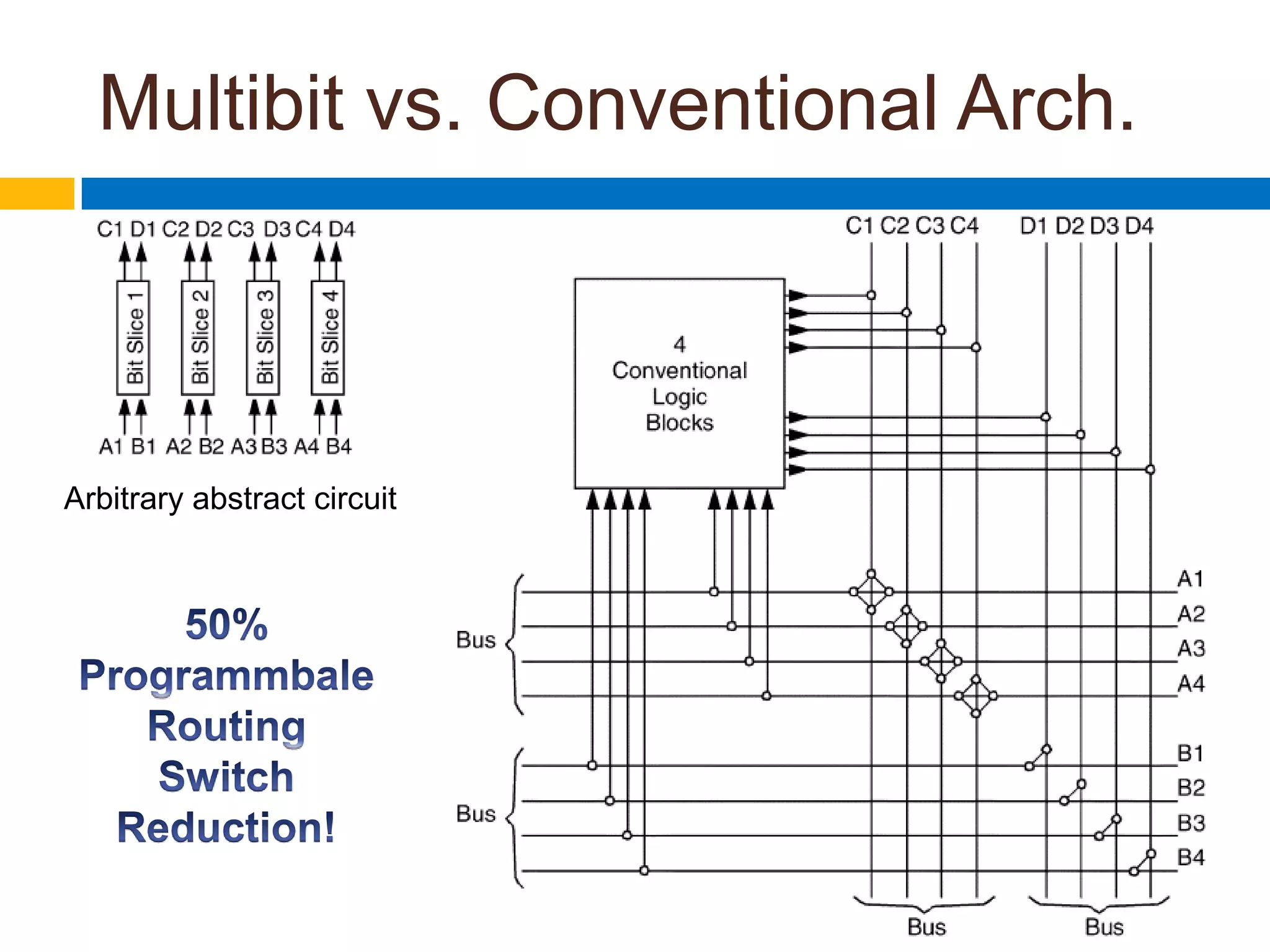

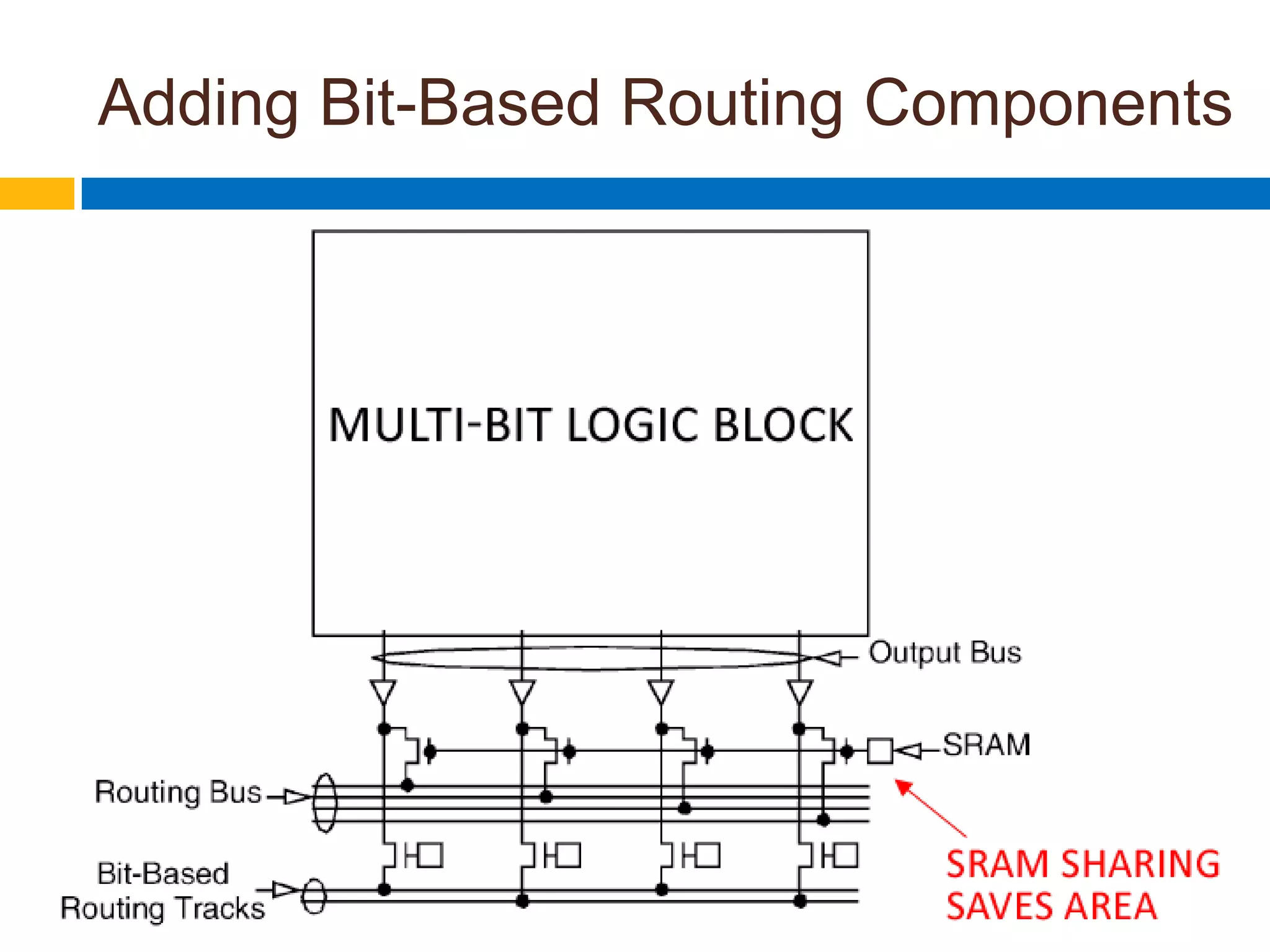

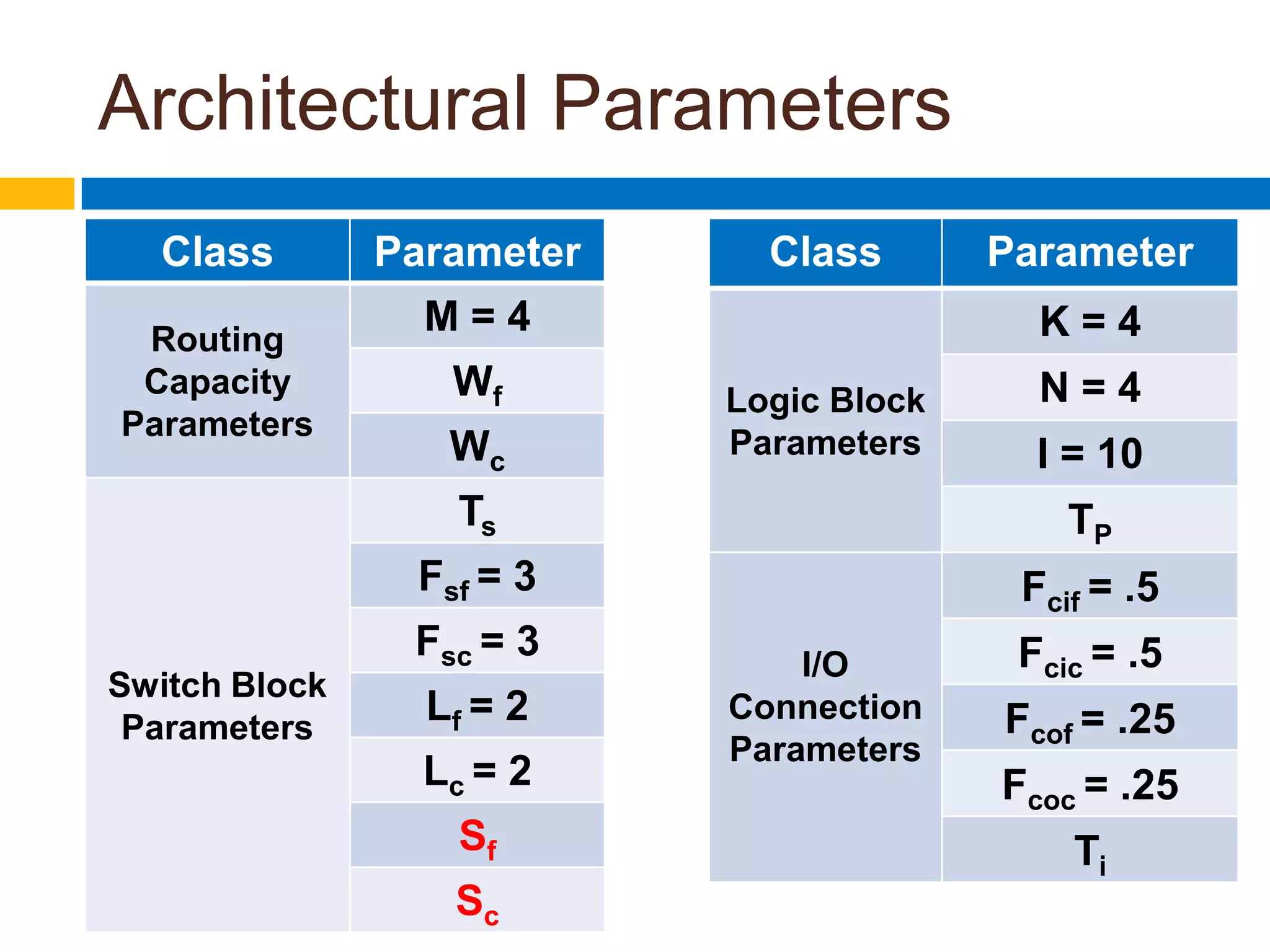

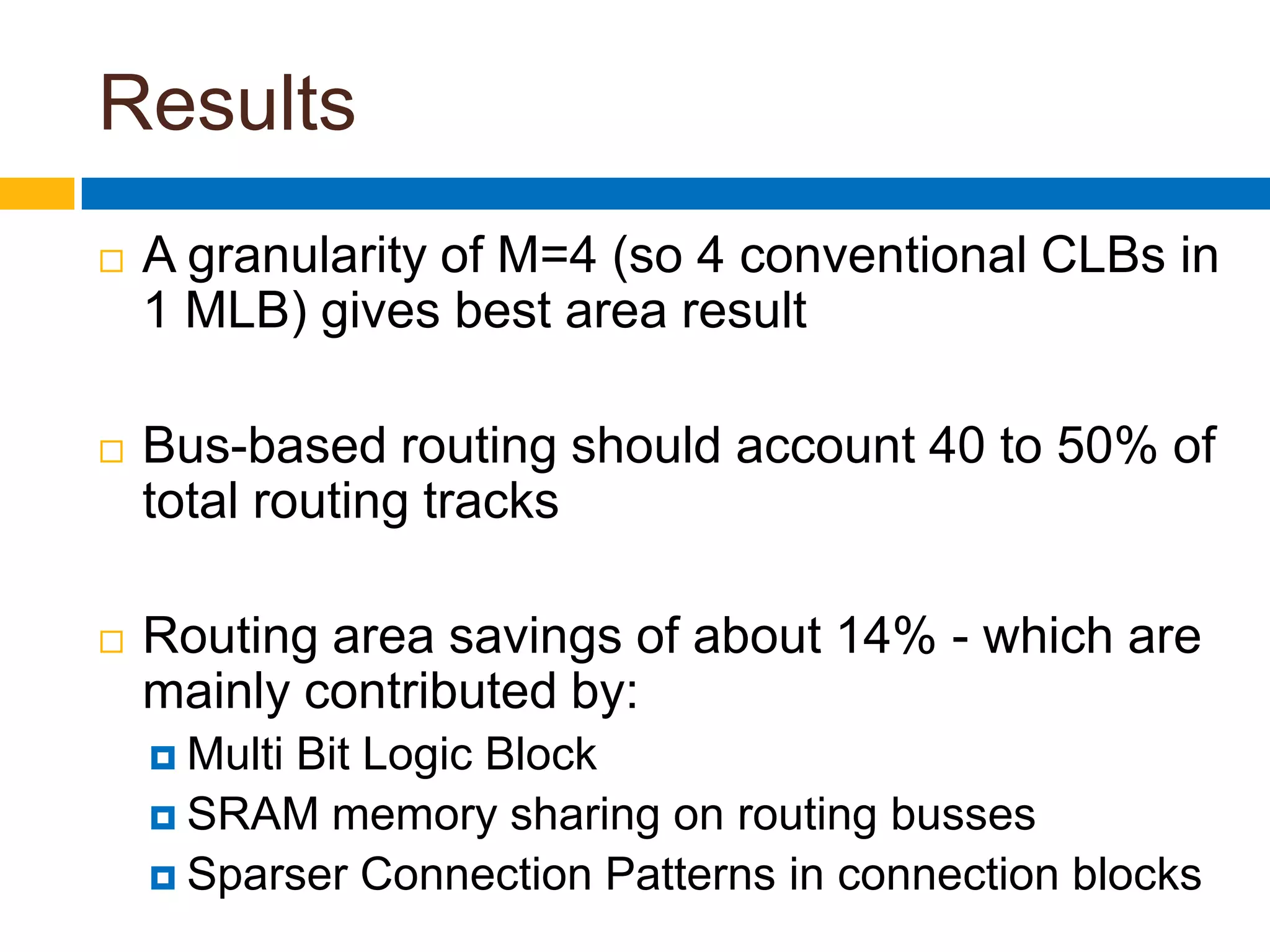

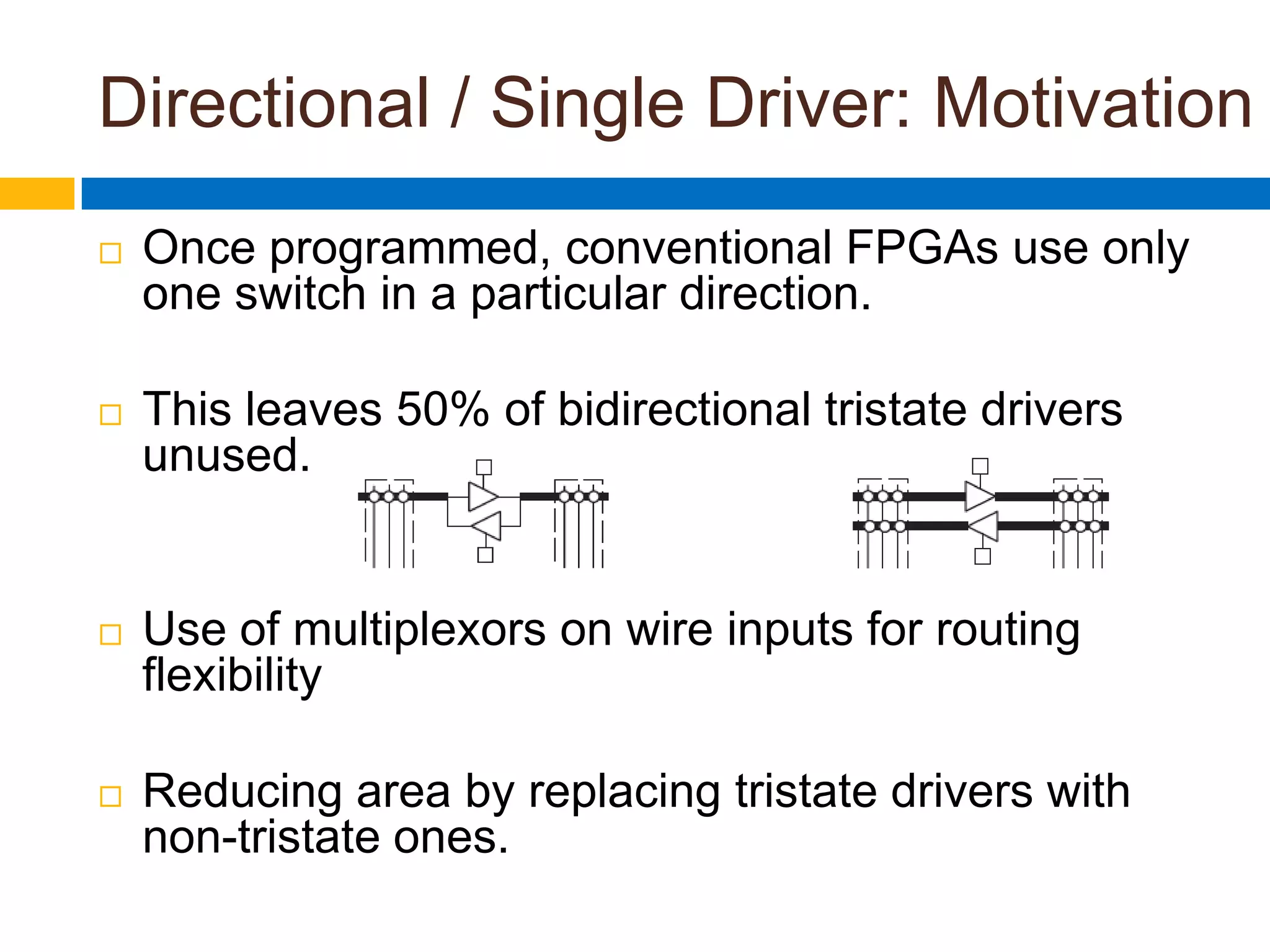

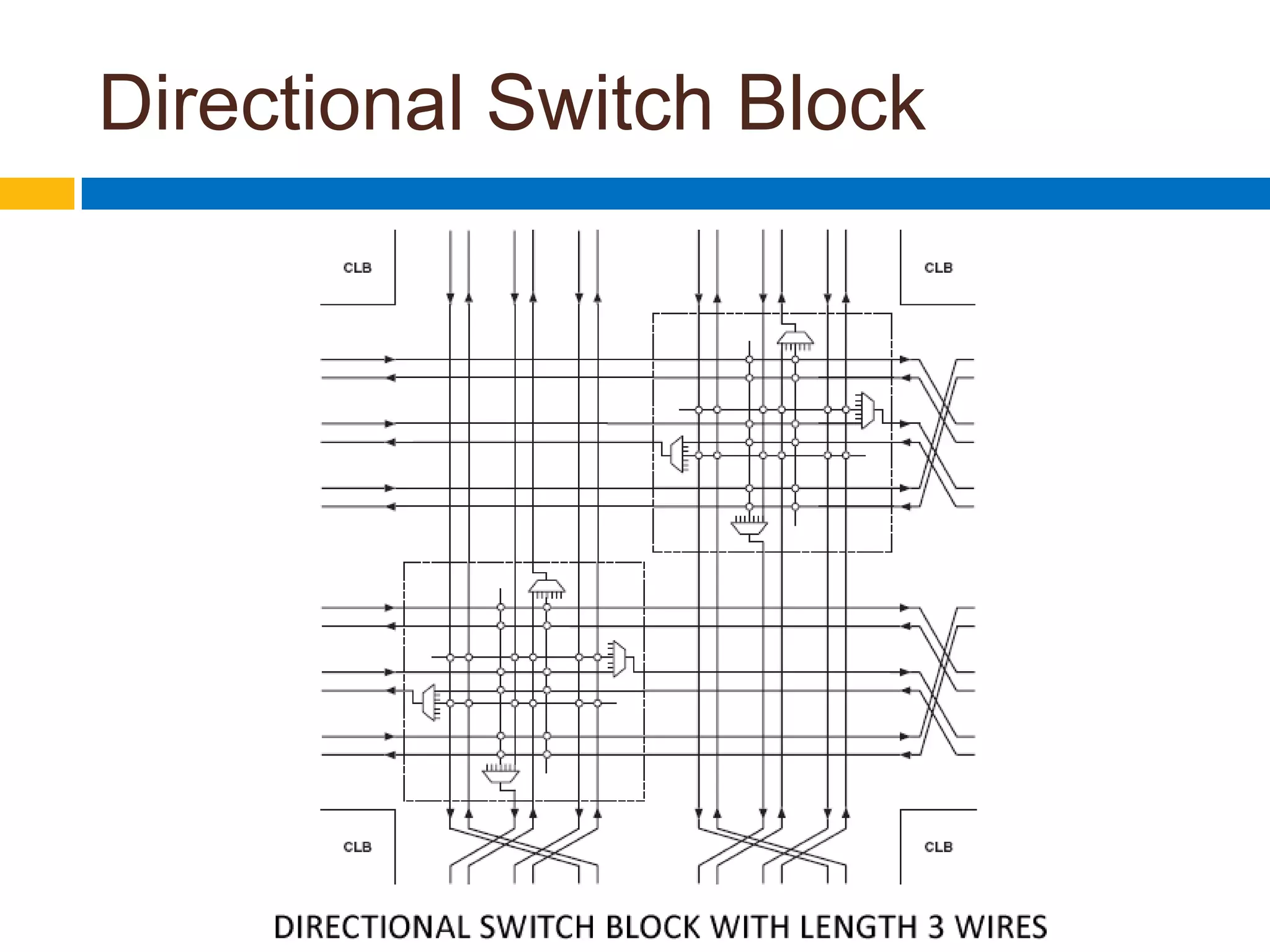

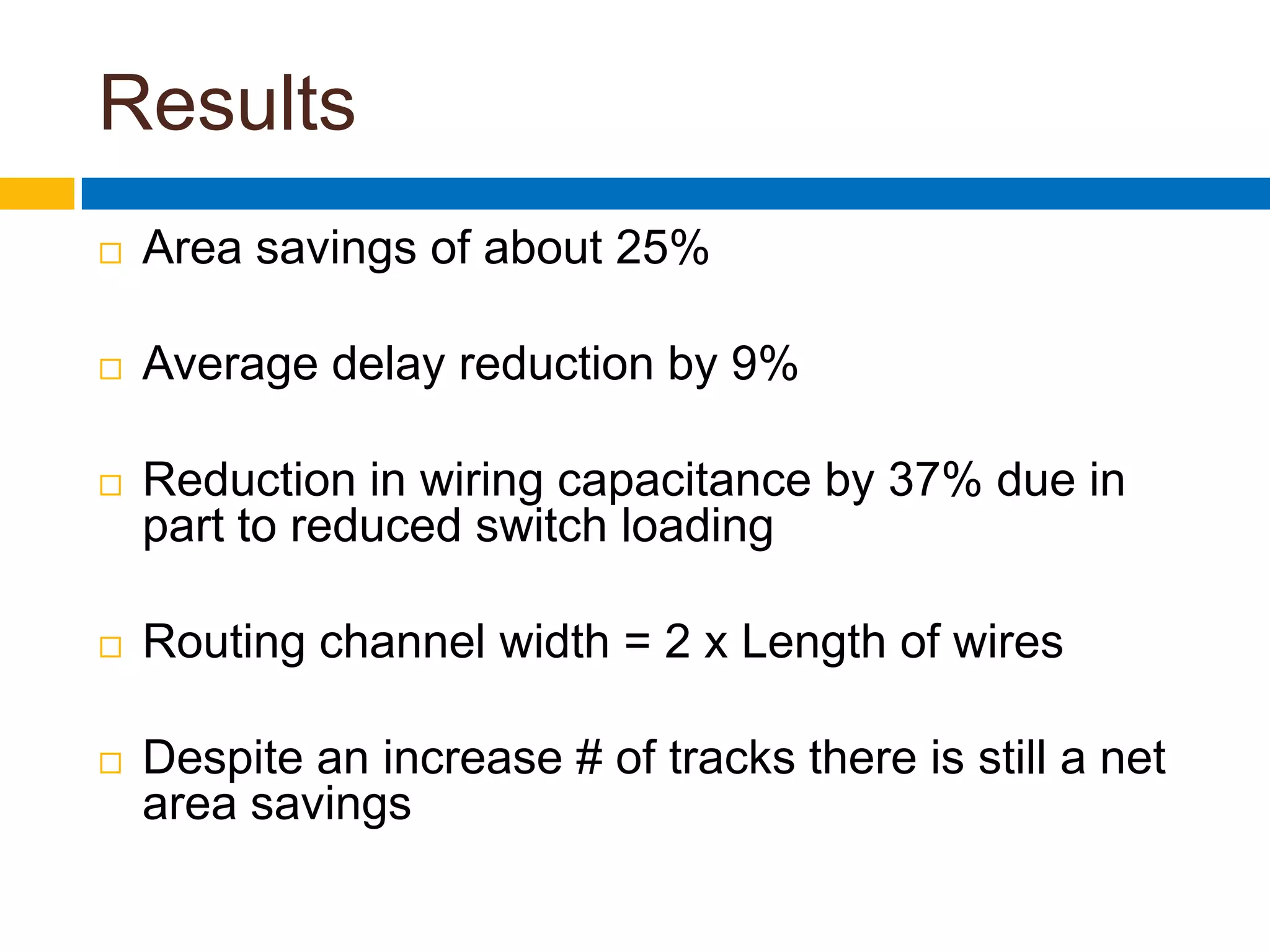

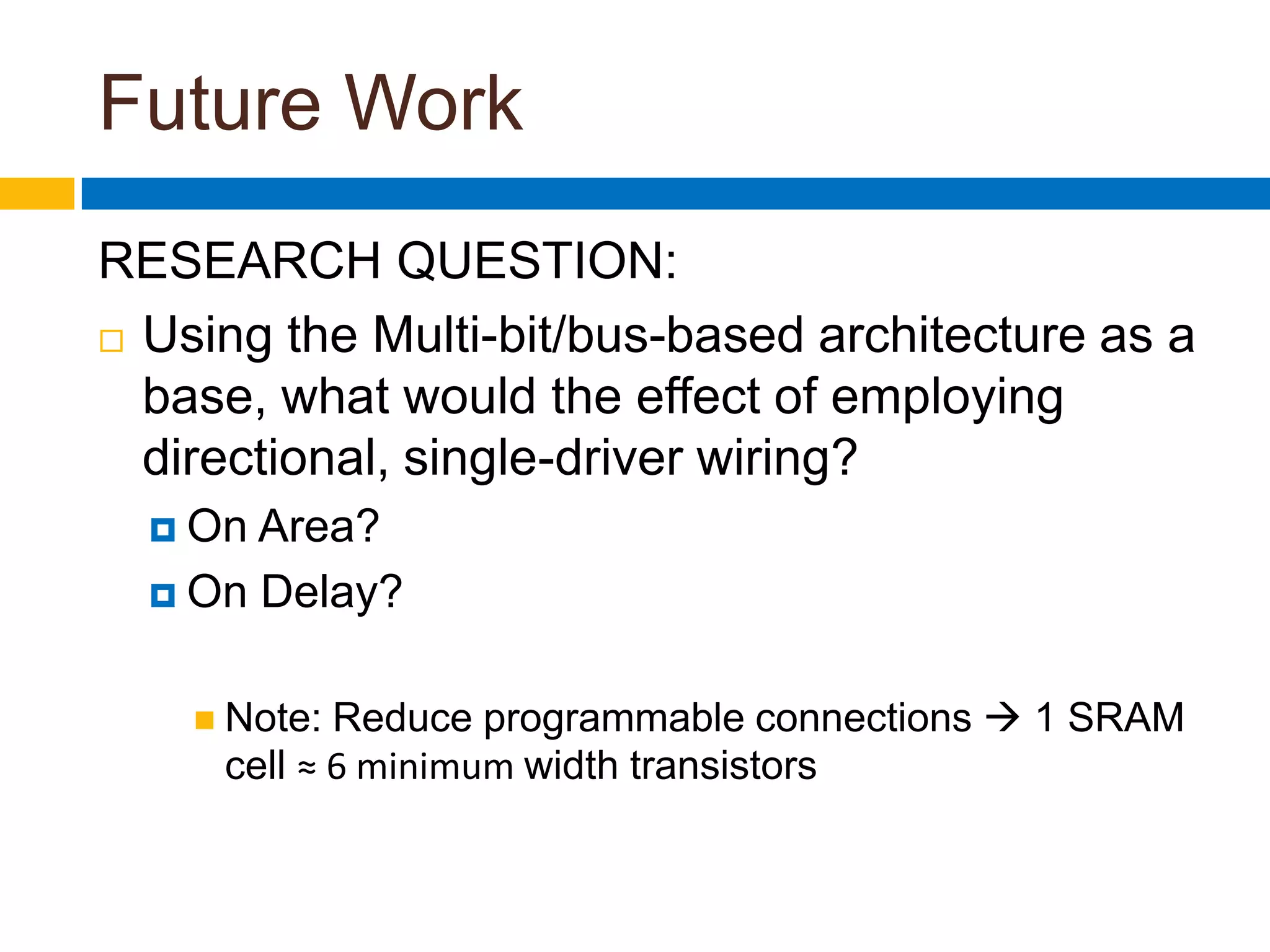

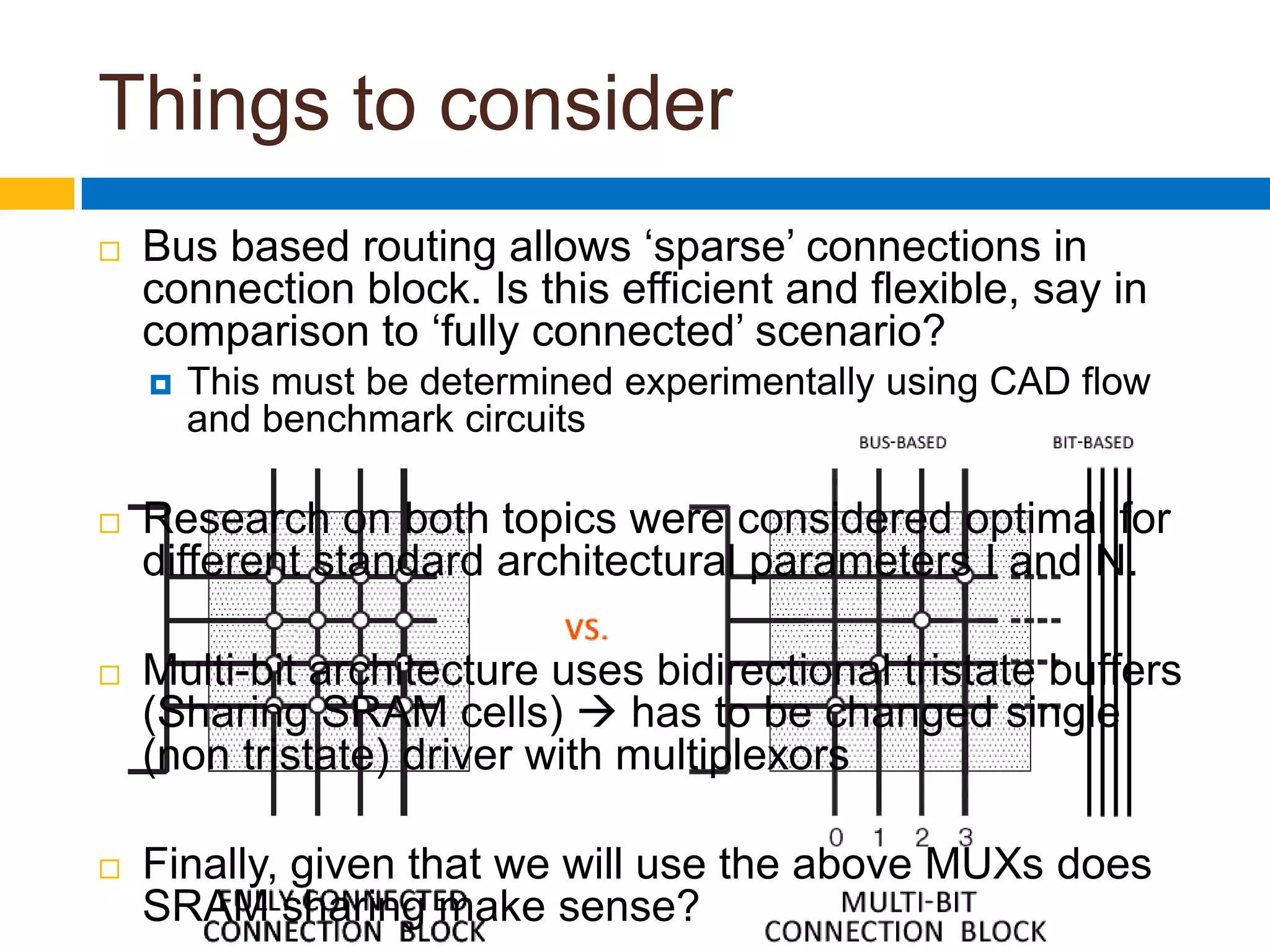

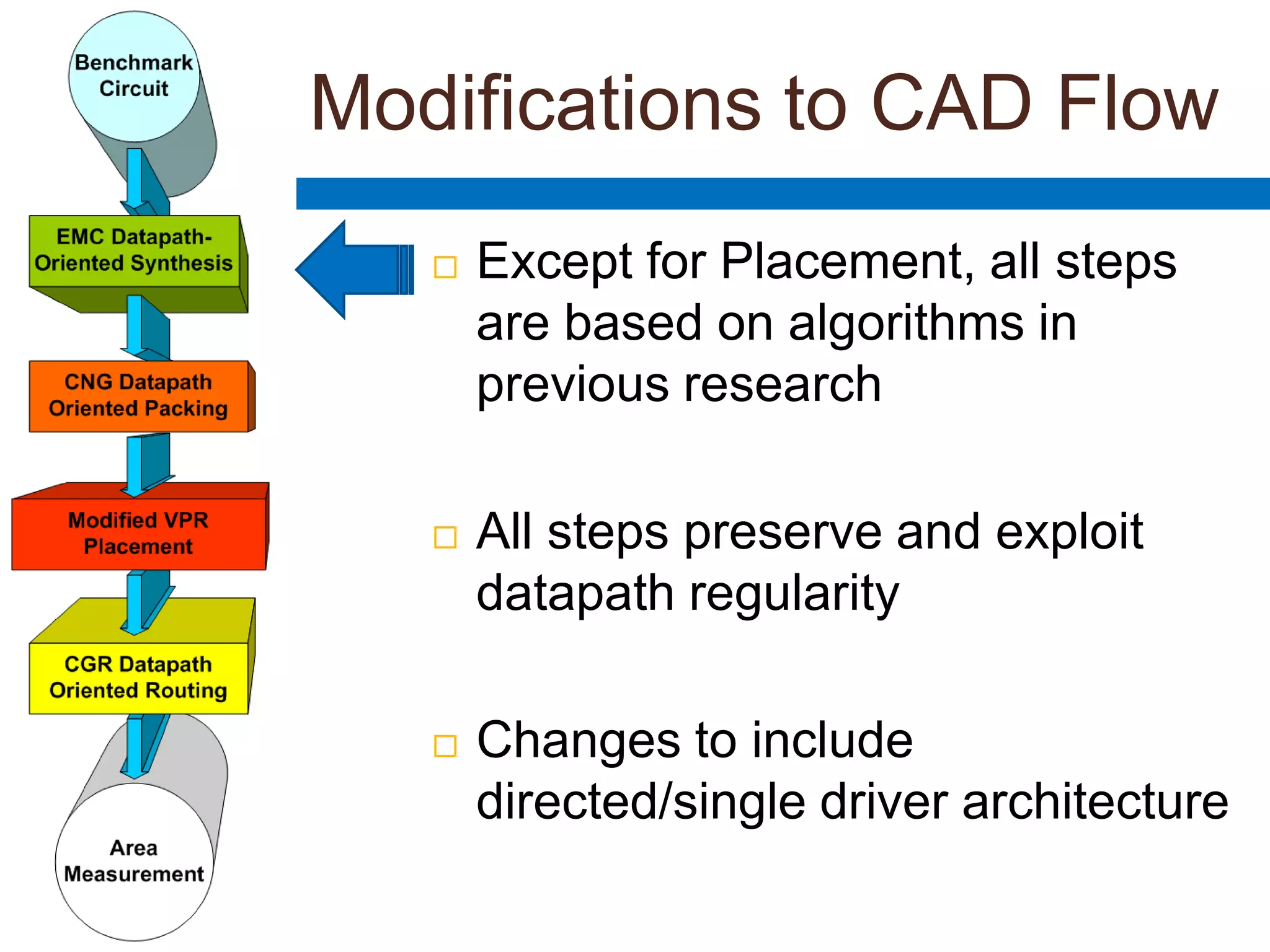

This document summarizes a student's MASc research on developing an area-efficient FPGA architecture for datapath circuits. It proposes combining bus-based and bit-based routing to better utilize multibit computing elements. Simulation results show the multi-bit logic block approach reduces routing area by 14% compared to conventional FPGAs. Future work involves exploring directional single-driver wires which could further reduce area by 25% and delay by 9% on average. The student seeks feedback on modifications to the CAD flow needed to support the new architectural features.

![References[1] Ye, A.; Rose, J., "Using bus-based connections to improve field-programmable gate-array density for implementing datapath circuits," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on , vol.14, no.5, pp. 462-473, May 2006[2] Lemieux, G.; Lee, E.; Tom, M.; Yu, A., "Directional and single-driver wires in FPGA interconnect," Field-Programmable Technology, 2004. Proceedings. 2004 IEEE International Conference on , vol., no., pp. 41-48, 6-8 Dec. 2004[3] A. Ye, J. Rose, and D. Lewis, “Synthesizing datapath circuits for FPGAs with emphasis on area minimization,” in Proc. Int. Conf. Field-Programmable Technol., 2002, pp. 219–227.[4] A.Ye and J. Rose, “Using multi-bit logic blocks and automated packing to improve field- programmable gate array density for implementing datapath circuits,” in Proc. Int. Conf. Field-Programmable Technol., 2004, pp. 129–136.[5] A. Marquardt, V. Betz and J. Rose, “Using Cluster-Based Logic Blocks and Timing-Driven Packing to Improve FPGA Speed and Density”, ACM/SIGDA FPGA 99, 1999, pp. 37-46.[6] A. Ye, “Field-Programmable Gate Array Architectures and Algorithms Optimized for Implementing Datapath Circuits,” Ph.D. thesis, Univ. Toronto, Dept. Elect. Comput. Eng., Univ. Toronto, ON, Canada, 2004 [Online]. Available: (http://www.eecg.toronto.edu/~jayar/pubs/theses/Ye/ AndyYe.pdf)](https://image.slidesharecdn.com/presentation-12528924986699-phpapp02/75/FPGA-Architecture-Presentation-18-2048.jpg)