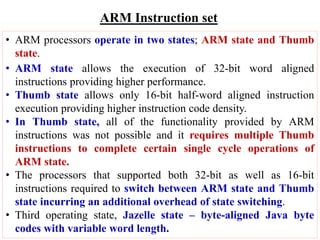

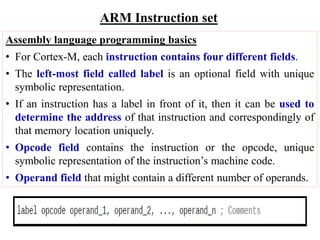

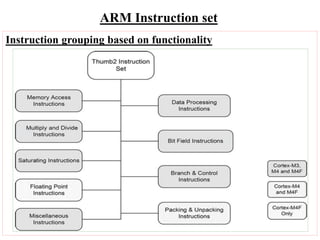

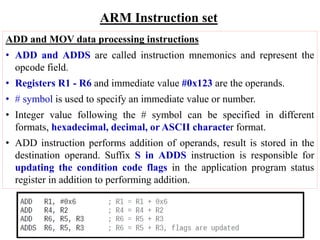

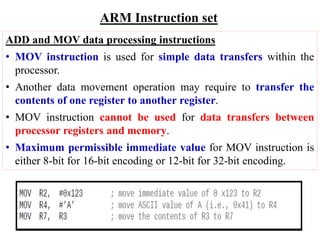

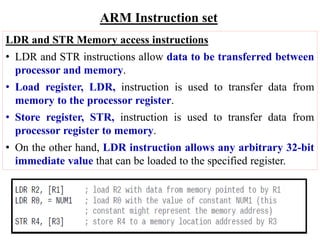

The document discusses ARM processor instruction sets, including ARM and Thumb instruction states. ARM state allows 32-bit instructions for higher performance, while Thumb state uses 16-bit instructions for higher code density. It also describes the basic structure of ARM assembly instructions, grouping instructions by functionality, and provides examples of ADD, MOV, LDR, and STR instructions.