The document describes the NEC SX-6 vector supercomputer. Key points:

- The SX-6 is a high-performance vector supercomputer utilizing a single-chip vector processor that can perform up to 8 billion calculations per second.

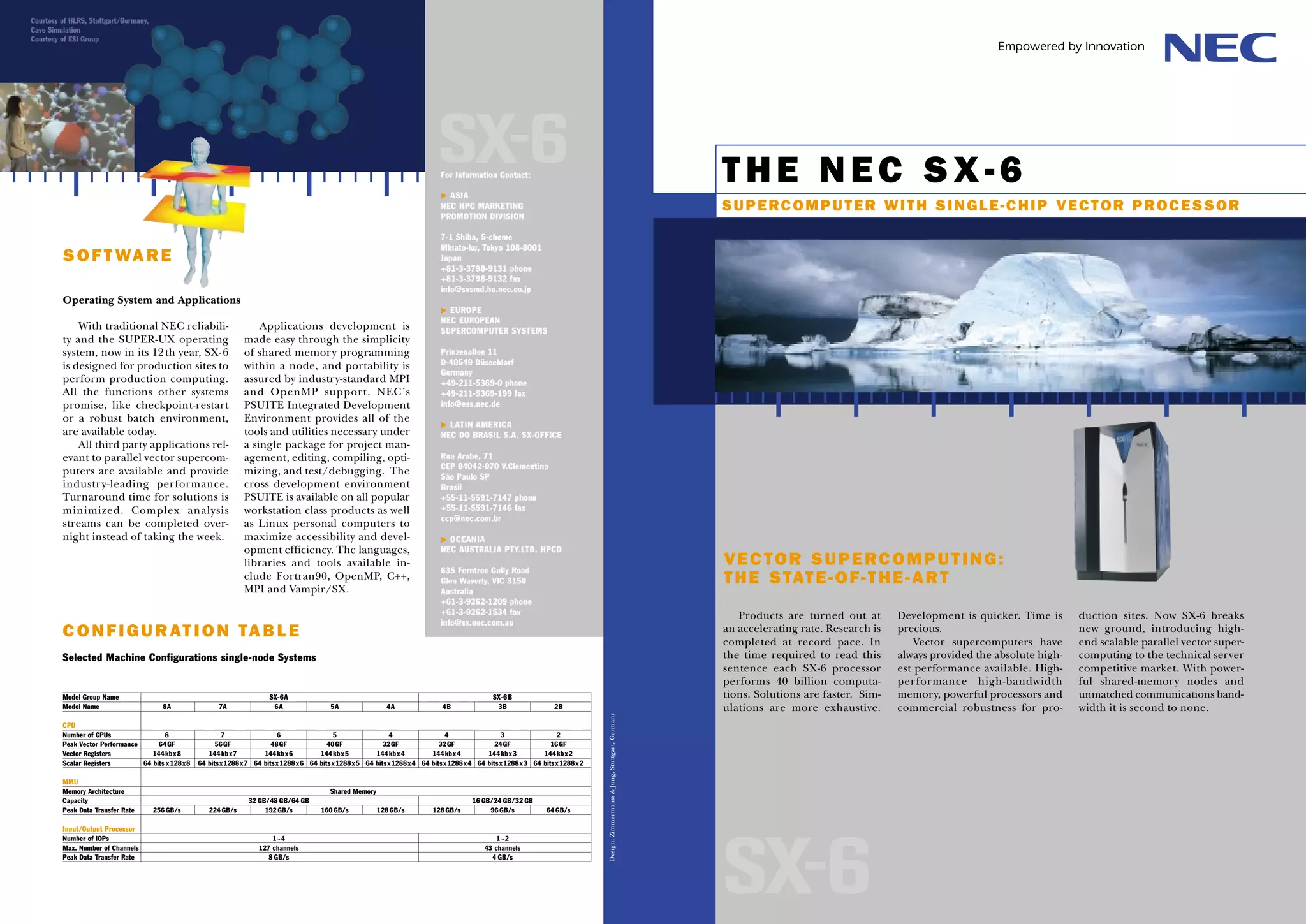

- It provides scalable performance from 16 to 64 GFLOPS and large shared memory capacity of up to 64GB per node. Larger configurations with up to 1024 CPUs and 8 TFLOPS of performance are possible.

- The SX-6 offers improved performance, memory bandwidth, and reliability compared to previous models, driven by its single-chip vector processor design and other technological advancements. It is well-suited for technical computing and simulation applications