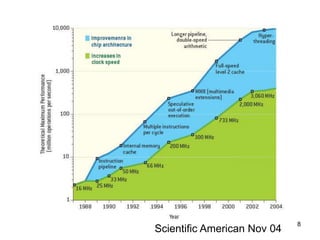

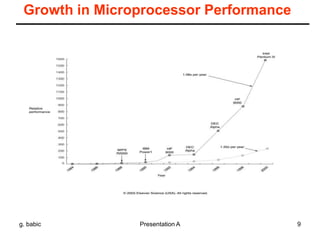

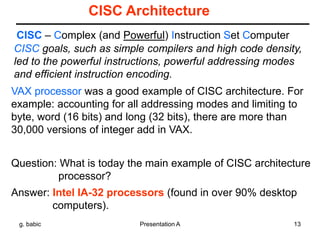

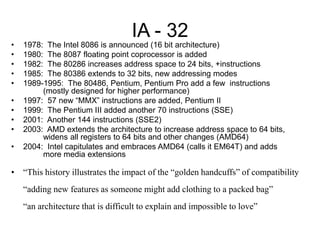

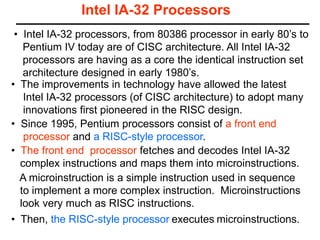

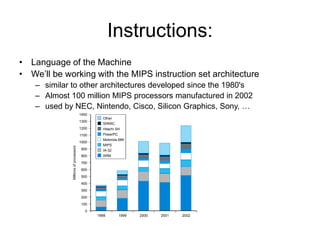

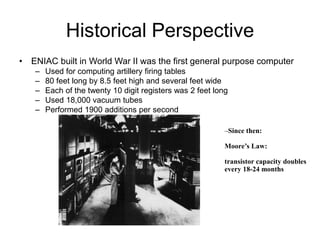

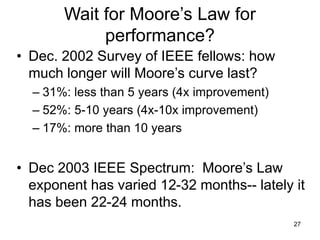

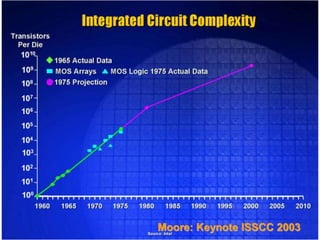

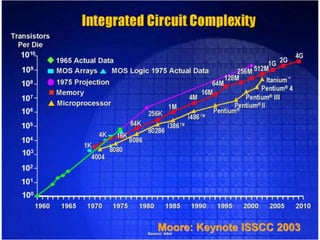

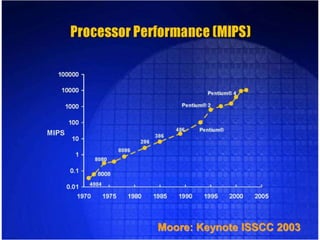

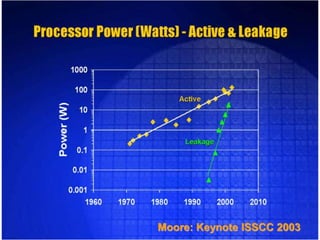

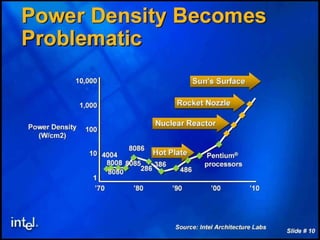

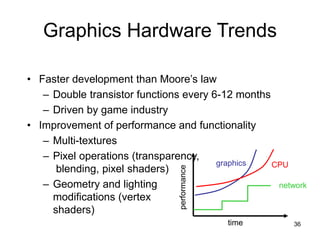

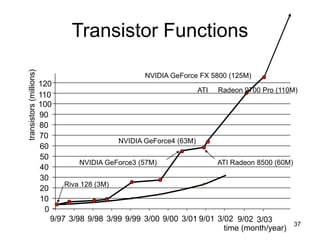

This document summarizes a presentation on computer architecture given by instructor Roger Crawfis. The presentation covered three aspects of computer design: instruction set architecture, computer organization, and computer hardware. It discussed RISC and CISC architectures and how Intel IA-32 processors adopted RISC-style implementations. The presentation also covered technology trends like Moore's Law and improvements in processor and graphics hardware performance over time. The goal of the course is to learn basic principles of processor and memory design using the MIPS instruction set architecture.