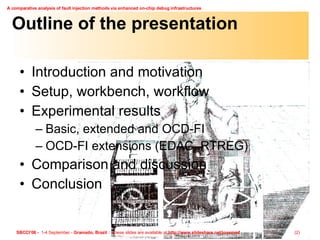

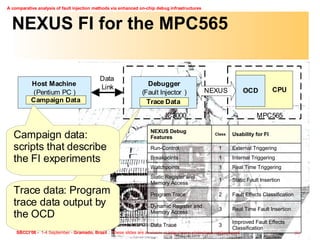

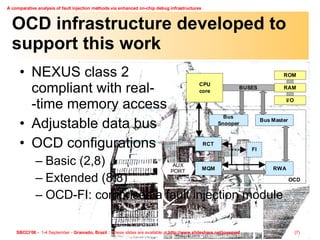

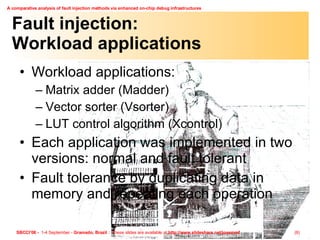

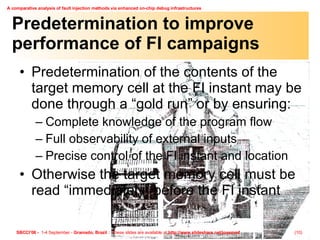

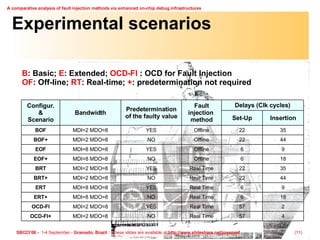

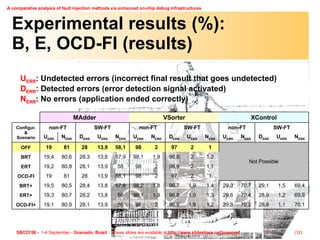

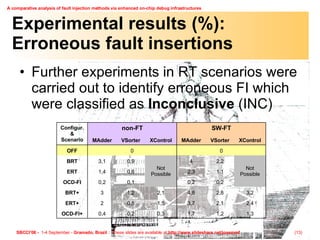

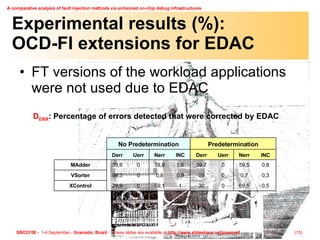

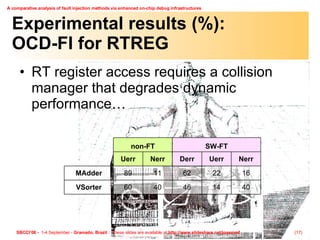

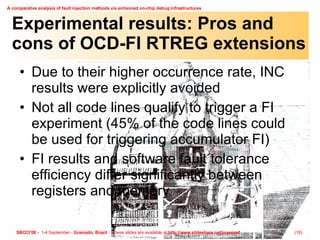

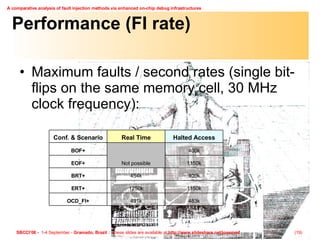

The document presents a comparative analysis of different fault injection methods using on-chip debug (OCD) infrastructures. It describes experiments conducted using a Freescale MPC-565 microprocessor with enhanced OCD capabilities. The experiments compare basic, extended, and OCD-enhanced fault injection configurations across offline and real-time scenarios. Results show that the OCD-enhanced method enables higher fault detection rates with lower performance overhead compared to other approaches.

![A comparative analysis of fault injection methods via enhanced on-chip debug infrastructures J. M. Martins Ferreira [ jmf@fe.up.pt ] FEUP / DEEC Rua Dr. Roberto Frias 4200-465 Porto - PORTUGAL André Fidalgo, Gustavo R. Alves Manuel Gericota [ anf/gca/mgg @isep.ipp.pt ] ISEP / DEE Rua Ant. Bernardino Almeida, 431 4200-072 Porto - PORTUGAL SBCCI’08: Gramado, Brazil, 1-4 September 2008 These slides are available at http://www.slideshare.net/josemmf](https://image.slidesharecdn.com/sbcci08-1215798852304965-9/75/SBCCI08-1-2048.jpg)

![Performance (overhead, dynamic) Silicon overhead and maximum operating frequency on a Virtex-2 FPGA: 25 108,3% 77484 x x +BOTH x 27 106,8% 76392 x +RTREG x 32 102,3% 73184 x +EDAC x 36 100,4% 71842 x x 36 106,4% 76127 ERT x 32 101,5% 72619 x BRT x 36 100,0% 71527 BRT x 32 76,9% 55018 x x 37 75,4% 53926 x [MHz] [%] [Eq Gates] Max f Overhead Area RTREG EDAC OCD-FI OCD CPU Core](https://image.slidesharecdn.com/sbcci08-1215798852304965-9/85/SBCCI08-20-320.jpg)