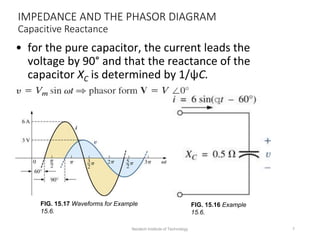

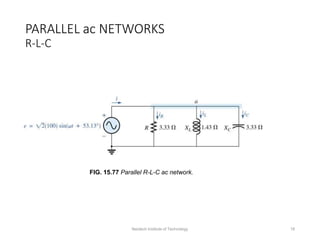

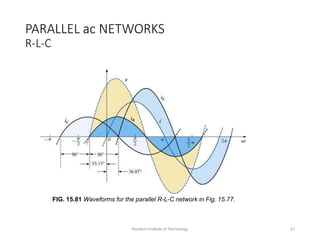

This document discusses series and parallel ac circuits. It begins by outlining the objectives of becoming familiar with the characteristics and calculations for series and parallel ac networks. It then covers impedance and phasor diagrams for resistive, inductive, and capacitive elements. Key concepts explained include impedance, reactance, admittance, and applying voltage and current divider rules. Worked examples are provided with corresponding phasor and waveform diagrams to illustrate various series and parallel ac circuit configurations.