Rf power amplifiers for wireless communications ch10 6

•

0 likes•59 views

for learning

Report

Share

Report

Share

Download to read offline

Recommended

A 10 d bm 25 dbm, 0.363 mm2 two stage 130 nm rf cmos power amplifier

This paper proposes a 2.4 GHz RF CMOS Power amplifi

er and variation in its main performance

parameters i.e, output power, S-parameters and powe

r added efficiency with respect to change in supply

voltage and size of the power stage transistor. The

supply voltage was varied form 1 V to 5 V and the

range

of output power at 1dB compression point was found

to be from 10.684 dBm to 25.08 dBm respectively.

The range of PAE is 16.65 % to 48.46 %. The width o

f the power stage transistor was varied from 150 μm

to 500 μm to achieve output power of range 15.47 dB

m to 20.338 dBm. The range of PAE obtained here is

29.085 % to 45.439 %. The total dimension of the la

yout comes out to be 0.714 * 0.508 mm

2

.

Design and analysis of low power pseudo differential

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology.

A Review on Wide Bandwidth Low Noise Amplifier for Modern Wireless Communication

https://irjet.net/archives/V4/i10/IRJET-V4I10161.pdf

A 60 GHz CMOS Power Amplifier for Wireless Communications

This paper presents a 60 GHz power amplifier (PA) suitable for wireless communications. The two-stage wideband PA is fabricated in 55 nm CMOS. Measurement results show that the PA obtains a peak gain of 16 dB over a -3 dB bandwidth from 57 GHz to 67 GHz. It archives an output 1 dB compression point (OP1dB) of 4 dBm and a peak power added efficiency (PAE) of 12.6%. The PA consumes a total DC power of 38.3 mW from a 1.2 V supply voltage while its core occupies a chip area of 0.45 mm 2 .

An operational amplifier with recycling folded cascode topology and adaptive ...

This paper presents a highly adaptive operational amplifier with high gain, high bandwidth, high speed

and low power consumption. By adopting the recycling folded cascode topology along with an adaptivebiasing

circuit, this design achieves high performance in terms of gain-bandwidth product (GBW) and slew

rate (SR). This single stage op-amp has been designed in 0.18μm technology with a power supply of 1.8V

and a 5pF load. The simulation results show that the amplifier achieved a GBW of 335.5MHz, Unity Gain

Bandwidth of 247.1MHz and a slew rate of 92.8V/μs.

A New CMOS Fully Differential Low Noise Amplifier for Wideband Applications

In this paper, a multi-stage fully differential low noise amplifier (LNA) has been presented for

wideband applications. A common-gate input stage is used to improve the input impedance matching and

linearity. A common-source stage is also used as the second stage to enhance gain and reduce noise. A

shunt-shunt feedback is employed to extend bandwidth and enhance linearity. The proposed low noise

amplifier has been designed and simulated using RF-TSMC 0.18 μm CMOS process technology. In

frequency band of 3.5-7.5 GHz, this amplifier has a flat power gain (S21) of 16.5 ± 1.5 dB, low noise figure

(NF) of 3dB, input (S11) and output (S22) return losses less than -10 dB and high linearity with input thirdorder

intercept point (IIP3) of -3dBm. It’s power consumption is also less than 10 mw with low power supply

voltage of 0.8v.

Recommended

A 10 d bm 25 dbm, 0.363 mm2 two stage 130 nm rf cmos power amplifier

This paper proposes a 2.4 GHz RF CMOS Power amplifi

er and variation in its main performance

parameters i.e, output power, S-parameters and powe

r added efficiency with respect to change in supply

voltage and size of the power stage transistor. The

supply voltage was varied form 1 V to 5 V and the

range

of output power at 1dB compression point was found

to be from 10.684 dBm to 25.08 dBm respectively.

The range of PAE is 16.65 % to 48.46 %. The width o

f the power stage transistor was varied from 150 μm

to 500 μm to achieve output power of range 15.47 dB

m to 20.338 dBm. The range of PAE obtained here is

29.085 % to 45.439 %. The total dimension of the la

yout comes out to be 0.714 * 0.508 mm

2

.

Design and analysis of low power pseudo differential

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology.

A Review on Wide Bandwidth Low Noise Amplifier for Modern Wireless Communication

https://irjet.net/archives/V4/i10/IRJET-V4I10161.pdf

A 60 GHz CMOS Power Amplifier for Wireless Communications

This paper presents a 60 GHz power amplifier (PA) suitable for wireless communications. The two-stage wideband PA is fabricated in 55 nm CMOS. Measurement results show that the PA obtains a peak gain of 16 dB over a -3 dB bandwidth from 57 GHz to 67 GHz. It archives an output 1 dB compression point (OP1dB) of 4 dBm and a peak power added efficiency (PAE) of 12.6%. The PA consumes a total DC power of 38.3 mW from a 1.2 V supply voltage while its core occupies a chip area of 0.45 mm 2 .

An operational amplifier with recycling folded cascode topology and adaptive ...

This paper presents a highly adaptive operational amplifier with high gain, high bandwidth, high speed

and low power consumption. By adopting the recycling folded cascode topology along with an adaptivebiasing

circuit, this design achieves high performance in terms of gain-bandwidth product (GBW) and slew

rate (SR). This single stage op-amp has been designed in 0.18μm technology with a power supply of 1.8V

and a 5pF load. The simulation results show that the amplifier achieved a GBW of 335.5MHz, Unity Gain

Bandwidth of 247.1MHz and a slew rate of 92.8V/μs.

A New CMOS Fully Differential Low Noise Amplifier for Wideband Applications

In this paper, a multi-stage fully differential low noise amplifier (LNA) has been presented for

wideband applications. A common-gate input stage is used to improve the input impedance matching and

linearity. A common-source stage is also used as the second stage to enhance gain and reduce noise. A

shunt-shunt feedback is employed to extend bandwidth and enhance linearity. The proposed low noise

amplifier has been designed and simulated using RF-TSMC 0.18 μm CMOS process technology. In

frequency band of 3.5-7.5 GHz, this amplifier has a flat power gain (S21) of 16.5 ± 1.5 dB, low noise figure

(NF) of 3dB, input (S11) and output (S22) return losses less than -10 dB and high linearity with input thirdorder

intercept point (IIP3) of -3dBm. It’s power consumption is also less than 10 mw with low power supply

voltage of 0.8v.

Open Loop Control Of Series Parallel Resonant Converter

Resonant converters are desirable for power

conversion due to their comparatively smaller size and

lower power losses resulting from high-frequency

operation and inherent soft switching. Among all the

topologies of the resonant converters, the series–parallel

resonant converter (SPRC) is known to have the

combined merits of the series resonant converter and

parallel resonant converter. The converter can regulate

the output voltage at a constant switching frequency even

for a change in load resistance from full load resistance to

infinity while maintaining good part load efficiency. The

purpose of this project is to design a closed loop

controller for the phase-controlled series parallel

resonant converter (PC SPRC). The open loop analysis

and closed loop control has been provided in this paper.

Performance analysis of High Speed ADC using SR F/F

http://www.iosrjournals.org/iosr-jvlsi/pages/v1i4.html

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

In Analog to Digital Converter (ADC), high speed comparator influences the overall performance of ADC directly. This paper presents the high speed & low power design of a CMOS comparator. Schematic design of this comparator is fabricated in a 0.18μm UMC Technology with 1.8V power supply and simulated in cadence Virtuoso. Simulation results are presented and it shows that this design can work under high speed of 0.8108 GHz. The design has a low offset voltage, low power dissipation 108.0318μw. In addition we have verified present results with schematic view design and also compared these results with earlier reported work and got improvement in this reported work.

A Low Power, 8-Bit, 5MS/s Digital to Analog Converter for Successive Approxim...

http://www.iosrjournals.org/iosr-jvlsi/pages/v1i4.html

IRJET-Design of Capacitor Less LDO Regulator by using Cascode Compensation Te...

https://irjet.net/archives/V5/i6/IRJET-V5I6322.pdf

DESIGN OF HIGH EFFICIENCY TWO STAGE POWER AMPLIFIER IN 0.13UM RF CMOS TECHNOL...

International Journal of VLSI design & Communication Systems (VLSICS)

Double feedback technique for reduction of Noise LNA with gain enhancement

In this paper we present a balun low noise amplifier (LNA) in which the gain is boosted by using a double feedback structure. The circuit is based on a conventional balun LNA with noise and distortion cancelation. The LNA is based on the combination of a common-gate (CG) stage and common-source (CS) stage. We propose to replace the load resistors by active loads, which can be used to implement local feedback loops (in the CG and CS stages). This will boost the gain and reduce the noise figure (NF). Simulation results, with a 130nm CMOS technology, show that the gain is 24dB and the NF is less than 2.7dB. The total power dissipation is only 5.4mW (since no extra blocks are required), leading to a figure-of-merit (FOM) of 3.8mW-1 using a nominal 1.2V supply. Measurement results are presented for the proposed DFBLNA included in a receiver frontend for biomedical applications (ISM and WMTS).

Design of a low-power compact CMOS variable gain amplifier for modern RF rece...

The demand for portability has speeded up the design of low-power electronic communication devices. Variable gain amplifier (VGA) is one of the most vulnerable elements of every modern receiver for the proper baseband processing of the signal. CMOS VGAs are generally suffered from low bandwidth and small gain range. In this research, a two-stage class AB VGA, each stage comprising of a direct transconductance amplifier and a linear transimpedance amplifier, is designed in Silterra 0.13-μm CMOS utilizing Mentor Graphics environment. The post-layout simulation results reveal that the VGA design achieves the widest bandwidth of >200 MHz and high gain range from -33 to 32 dB. The VGA dissipates only 2mW from a single 1.2 V DC supply. The core chip area of the VGA is also only 0.026 mm2 which is also the lowest compared to recent researches. Such a VGA will be a very useful module for all modern communication devices.

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier

using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve

linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range

using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped

and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization

technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS)

tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB),

6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward

linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of

8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier

without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer

had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression

point.

Design of a high frequency low voltage CMOS operational amplifier

A method is presented in this paper for the design of a high frequency CMOS operational amplifier (OpAmp) which operates at 3V power supply using tsmc 0.18 micron CMOS technology. The OPAMP designed is a two-stage CMOS OPAMP followed by an output buffer. This Operational Transconductance Amplifier (OTA) employs a Miller capacitor and is compensated with a current buffer compensation technique. The unique behaviour of the MOS transistors in saturation region not only allows a designer to work at a low voltage, but also at a high frequency. Designing of two-stage op-amps is a multi-dimensional-optimization problem where optimization of one or more parameters may easily result into degradation of others. The OPAMP is designed to exhibit a unity gain frequency of 2.02GHz and exhibits a gain of 49.02dB with a 60.50 phase margin. As compared to the conventional approach, the proposed compensation method results in a higher unity gain frequency under the same load condition. Design has been carried out in Tanner tools. Simulation results are verified using S-edit and W-edit.

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS) tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB), 6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of 8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression point

IRJET- Design of 4th Order Low Pass Filter using Memristive OP-AMPS

https://www.irjet.net/archives/V6/i6/IRJET-V6I6238.pdf

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier

using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve

linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range

using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped

and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization

technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS)

tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB),

6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward

linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of

8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier

without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer

had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression

point.

0.5GHz - 1.5GHz Bandwidth 10W GaN HEMT RF Power Amplifier Design

With the current development in wireless communication technology, the need for a wide bandwith in RF power amplifier (RF PA) is an essential. In this paper, the design and simulation of 10W GaN HEMT wideband RF PA will be presented. The Source-Pull and Load-Pull technique was used to design the input and output matching network of the RF PA. From the simulation, the RF PA achieved a flat gain between 15dB to 17dB from 0.5GHz to 1.5GHz. At 1.5GHz, the drain efficiency is simulated to achieve 36% at the output power of 40 dBm while the power added efficiency (PAE) was found to be 28.2%.

K0536569

IOSR Journal of Electronics and Communication Engineering(IOSR-JECE) is an open access international journal that provides rapid publication (within a month) of articles in all areas of electronics and communication engineering and its applications. The journal welcomes publications of high quality papers on theoretical developments and practical applications in electronics and communication engineering. Original research papers, state-of-the-art reviews, and high quality technical notes are invited for publications.

A Novel Design of a Microstrip Microwave Power Amplifier for DCS Application ...

This paper presents a 1.80GHz class-A Microwave power amplifier (PA). The proposed power amplifier is designed with single-stage architecture. This power amplifier consists of a bipolar transistor and improved by Collector-Feedback Biasing fed with a single power supply. The aim of this work is to improve the performance of this amplifier by using simple stubs with 50Ω microstrip transmissions lines. The proposed PA is investigated and optimized by utilizing Advanced Design System (ADS) software. The simulation results show that the amplifier achieves a high power gain of 13dB, output power rise up to 21dBm and good impedances matching ;For the input reflection coefficient (S11) is below than - 46.39dB. Regarding the output reflection coefficient (S22) is below than -29.898dB, with an overall size of about 93 x 59mm². By the end; we find that this power amplifier offers an excellent performance for DCS applications.

Closed Loop Power Control of Grid Connected DG Units for Reducing Active Harm...

https://irjet.net/archives/V4/i8/IRJET-V4I8386.pdf

More Related Content

What's hot

Open Loop Control Of Series Parallel Resonant Converter

Resonant converters are desirable for power

conversion due to their comparatively smaller size and

lower power losses resulting from high-frequency

operation and inherent soft switching. Among all the

topologies of the resonant converters, the series–parallel

resonant converter (SPRC) is known to have the

combined merits of the series resonant converter and

parallel resonant converter. The converter can regulate

the output voltage at a constant switching frequency even

for a change in load resistance from full load resistance to

infinity while maintaining good part load efficiency. The

purpose of this project is to design a closed loop

controller for the phase-controlled series parallel

resonant converter (PC SPRC). The open loop analysis

and closed loop control has been provided in this paper.

Performance analysis of High Speed ADC using SR F/F

http://www.iosrjournals.org/iosr-jvlsi/pages/v1i4.html

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

In Analog to Digital Converter (ADC), high speed comparator influences the overall performance of ADC directly. This paper presents the high speed & low power design of a CMOS comparator. Schematic design of this comparator is fabricated in a 0.18μm UMC Technology with 1.8V power supply and simulated in cadence Virtuoso. Simulation results are presented and it shows that this design can work under high speed of 0.8108 GHz. The design has a low offset voltage, low power dissipation 108.0318μw. In addition we have verified present results with schematic view design and also compared these results with earlier reported work and got improvement in this reported work.

A Low Power, 8-Bit, 5MS/s Digital to Analog Converter for Successive Approxim...

http://www.iosrjournals.org/iosr-jvlsi/pages/v1i4.html

IRJET-Design of Capacitor Less LDO Regulator by using Cascode Compensation Te...

https://irjet.net/archives/V5/i6/IRJET-V5I6322.pdf

DESIGN OF HIGH EFFICIENCY TWO STAGE POWER AMPLIFIER IN 0.13UM RF CMOS TECHNOL...

International Journal of VLSI design & Communication Systems (VLSICS)

Double feedback technique for reduction of Noise LNA with gain enhancement

In this paper we present a balun low noise amplifier (LNA) in which the gain is boosted by using a double feedback structure. The circuit is based on a conventional balun LNA with noise and distortion cancelation. The LNA is based on the combination of a common-gate (CG) stage and common-source (CS) stage. We propose to replace the load resistors by active loads, which can be used to implement local feedback loops (in the CG and CS stages). This will boost the gain and reduce the noise figure (NF). Simulation results, with a 130nm CMOS technology, show that the gain is 24dB and the NF is less than 2.7dB. The total power dissipation is only 5.4mW (since no extra blocks are required), leading to a figure-of-merit (FOM) of 3.8mW-1 using a nominal 1.2V supply. Measurement results are presented for the proposed DFBLNA included in a receiver frontend for biomedical applications (ISM and WMTS).

Design of a low-power compact CMOS variable gain amplifier for modern RF rece...

The demand for portability has speeded up the design of low-power electronic communication devices. Variable gain amplifier (VGA) is one of the most vulnerable elements of every modern receiver for the proper baseband processing of the signal. CMOS VGAs are generally suffered from low bandwidth and small gain range. In this research, a two-stage class AB VGA, each stage comprising of a direct transconductance amplifier and a linear transimpedance amplifier, is designed in Silterra 0.13-μm CMOS utilizing Mentor Graphics environment. The post-layout simulation results reveal that the VGA design achieves the widest bandwidth of >200 MHz and high gain range from -33 to 32 dB. The VGA dissipates only 2mW from a single 1.2 V DC supply. The core chip area of the VGA is also only 0.026 mm2 which is also the lowest compared to recent researches. Such a VGA will be a very useful module for all modern communication devices.

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier

using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve

linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range

using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped

and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization

technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS)

tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB),

6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward

linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of

8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier

without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer

had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression

point.

Design of a high frequency low voltage CMOS operational amplifier

A method is presented in this paper for the design of a high frequency CMOS operational amplifier (OpAmp) which operates at 3V power supply using tsmc 0.18 micron CMOS technology. The OPAMP designed is a two-stage CMOS OPAMP followed by an output buffer. This Operational Transconductance Amplifier (OTA) employs a Miller capacitor and is compensated with a current buffer compensation technique. The unique behaviour of the MOS transistors in saturation region not only allows a designer to work at a low voltage, but also at a high frequency. Designing of two-stage op-amps is a multi-dimensional-optimization problem where optimization of one or more parameters may easily result into degradation of others. The OPAMP is designed to exhibit a unity gain frequency of 2.02GHz and exhibits a gain of 49.02dB with a 60.50 phase margin. As compared to the conventional approach, the proposed compensation method results in a higher unity gain frequency under the same load condition. Design has been carried out in Tanner tools. Simulation results are verified using S-edit and W-edit.

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS) tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB), 6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of 8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression point

IRJET- Design of 4th Order Low Pass Filter using Memristive OP-AMPS

https://www.irjet.net/archives/V6/i6/IRJET-V6I6238.pdf

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

This paper proposes a design of 0.15μm Monolithic Microwave Integrated Circuit (MMIC) power amplifier

using GaAs pHEMT technology at 2.4 GHz which employs feed forward linearization technique to improve

linearity. The amplifier is designed to operate in personal communication systems (PCS) frequency range

using WIN semiconductor GaAs pHEMT technology. Single stage power amplifier is designed in lumped

and distributed components with its layout. Linearity of PA is improved by Feed forward Linearization

technique. To evaluate the performance of proposed linearized amplifier, Advanced Design system (ADS)

tool is used. The designed circuit results with 13.65dBm output power at 1dB compression point (P1dB),

6dB power gain and maximum Power added efficiency of 16.4%. Linearity achieved by feed forward

linearizer circuit with third order intermodulation suppression of 30dBc for the output power level of

8.217dBm and 1dB compression point at an input power of 15 dBm whereas 6 dBm for the Power amplifier

without feed forward linearizer circuit. The designed Power amplifier system with feed forward linearizer

had IMD3 suppression of 30dBc which is in appreciable range with improvement in 1dB compression

point.

0.5GHz - 1.5GHz Bandwidth 10W GaN HEMT RF Power Amplifier Design

With the current development in wireless communication technology, the need for a wide bandwith in RF power amplifier (RF PA) is an essential. In this paper, the design and simulation of 10W GaN HEMT wideband RF PA will be presented. The Source-Pull and Load-Pull technique was used to design the input and output matching network of the RF PA. From the simulation, the RF PA achieved a flat gain between 15dB to 17dB from 0.5GHz to 1.5GHz. At 1.5GHz, the drain efficiency is simulated to achieve 36% at the output power of 40 dBm while the power added efficiency (PAE) was found to be 28.2%.

K0536569

IOSR Journal of Electronics and Communication Engineering(IOSR-JECE) is an open access international journal that provides rapid publication (within a month) of articles in all areas of electronics and communication engineering and its applications. The journal welcomes publications of high quality papers on theoretical developments and practical applications in electronics and communication engineering. Original research papers, state-of-the-art reviews, and high quality technical notes are invited for publications.

A Novel Design of a Microstrip Microwave Power Amplifier for DCS Application ...

This paper presents a 1.80GHz class-A Microwave power amplifier (PA). The proposed power amplifier is designed with single-stage architecture. This power amplifier consists of a bipolar transistor and improved by Collector-Feedback Biasing fed with a single power supply. The aim of this work is to improve the performance of this amplifier by using simple stubs with 50Ω microstrip transmissions lines. The proposed PA is investigated and optimized by utilizing Advanced Design System (ADS) software. The simulation results show that the amplifier achieves a high power gain of 13dB, output power rise up to 21dBm and good impedances matching ;For the input reflection coefficient (S11) is below than - 46.39dB. Regarding the output reflection coefficient (S22) is below than -29.898dB, with an overall size of about 93 x 59mm². By the end; we find that this power amplifier offers an excellent performance for DCS applications.

What's hot (20)

Open Loop Control Of Series Parallel Resonant Converter

Open Loop Control Of Series Parallel Resonant Converter

Performance analysis of High Speed ADC using SR F/F

Performance analysis of High Speed ADC using SR F/F

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

Design of Low Power & High Speed Comparator with 0.18μm Technology for ADC Ap...

A Low Power, 8-Bit, 5MS/s Digital to Analog Converter for Successive Approxim...

A Low Power, 8-Bit, 5MS/s Digital to Analog Converter for Successive Approxim...

IRJET-Design of Capacitor Less LDO Regulator by using Cascode Compensation Te...

IRJET-Design of Capacitor Less LDO Regulator by using Cascode Compensation Te...

DESIGN OF HIGH EFFICIENCY TWO STAGE POWER AMPLIFIER IN 0.13UM RF CMOS TECHNOL...

DESIGN OF HIGH EFFICIENCY TWO STAGE POWER AMPLIFIER IN 0.13UM RF CMOS TECHNOL...

Double feedback technique for reduction of Noise LNA with gain enhancement

Double feedback technique for reduction of Noise LNA with gain enhancement

Design of a low-power compact CMOS variable gain amplifier for modern RF rece...

Design of a low-power compact CMOS variable gain amplifier for modern RF rece...

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

Design of a high frequency low voltage CMOS operational amplifier

Design of a high frequency low voltage CMOS operational amplifier

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

Alternative approach to design matching network for differential drive 2016

Alternative approach to design matching network for differential drive 2016

IRJET- Design of 4th Order Low Pass Filter using Memristive OP-AMPS

IRJET- Design of 4th Order Low Pass Filter using Memristive OP-AMPS

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

DESIGN OF 2.4 GHZ MMIC FEED FORWARD AMPLIFIER FOR WIRELESS APPLICATIONS

0.5GHz - 1.5GHz Bandwidth 10W GaN HEMT RF Power Amplifier Design

0.5GHz - 1.5GHz Bandwidth 10W GaN HEMT RF Power Amplifier Design

A Novel Design of a Microstrip Microwave Power Amplifier for DCS Application ...

A Novel Design of a Microstrip Microwave Power Amplifier for DCS Application ...

Similar to Rf power amplifiers for wireless communications ch10 6

Closed Loop Power Control of Grid Connected DG Units for Reducing Active Harm...

https://irjet.net/archives/V4/i8/IRJET-V4I8386.pdf

International Journal of Engineering and Science Invention (IJESI)

International Journal of Engineering and Science Invention (IJESI) is an international journal intended for professionals and researchers in all fields of computer science and electronics. IJESI publishes research articles and reviews within the whole field Engineering Science and Technology, new teaching methods, assessment, validation and the impact of new technologies and it will continue to provide information on the latest trends and developments in this ever-expanding subject. The publications of papers are selected through double peer reviewed to ensure originality, relevance, and readability. The articles published in our journal can be accessed online.

An analysis of pfc converter with high speed dynamic

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Analysis and design of single phase voltage-frequency converter with optimize...

Analysis and design of single phase voltage-frequency converter with optimize...International Journal of Power Electronics and Drive Systems

This paper proposes a new voltage frequency converter (VFC) that converts both voltage and frequency to the required level of voltage and frequency in low voltage networks used in various countries. The proposed converter could be used as a universal power supply for sensitive AC loads. The converter is composed of, input voltage and frequency detection circuitry, full bridge boost rectifier and a DC to AC inverter. In addition, to improve the feasibility and performance of the converter, synchronous reference based PI (SRFPI) controller is adopted, where the system behaves similar to a DC-DC converter. The parameter selection of PI controller is done using a recent optimisation technique called Lightning Search Algorithm (LSA). The simulation of VFC is conducted in MATLAB/Simulink environment. The simulation results shows that LSA based PI controller provides better output voltage regulation with respect to the reference value under various load and input conditions.Mi2420432050

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

A Review of Analysis and Modeling of Grid Connected Three Phase Multilevel Un...

https://www.irjet.net/archives/V4/i6/IRJET-V4I659.pdf

Phase Frequency Detector and Charge Pump for Low Jitter PLL Applications

In this paper a new technique is presented to improve the jitter performance of conventional phase frequency detectors by completely removing the unnecessary one-shot pulse. This technique uses a variable pulse-height circuit to control the unnecessary one-shot pulse height. In addition, a novel charge-pump circuit with perfect current-matching characteristics is used to improve the output jitter performance of conventional charge pumps. This circuit is composed of a pair of symmetrical pump circuits to obtain a good current matching. As a result, the proposed charge-pump circuit has perfect current-matching characteristics, wide output range, no glitch output current, and no jump output voltage. In order to verify such operation, circuit simulation is performed using 0.18 μm CMOS process parameters.

A Five – Level Integrated AC – DC Converter

This paper presents the implementation of a new five – level integrated AC – DC converter with high input power factor and reduced input current harmonics complied with IEC1000-3-2 harmonic standards for electrical equipments. The proposed topology is a combination of boost input power factor pre – regulator and five – level DC – DC converter. The single – stage PFC (SSPFC) approach used in this topology is an alternative solution to low – power and cost – effective applications.

Research Inventy : International Journal of Engineering and Science

Research Inventy : International Journal of Engineering and Science is published by the group of young academic and industrial researchers with 12 Issues per year. It is an online as well as print version open access journal that provides rapid publication (monthly) of articles in all areas of the subject such as: civil, mechanical, chemical, electronic and computer engineering as well as production and information technology. The Journal welcomes the submission of manuscripts that meet the general criteria of significance and scientific excellence. Papers will be published by rapid process within 20 days after acceptance and peer review process takes only 7 days. All articles published in Research Inventy will be peer-reviewed.

Modeling and analysis of pfc with appreciable voltage ripple to achieve fast ...

International peer-reviewed academic journals call for papers, http://www.iiste.org

Similar to Rf power amplifiers for wireless communications ch10 6 (20)

High Efficiency LDMOS Technology for UMTS base stations_journal

High Efficiency LDMOS Technology for UMTS base stations_journal

Closed Loop Power Control of Grid Connected DG Units for Reducing Active Harm...

Closed Loop Power Control of Grid Connected DG Units for Reducing Active Harm...

International Journal of Engineering and Science Invention (IJESI)

International Journal of Engineering and Science Invention (IJESI)

An analysis of pfc converter with high speed dynamic

An analysis of pfc converter with high speed dynamic

An analysis of pfc converter with high speed dynamic

An analysis of pfc converter with high speed dynamic

The effect of ripple steering on control loop stability for ac cm pfc boost c...

The effect of ripple steering on control loop stability for ac cm pfc boost c...

Analysis and design of single phase voltage-frequency converter with optimize...

Analysis and design of single phase voltage-frequency converter with optimize...

A Review of Analysis and Modeling of Grid Connected Three Phase Multilevel Un...

A Review of Analysis and Modeling of Grid Connected Three Phase Multilevel Un...

Phase Frequency Detector and Charge Pump for Low Jitter PLL Applications

Phase Frequency Detector and Charge Pump for Low Jitter PLL Applications

Research Inventy : International Journal of Engineering and Science

Research Inventy : International Journal of Engineering and Science

Modeling and analysis of pfc with appreciable voltage ripple to achieve fast ...

Modeling and analysis of pfc with appreciable voltage ripple to achieve fast ...

Recently uploaded

一比一原版(Bolton毕业证书)博尔顿大学毕业证成绩单如何办理

原件一模一样【微信:6496090 】【(Bolton毕业证书)博尔顿大学毕业证成绩单】【微信:6496090 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微6496090

【主营项目】

一.毕业证【q微6496090】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微6496090】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

Between Filth and Fortune- Urban Cattle Foraging Realities by Devi S Nair, An...

This study examines cattle rearing in urban and rural settings, focusing on milk production and consumption. By exploring a case in Ahmedabad, it highlights the challenges and processes in dairy farming across different environments, emphasising the need for sustainable practices and the essential role of milk in daily consumption.

PDF SubmissionDigital Marketing Institute in Noida

https://www.safalta.com/online-digital-marketing/advance-digital-marketing-training-in-noidaTop Digital Marketing Institute in Noida: Boost Your Career Fast

[3:29 am, 30/05/2024] +91 83818 43552: Safalta Digital Marketing Institute in Noida also provides advanced classes for individuals seeking to develop their expertise and skills in this field. These classes, led by industry experts with vast experience, focus on specific aspects of digital marketing such as advanced SEO strategies, sophisticated content creation techniques, and data-driven analytics.

Technoblade The Legacy of a Minecraft Legend.

Technoblade, born Alex on June 1, 1999, was a legendary Minecraft YouTuber known for his sharp wit and exceptional PvP skills. Starting his channel in 2013, he gained nearly 11 million subscribers. His private battle with metastatic sarcoma ended in June 2022, but his enduring legacy continues to inspire millions.

一比一原版(毕业证)长崎大学毕业证成绩单如何办理

一模一样【q/微:1954292140】【(毕业证)长崎大学毕业证成绩单Offer】【q/微:1954292140】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

【业务选择办理准则】

一、工作未确定,回国需先给父母、亲戚朋友看下文凭的情况,办理一份就读学校的毕业证【q/微:1954292140】文凭即可

二、回国进私企、外企、自己做生意的情况,这些单位是不查询毕业证真伪的,而且国内没有渠道去查询国外文凭的真假,也不需要提供真实教育部认证。鉴于此,办理一份毕业证【q/微:1954292140】即可

三、进国企,银行,事业单位,考公务员等等,这些单位是必需要提供真实教育部认证的,办理教育部认证所需资料众多且烦琐,所有材料您都必须提供原件,我们凭借丰富的经验,快捷的绿色通道帮您快速整合材料,让您少走弯路。

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

Design Thinking Design thinking Design thinking

browser_id=0805f5bf-ce9a-4428-95d6-d033e2e99357; country_code=HK; osano_consentmanager_uuid=e15f0d2d-abea-4bd1-8577-fd4496790f18; osano_consentmanager=jLf5tMmyGrJqqkCKKefFwIVpDtiqgmGXw27g5gYdfQpk4hOXYBfZCKCzPBWYdK8w1lcTqLap8QS67svOUbat03XkUWKpqKEsLCK3mjSUmA3OnMuRFuNcW9HVt3YeaJgOUXcJUn5WeIq8q9VtmrJKMuvXgOOyCNgJWMAZwoEMWDFkG3j7qcUcs1NPsqtUuw0j0wfj8i4zlaJfa3IvQPG_D4D260JFXkQhYznGXb5sE5mPs-APZIQtxPHmFwkJdDYoBoMM5i6BZTOE3CooiHLlsht3rOOPQg88XYMzui4zjk9McsqToNHwDRV6b9Kej7cm8wKYlnWd2VvhLptTLhhm5ZKtGgKGzvw1_typZRzwu9MKcBj0yTeYwGRJRAKuVn47zkhpHSgnz6D1l16vepyuyiQ8MPZIOh8c_uGbHMcyoaVTDaayQ8U8px9wRqFxUSyZEpQTa_fi5T-6Uz_R67Brn2PS-d4tvXLr66ldhAZ1Jf__4OIznZdrqvDR_Z2ebTeVTu5ATJ1DvLZ4i1BLFhcurWlu5l8T0-Jhw6DJ34hHUusbWzObZ3YFnj__0ei7tWJgFrkFO9CJagQ3viMmBxQ7AkTVJEHyjWU9; _fs_sample_user=false; _cookie_id=0a94bc58797e85f5de6c93345f64781e; __utma=186399478.1905777825.1717386827.1717386827.1717386827.1; __utmc=186399478; __utmz=186399478.1717386827.1.1.utmcsr=(direct)|utmccn=(direct)|utmcmd=(none); logged_in=MjUwNTA4MTg3--b7017508f246f17817fd3e608989a3ea5afca79b; _uv_id=30907880; __utmv=186399478.|1=member_type=FREE=1; __utmt=1; split=%7B%22connatix_player%22%3A%22control%22%7D; _li_dcdm_c=.slideshare.net; _lc2_fpi=064716c27ff8--01hze4afgcx42z2sfzncwg116f; _lc2_fpi_meta=%7B%22w%22%3A1717387476492%7D; cookie=579db3e3-4e1c-4ac9-a9db-002f2d678eef; cookie_cst=zix7LPQsHA%3D%3D; _lr_retry_request=true; _lr_env_src_ats=false; ccuid=70541430-c837-48de-9b38-b4f3df46fe15; ccsid=a9cca90f-eb12-4a61-b312-3155fe2cedc9; pbjs_fabrickId_cst=VyxHLMwsHQ%3D%3D; __qca=P0-718305261-1717387477147; _au_1d=AU1D-0100-001717387478-RZGCHPIP-HI28; cnx_userId=1a25f8b38d594f66bdfcd9b623574d7e; __gads=ID=b0c257cd8837a2d5:T=1717387477:RT=1717387477:S=ALNI_MZemOB79GYzmJy3MDitud8C8ts5nA; __gpi=UID=00000e3fd92e5908:T=1717387477:RT=1717387477:S=ALNI_MZR3uQlHjpZGt6pPAiR8bAmgQiNMw; __eoi=ID=120019e4653fcac0:T=1717387477:RT=1717387477:S=AA-Afja3ZyvegUx9PpJpyU3JRtKG; _ga=GA1.2.1905777825.1717386827; _gid=GA1.2.1124439812.1717387480; pbjs_fabrickId=%7B%22fabrickId%22%3A%22E1%3AZZkbPxuXzPC-yttqf7OyQwqyZ4d59gxkbK9Q9mAMU6KKtKk-zyILipMXIxtHYjde-k20DDHHi6M_4jJU4r9LAuwgRg_9_51CF7Sii2B_ST0%22%7D; flash=BAh7DEkiDHN1Y2Nlc3MGOgZFRjBJIgtub3RpY2UGOwBGMEkiDHdhcm5pbmcGOwBGMEkiDG1lc3NhZ2UGOwBGMEkiCmVycm9yBjsARjBJIg5wZXJtYW5lbnQGOwBGMEkiEW1vZGFsX25vdGljZQY7AEYw--f6b5339a8f734d46392574bf61fd69c472ec51d6; __utmb=186399478.31.7.1717387752666; _dd_s=rum=0&expire=1717388665794

Design Thinking Design thinking Design thinking

https://www.google.com/maps/d/view?mid=1deXTRaa0CGg1QvFHlnVvmlnp4FPtZ10&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=1BHv3gx5ZJJH3inU343hkNLpPQCv6KPo&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=1AfH4_M3zoT6_s93ASy0CeE8jovcHgik&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=19QktXHVSUwDqMFK3CcLocgXQ6bPz5b8&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=1w11lKJgVGX6rOP4J7J1PCJie86IWQVM&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=1kVcrH9p-f2MJdJ6voQGvC1P35jx-QZ8&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/view?mid=149RlyyVXCaY65ql-dLC2eZ1fsP01JN8&vomp=1&cid=mp&cv=RgEAcd5aUzg.en.

https://www.google.com/maps/d/view?mid=1jtRQWjvBCrEFjsvsEIDLcLy-VAyeVHY&vomp=1&cid=mp&cv=RgEAcd5aUzg.en.

https://www.google.com/maps/d/view?mid=1L5nx5uSpbzk3VDdxpuIX8TzOM2ZUA4E&vomp=1&cid=mp&cv=RgEAcd5aUzg.en.

https://www.google.com/maps/d/view?mid=1L5nx5uSpbzk3VDdxpuIX8TzOM2ZUA4E&vomp=1&cid=mp&cv=RgEAcd5aUzg.en.

https://www.google.com/maps/d/view?mid=1SudZO_xD1NsTUsnvMCZtPgAHMpZCIaI&ll=22.39653737546966%2C114.10949749999997&z=12

https://www.google.com/maps/d/view?mid=1xl8SHD1eLjf4PbIhmeodTYJF4dPX4oo&ll=22.39653737546966%2C114.10949749999997&z=12

https://www.google.com/maps/d/view?mid=1LikThZPD8S6wG37Lnt1VWYWjBZ4IL_0&ll=22.39653737546966%2C114.10949749999997&z=12

https://www.google.com/maps/d/view?mid=1xl8SHD1eLjf4PbIhmeodTYJF4dPX4oo&ll=22.39653737546966%2C114.10949749999997&z=12

https://www.google.com/maps/d/view?mid=149RlyyVXCaY65ql-dLC2eZ1fsP01JN8&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1m72ggtGeWoLJnHpU_3f7LZ-HUQv2Mzk&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1F2NYKICN0Wb27ewNUsrV2BB18wvP7GQ&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1eKeVRSRhyfqRrG0F9kQiD5yp0cGt4WQ&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1g6bB3w3qRleJoX2Psz1zPggAUxwnCdU&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1sGPo5jqk_loy-a1es93BLxTKvRXmxt4&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1vaAt-Vy9I85rMukOc65MQmt3SoNBpNQ&ll=22.396537375469673%2C114.10949749999997&z=11

https://www.google.com/maps/d/viewer?mid=1r62eAttQMFxuaZeIVC_YF_aqPADXnf8&ll=22.396537375469673%2C114.10949749999997&z=11

EASY TUTORIAL OF HOW TO USE CAPCUT BY: FEBLESS HERNANE

CapCut is an easy-to-use video editing app perfect for beginners. To start, download and open CapCut on your phone. Tap "New Project" and select the videos or photos you want to edit. You can trim clips by dragging the edges, add text by tapping "Text," and include music by selecting "Audio." Enhance your video with filters and effects from the "Effects" menu. When you're happy with your video, tap the export button to save and share it. CapCut makes video editing simple and fun for everyone!

LORRAINE ANDREI_LEQUIGAN_HOW TO USE TRELLO

These presentations might provide detailed guidance on utilizing the Trello app effectively.

一比一原版(Columbia毕业证)哥伦比亚大学毕业证如何办理

Columbia毕业证offer【微信95270640】☀《哥伦比亚大学毕业证购买》Q微信95270640《Columbia毕业证文凭补》文凭、本科、硕士、研究生学历都可以做,留信认证的作用:

1:该专业认证可证明留学生真实留学身份。

2:同时对留学生所学专业等级给予评定。

3:国家专业人才认证中心颁发入库证书

4:这个入网证书并且可以归档到地方

5:凡是获得留信网入网的信息将会逐步更新到个人身份内,将在网内查询个人身份证信息后,同步读取人才网入库信息。

6:个人职称评审加20分。

7:个人信誉贷款加10分。

8:在国家人才网主办的全国网络招聘大会中纳入资料,供国家500强等高端企业选择人才《文凭Columbia毕业证书原版制作Columbia成绩单》仿制Columbia毕业证成绩单哥伦比亚大学学位证书pdf电子图》。

办国外哥伦比亚大学哥伦比亚大学毕业证录取书教育部学历学位认证留信认证大使馆认证留学回国人员证明修改成绩单信封申请学校offer录取通知书在读证明offer letter。

快速办理高仿国外毕业证成绩单:

1哥伦比亚大学毕业证+成绩单+留学回国人员证明+教育部学历认证(全套留学回国必备证明材料给父母及亲朋好友一份完美交代);

2雅思成绩单托福成绩单OFFER在读证明等留学相关材料(申请学校转学甚至是申请工签都可以用到)。

3.毕业证 #成绩单等全套材料从防伪到印刷从水印到钢印烫金高精仿度跟学校原版100%相同。

专业服务请勿犹豫联系我!联系人微信号:95270640诚招代理:本公司诚聘当地代理人员如果你有业余时间有兴趣就请联系我们。

国外哥伦比亚大学哥伦比亚大学毕业证录取书办理过程:

1客户提供办理信息:姓名生日专业学位毕业时间等(如信息不确定可以咨询顾问:我们有专业老师帮你查询);

2开始安排制作毕业证成绩单电子图;

3毕业证成绩单电子版做好以后发送给您确认;

4毕业证成绩单电子版您确认信息无误之后安排制作成品;

5成品做好拍照或者视频给您确认;

6快递给客户(国内顺丰国外DHLUPS等快读邮寄)。我们的亲人生我养我的父母您们的年迈的苍老换来了我们新一代的新鲜与活力无论我们在哪里父母对我们的爱和思念为我们的生命增加了光彩给予我们自由追求的力量生活的力量我们也不忘感恩正因为这股感恩的线牵着我们使我们在一年的结束时刻义无反顾的踏上了回家的旅途人们常说父母恩最难回报愿我能以当年爸爸妈妈对待小时候的我们那样耐心温柔地对待我将渐渐老去的父母体谅他们以反哺之心奉敬父母以感恩之心孝顺父母哪怕只为父母换洗的

一比一原版(UAL毕业证书)伦敦艺术大学毕业证成绩单如何办理

原件一模一样【微信:6496090 】【(UAL毕业证书)伦敦艺术大学毕业证成绩单】【微信:6496090 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微6496090

【主营项目】

一.毕业证【q微6496090】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微6496090】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

Can AI do good? at 'offtheCanvas' India HCI prelude

Invited talk at 'offtheCanvas' IndiaHCI prelude, 29th June 2024.

https://www.alandix.com/academic/talks/offtheCanvas-IndiaHCI2024/

The world is being changed fundamentally by AI and we are constantly faced with newspaper headlines about its harmful effects. However, there is also the potential to both ameliorate theses harms and use the new abilities of AI to transform society for the good. Can you make the difference?

Mohannad Abdullah portfolio _ V2 _22-24

Mohannad Abdullah

Architecture | Interior Design

portoflio_V2_22-24

Connect Conference 2022: Passive House - Economic and Environmental Solution...

Passive House: The Economic and Environmental Solution for Sustainable Real Estate. Lecture by Tim Eian of TE Studio Passive House Design in November 2022 in Minneapolis.

- The Built Environment

- Let's imagine the perfect building

- The Passive House standard

- Why Passive House targets

- Clean Energy Plans?!

- How does Passive House compare and fit in?

- The business case for Passive House real estate

- Tools to quantify the value of Passive House

- What can I do?

- Resources

Transforming Brand Perception and Boosting Profitability

In today's digital era, the dynamics of brand perception, consumer behavior, and profitability have been profoundly reshaped by the synergy of branding, social media, and website design. This research paper investigates the transformative power of these elements in influencing how individuals perceive brands and products and how this transformation can be harnessed to drive sales and profitability for businesses.

Through an exploration of brand psychology and consumer behavior, this study sheds light on the intricate ways in which effective branding strategies, strategic social media engagement, and user-centric website design contribute to altering consumers' perceptions. We delve into the principles that underlie successful brand transformations, examining how visual identity, messaging, and storytelling can captivate and resonate with target audiences.

Methodologically, this research employs a comprehensive approach, combining qualitative and quantitative analyses. Real-world case studies illustrate the impact of branding, social media campaigns, and website redesigns on consumer perception, sales figures, and profitability. We assess the various metrics, including brand awareness, customer engagement, conversion rates, and revenue growth, to measure the effectiveness of these strategies.

The results underscore the pivotal role of cohesive branding, social media influence, and website usability in shaping positive brand perceptions, influencing consumer decisions, and ultimately bolstering sales and profitability. This paper provides actionable insights and strategic recommendations for businesses seeking to leverage branding, social media, and website design as potent tools to enhance their market position and financial success.

一比一原版(Brunel毕业证书)布鲁内尔大学毕业证成绩单如何办理

原件一模一样【微信:6496090 】【(Brunel毕业证书)布鲁内尔大学毕业证成绩单】【微信:6496090 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微6496090

【主营项目】

一.毕业证【q微6496090】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微6496090】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

原版定做(penn毕业证书)美国宾夕法尼亚大学毕业证文凭学历证书原版一模一样

原版纸张【微信:741003700 】【(penn毕业证书)美国宾夕法尼亚大学毕业证、文凭学历证书】【微信:741003700 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原海外各大学 Bachelor Diploma degree, Master Degree Diploma

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微741003700

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

Book Formatting: Quality Control Checks for Designers

This presentation was made to help designers who work in publishing houses or format books for printing ensure quality.

Quality control is vital to every industry. This is why every department in a company need create a method they use in ensuring quality. This, perhaps, will not only improve the quality of products and bring errors to the barest minimum, but take it to a near perfect finish.

It is beyond a moot point that a good book will somewhat be judged by its cover, but the content of the book remains king. No matter how beautiful the cover, if the quality of writing or presentation is off, that will be a reason for readers not to come back to the book or recommend it.

So, this presentation points designers to some important things that may be missed by an editor that they could eventually discover and call the attention of the editor.

一比一原版(NCL毕业证书)纽卡斯尔大学毕业证成绩单如何办理

学校原件一模一样【微信:6496090 】【(NCL毕业证书)纽卡斯尔大学毕业证成绩单】【微信:6496090 】学位证,留信认证(真实可查,永久存档)原件一模一样纸张工艺/offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微6496090

【主营项目】

一.毕业证【q微6496090】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微6496090】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

办理(NCL毕业证书)纽卡斯尔大学毕业证【微信:6496090 】外观非常简单,由纸质材料制成,上面印有校徽、校名、毕业生姓名、专业等信息。

办理(NCL毕业证书)纽卡斯尔大学毕业证【微信:6496090 】格式相对统一,各专业都有相应的模板。通常包括以下部分:

校徽:象征着学校的荣誉和传承。

校名:学校英文全称

授予学位:本部分将注明获得的具体学位名称。

毕业生姓名:这是最重要的信息之一,标志着该证书是由特定人员获得的。

颁发日期:这是毕业正式生效的时间,也代表着毕业生学业的结束。

其他信息:根据不同的专业和学位,可能会有一些特定的信息或章节。

办理(NCL毕业证书)纽卡斯尔大学毕业证【微信:6496090 】价值很高,需要妥善保管。一般来说,应放置在安全、干燥、防潮的地方,避免长时间暴露在阳光下。如需使用,最好使用复印件而不是原件,以免丢失。

综上所述,办理(NCL毕业证书)纽卡斯尔大学毕业证【微信:6496090 】是证明身份和学历的高价值文件。外观简单庄重,格式统一,包括重要的个人信息和发布日期。对持有人来说,妥善保管是非常重要的。

一比一原版(UNUK毕业证书)诺丁汉大学毕业证如何办理

学校原件一模一样【微信:6496090 】【(UNUK毕业证书)诺丁汉大学毕业证成绩单】【微信:6496090 】学位证,留信认证(真实可查,永久存档)原件一模一样纸张工艺/offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微6496090

【主营项目】

一.毕业证【q微6496090】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微6496090】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

办理(UNUK毕业证书)诺丁汉大学毕业证【微信:6496090 】外观非常简单,由纸质材料制成,上面印有校徽、校名、毕业生姓名、专业等信息。

办理(UNUK毕业证书)诺丁汉大学毕业证【微信:6496090 】格式相对统一,各专业都有相应的模板。通常包括以下部分:

校徽:象征着学校的荣誉和传承。

校名:学校英文全称

授予学位:本部分将注明获得的具体学位名称。

毕业生姓名:这是最重要的信息之一,标志着该证书是由特定人员获得的。

颁发日期:这是毕业正式生效的时间,也代表着毕业生学业的结束。

其他信息:根据不同的专业和学位,可能会有一些特定的信息或章节。

办理(UNUK毕业证书)诺丁汉大学毕业证【微信:6496090 】价值很高,需要妥善保管。一般来说,应放置在安全、干燥、防潮的地方,避免长时间暴露在阳光下。如需使用,最好使用复印件而不是原件,以免丢失。

综上所述,办理(UNUK毕业证书)诺丁汉大学毕业证【微信:6496090 】是证明身份和学历的高价值文件。外观简单庄重,格式统一,包括重要的个人信息和发布日期。对持有人来说,妥善保管是非常重要的。

Recently uploaded (20)

Between Filth and Fortune- Urban Cattle Foraging Realities by Devi S Nair, An...

Between Filth and Fortune- Urban Cattle Foraging Realities by Devi S Nair, An...

PDF SubmissionDigital Marketing Institute in Noida

PDF SubmissionDigital Marketing Institute in Noida

EASY TUTORIAL OF HOW TO USE CAPCUT BY: FEBLESS HERNANE

EASY TUTORIAL OF HOW TO USE CAPCUT BY: FEBLESS HERNANE

Can AI do good? at 'offtheCanvas' India HCI prelude

Can AI do good? at 'offtheCanvas' India HCI prelude

Connect Conference 2022: Passive House - Economic and Environmental Solution...

Connect Conference 2022: Passive House - Economic and Environmental Solution...

Transforming Brand Perception and Boosting Profitability

Transforming Brand Perception and Boosting Profitability

Book Formatting: Quality Control Checks for Designers

Book Formatting: Quality Control Checks for Designers

Rf power amplifiers for wireless communications ch10 6

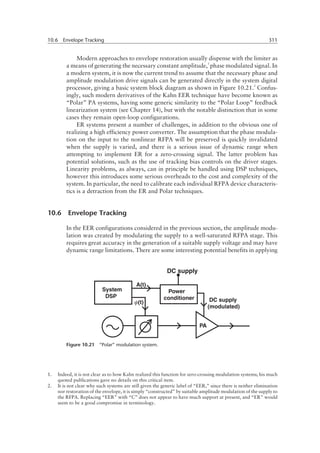

- 1. Modern approaches to envelope restoration usually dispense with the limiter as a means of generating the necessary constant amplitude, 1 phase modulated signal. In a modern system, it is now the current trend to assume that the necessary phase and amplitude modulation drive signals can be generated directly in the system digital processor, giving a basic system block diagram as shown in Figure 10.21.2 Confus- ingly, such modern derivatives of the Kahn EER technique have become known as “Polar” PA systems, having some generic similarity to the “Polar Loop” feedback linearization system (see Chapter 14), but with the notable distinction that in some cases they remain open-loop configurations. ER systems present a number of challenges, in addition to the obvious one of realizing a high efficiency power converter. The assumption that the phase modula- tion on the input to the nonlinear RFPA will be preserved is quickly invalidated when the supply is varied, and there is a serious issue of dynamic range when attempting to implement ER for a zero-crossing signal. The latter problem has potential solutions, such as the use of tracking bias controls on the driver stages. Linearity problems, as always, can in principle be handled using DSP techniques, however this introduces some serious overheads to the cost and complexity of the system. In particular, the need to calibrate each individual RFPA device characteris- tics is a detraction from the ER and Polar techniques. 10.6 Envelope Tracking In the EER configurations considered in the previous section, the amplitude modu- lation was created by modulating the supply to a well-saturated RFPA stage. This requires great accuracy in the generation of a suitable supply voltage and may have dynamic range limitations. There are some interesting potential benefits in applying 10.6 Envelope Tracking 311 Figure 10.21 “Polar” modulation system. 1. Indeed, it is not clear as to how Kahn realized this function for zero-crossing modulation systems; his much quoted publications gave no details on this critical item. 2. It is not clear why such systems are still given the generic label of “EER,” since there is neither elimination nor restoration of the envelope, it is simply “constructed” by suitable amplitude modulation of the supply to the RFPA. Replacing “EER” with “C” does not appear to have much support at present, and “ER” would seem to be a good compromise in terminology.

- 2. a similar envelope-derived modulation to the supply voltage of a conventional linear RF amplifier. Such a technique is generally termed “Envelope Tracking,” or “ET,” and is shown schematically in Figure 10.22. Recalling the analysis of a conventional Class B amplifier (Figure 10.1), we have already seen that if the RF load resistor is decreased in inverse proportion to increas- ing drive voltage amplitude, the efficiency remains constant at its maximum value while the power increases as the square root of the drive power; this is an important mode of dynamic behavior in the Doherty amplifier (Section 10.2). An alternative, and considerably simpler, scenario is that the load resistor remains fixed and the supply voltage is increased in proportion to the increasing drive voltage. In this case, maximum efficiency is maintained (due to full rail-to-rail voltage swing) and the output power increases linearly with input drive power. This process can be contin- ued down to a selected point on the lower side, and up to a point where the RF swing reaches breakdown level. In this manner, maximum efficiency can be maintained over a wide linear power range. One of the appealing aspects of this technique is that the modulation control voltage does not have to replicate the signal envelope with great accuracy, as is the case in the ER process. For example, the supply voltage could be tracked for just the upper few dB of the signal envelope range; this would then show an overall PBO effi- ciency characteristic somewhat comparable to a Doherty PA. The still-present chal- lenge of the tracking power converter can also be further reduced by the use of a power supply having two or more discrete switched output voltage levels. Problems of dynamic range, particularly in zero-crossing signal environments, are essentially eliminated by allowing for normal linear operation at a reduced supply voltage in the small signal regime. An additional attraction of ET is that the efficiency enhance- ment process is completely decoupled 3 from the RF matching. This is in contrast to the Doherty and Chireix configurations, which depend heavily for their operation on resonant RF circuit elements. It is instructive to consider a simple case, where two supply voltages are avail- able, as shown in Figure 10.23. The supply switch can, in principle, be realized using low cost and readily available semiconductors, which for envelope speeds in the MHz range do not have to be exceptionally fast, by modern standards. The drive signal to the switch would conventionally be derived by using an envelope detector 312 Efficiency Enhancement Techniques RF IN DC RF OUT Pwr. cond Figure 10.22 Envelope Tracking (“ET”) RF PA system. 3. Both literally and metaphorically; the physical integration of power converter and RFPA circuitry is one of the less publicized challenges in implementing ER systems.

- 3. and a threshold circuit which sets the level at which the switch was activated. A modern implementation would probably use a drive signal generated by the system DSP, which could conveniently be time-synchronized with appropriate pre- distortion of the input RF signal. This will include necessary compensation for the small changes in gain and phase in the RFPA as the supply is switched. The “break- point,” or envelope level at which the supply is switched, is clearly an important design choice. This choice will have an optimum value, dependent on the statistics of the signal environment. As with the selection of the breakpoint in a Doherty PA, the intuitive choice would be to set the lower voltage to switch in at the mean power level, the higher supply being used up to the peak power. The efficiency characteris- tic shown in Figure 10.24 assumes that the PA follows the ideal Class B PBO/effi- ciency characteristic for each supply voltage setting, reaching a maximum value of 70% at the onset of envelope clipping in each case. In order to evaluate the impact of such a characteristic in a specific signal envi- ronment, it is necessary to generate a representative signal burst and evaluate the average efficiency. This process can be repeated for various breakpoint and PEP backoff settings. For example, Figure 10.25 shows the results from performing this exercise for a two-level supply voltage on an EDGE signal. The average efficiency 10.6 Envelope Tracking 313 RF IN Switch drive DC RF OUT DC-DC conv. Figure 10.23 ET System using a two-level switched supply. 100 50 0 -10 dB-20 dB Pmax Efficiency (%) Output power backoff (dB) Vss Vss/2Vss/3 Figure 10.24 PBO-Efficiency characteristic for two-level switched ET system.

- 4. for the two-level supply switch is plotted for a range of breakpoint values. It is clear that a simple two-level switch, in this signal environment, can give a useful increase in efficiency (53.5% at optimum break point) in comparison to a standard Class B PA (45.3%), but falls significantly short of the Doherty PA result for the same signal environment (60.3%). In the case of an EDGE signal, it will in practice be necessary to back the PEP level down from the clipping point in order to obtain acceptable ACP performance, this will reduce all of the efficiency results by a similar factor. The efficiency gains in Figure 10.25 seem to deliver somewhat less than the PBO effi- ciency curves might suggest. The returns are, however, quite critically dependent on the signal environment. Some further details of the method used to perform the effi- ciency computations contained in Figure 10.25, and some more simulation results, will be presented in Section 10.10. As is customary when promoting efficiency enhancement techniques, little has been said about the possible effects of the technique on the PA linearity. As far as envelope tracking is concerned, this has to be raised as a potentially serious issue. The next chapter in this book, Chapter 11, is largely devoted to minimizing the harmful effects of small amounts of unintended modulation on the supply voltage to an RFPA. Clearly, when it is proposed that this same supply voltage be intentionally yanked around over most of its allowable range in order to improve the efficiency, questions about linearity have to be addressed. The standard answer, as always in the modern era, is that DSP will save the day. The gain and phase variations which the tracking will create can in principle be characterized and compensated by suit- able adjustment (DPD) to the input signal. But there can be little doubt that the large supply variations will make the DPD task more challenging. 10.7 Power Converters for EER and ET The implementation of a high efficiency, broadband power converter design for EER and ET implementation in RFPAs has been the focus of much research activity 314 Efficiency Enhancement Techniques Break point (normalized) Efficiency (%) 100 50 0 0 0.5 1.0 Doherty (6 dB breakpoint) Figure 10.25 Average efficiency for EDGE signal, Class B PA with switched voltage supply; (switch break point plotted as x-axis). Doherty PA efficiency shown for standard 6 dB break point.