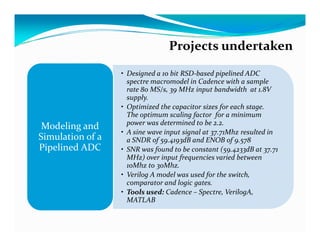

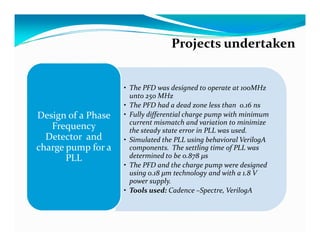

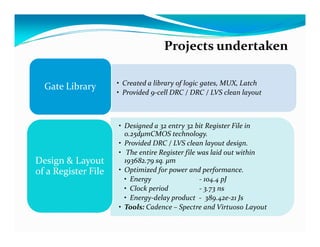

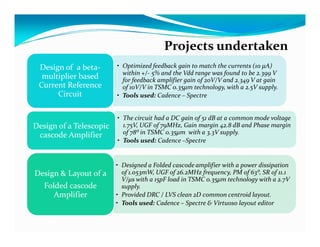

Sriram Sundararajah's professional profile includes a Master's degree in Electrical Engineering from Arizona State University and a Bachelor's degree in Electronics & Communication Engineering from Anna University, India. He has worked as a volunteer research assistant at ASU and as an intern at Foveon, Inc. His previous experience includes working as an assistant systems engineer at Tata Consultancy Services. His projects include designing and simulating pipelined ADCs, PLLs, current references, and amplifiers using Cadence tools.