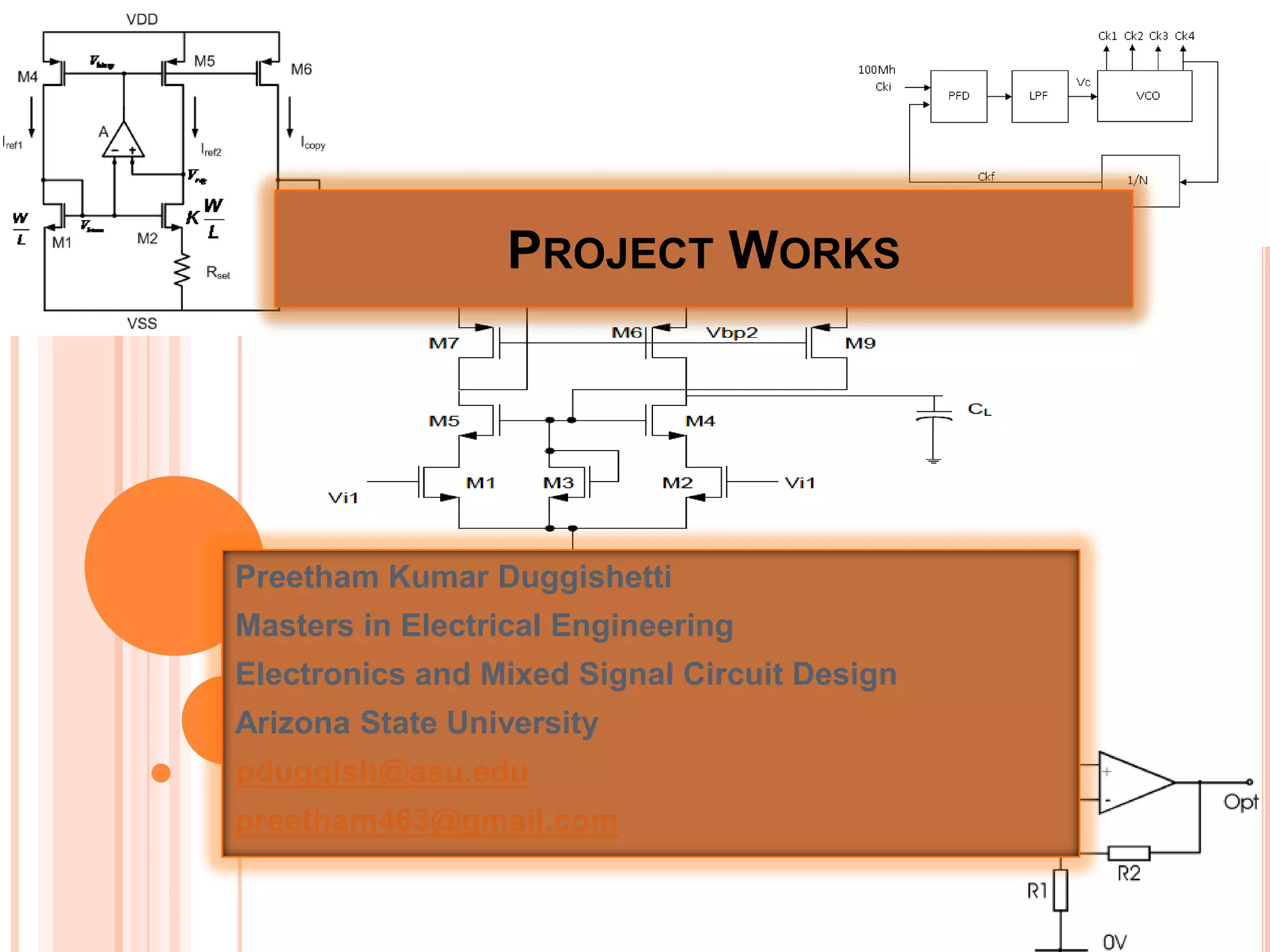

The document outlines Preetham Kumar Duggishetti's Masters projects in electrical engineering focusing on circuit design, including projects developing a Phase Locked Loop at 1.6GHz, a low power 32-bit ALU, an oversampling Sigma Delta ADC for WLAN systems, and more. The projects involved designing circuits in Cadence and developing behavioral models in VerilogA and MATLAB to meet various power, speed, and dynamic range requirements. Preetham's work demonstrates expertise in analog and mixed-signal circuit design.