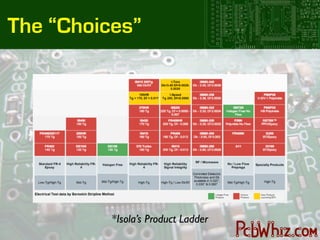

The document provides an overview of PCB laminates, including essential components like core, pre-preg, and foil, alongside critical properties and types such as fr-4 and modified epoxy systems. It highlights the differences between lead and lead-free assemblies and categorizes PCB types based on layer count and performance specifications. Key considerations for material qualification and manufacturing challenges are also discussed, emphasizing the need for careful vendor and customer communications.