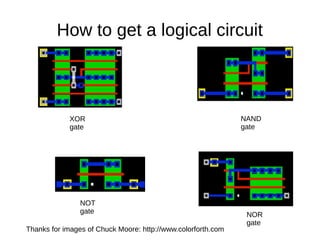

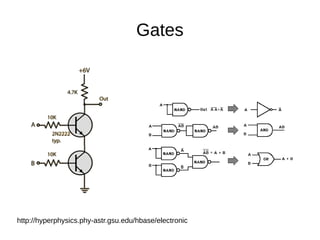

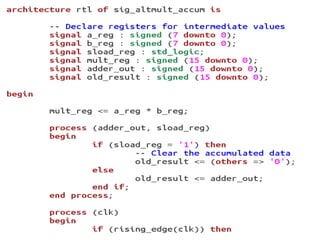

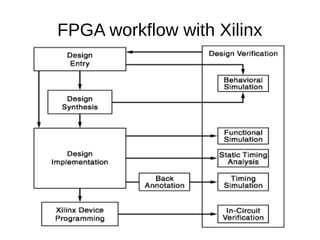

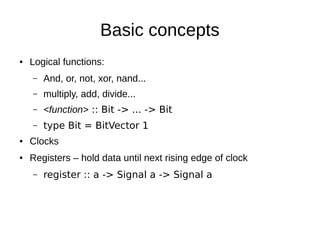

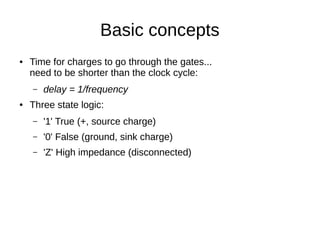

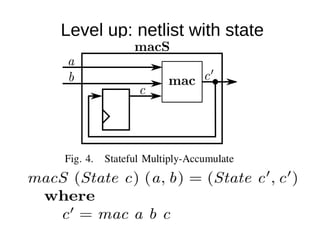

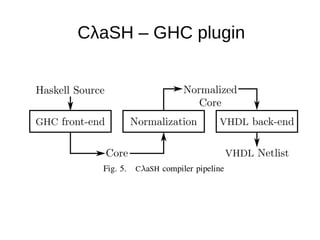

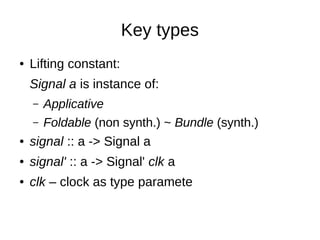

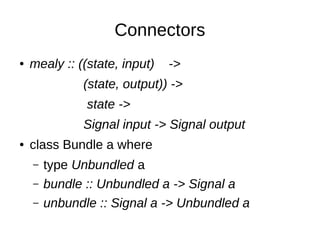

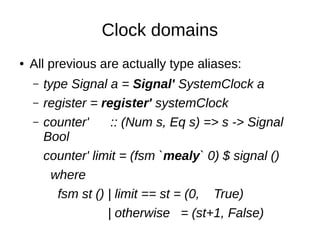

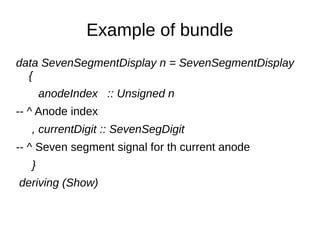

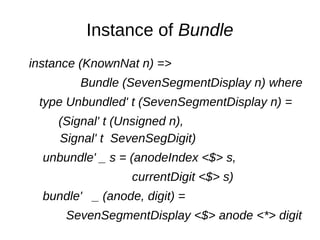

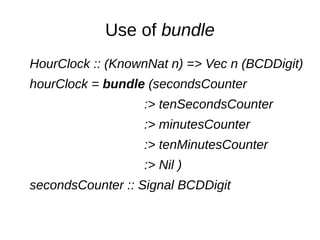

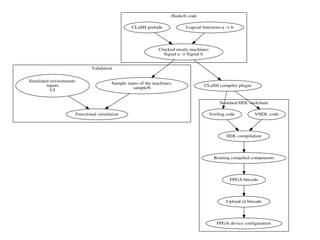

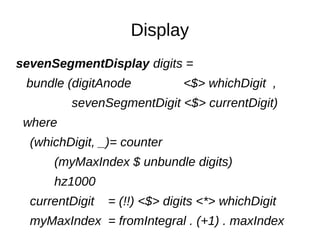

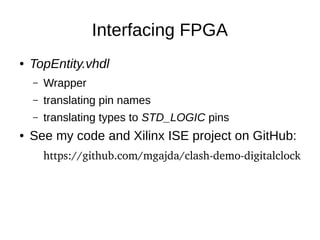

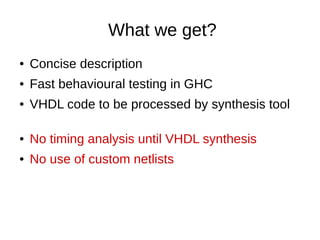

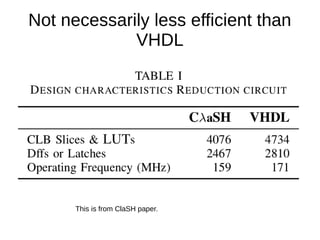

This document summarizes a Haskell.SG MeetUp presentation about using the ClaSH compiler plugin to compile Haskell code describing digital logic circuits into VHDL for implementation on FPGAs. The presentation introduced basic digital logic concepts like gates, clocks, registers and three-state logic. It described how ClaSH allows describing circuits as Haskell functions and mealy machines, and bundles signals for simulation and compilation to VHDL. Example code was shown for a seven segment display driven by a counter circuit. The workflow allows behavioral testing in Haskell and generation of VHDL for synthesis, without necessarily being less efficient than hand-coding in VHDL.