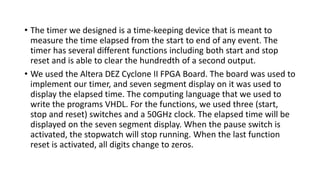

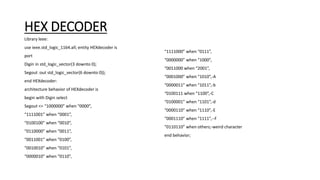

The timer project uses a FPGA board to display elapsed time on a seven segment display. It is implemented using VHDL with hardware blocks that include a BCD counter, HEX decoder, and finite state machine (FSM). The BCD counter counts the time in binary coded decimal format. The HEX decoder converts the BCD output to the hexadecimal display format for the seven segment display. The FSM controls the different states of the timer for the start, stop, and reset functions using the button inputs.