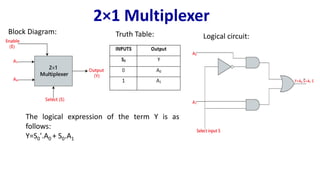

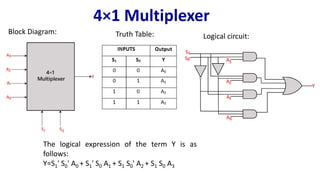

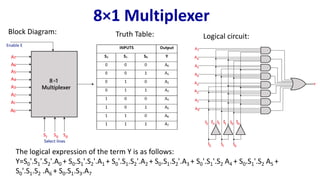

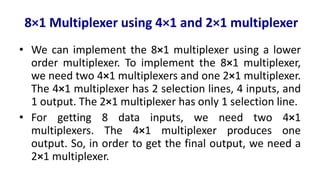

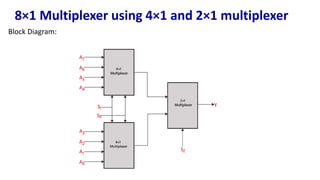

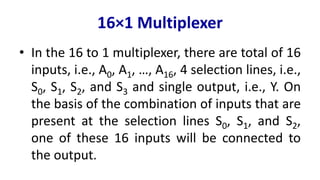

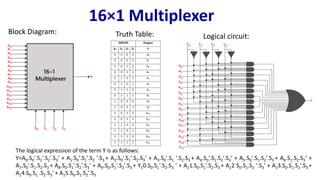

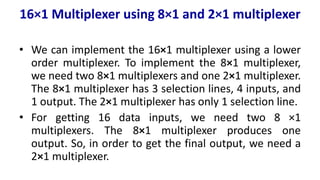

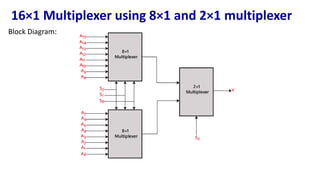

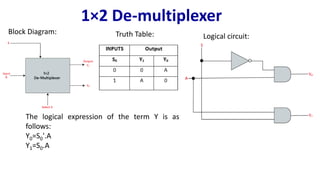

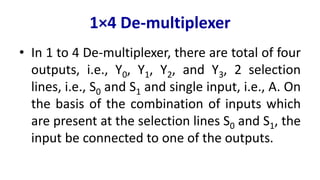

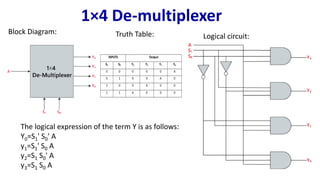

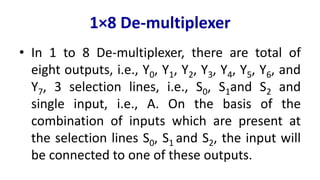

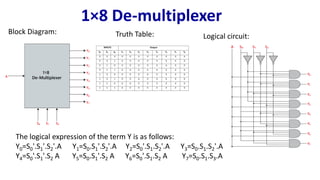

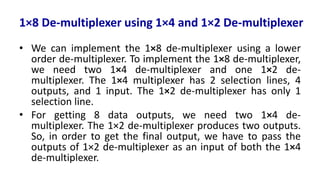

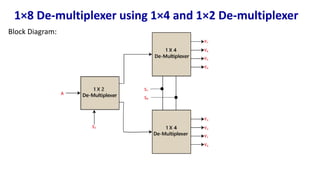

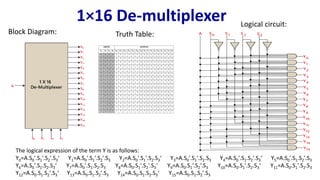

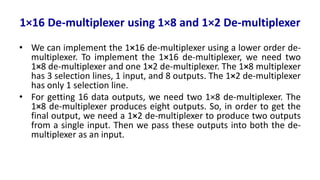

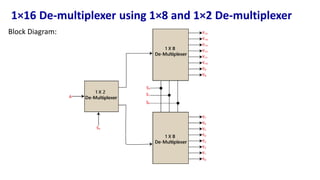

The document describes multiplexer and demultiplexer circuits, detailing their definitions, functionalities, and various types, including 2×1, 4×1, 8×1, and 16×1 multiplexers, as well as corresponding de-multiplexers. Each type's structure is explained along with truth tables and logical expressions. The document also covers how higher-order multiplexers can be implemented using lower-order multiplexers.