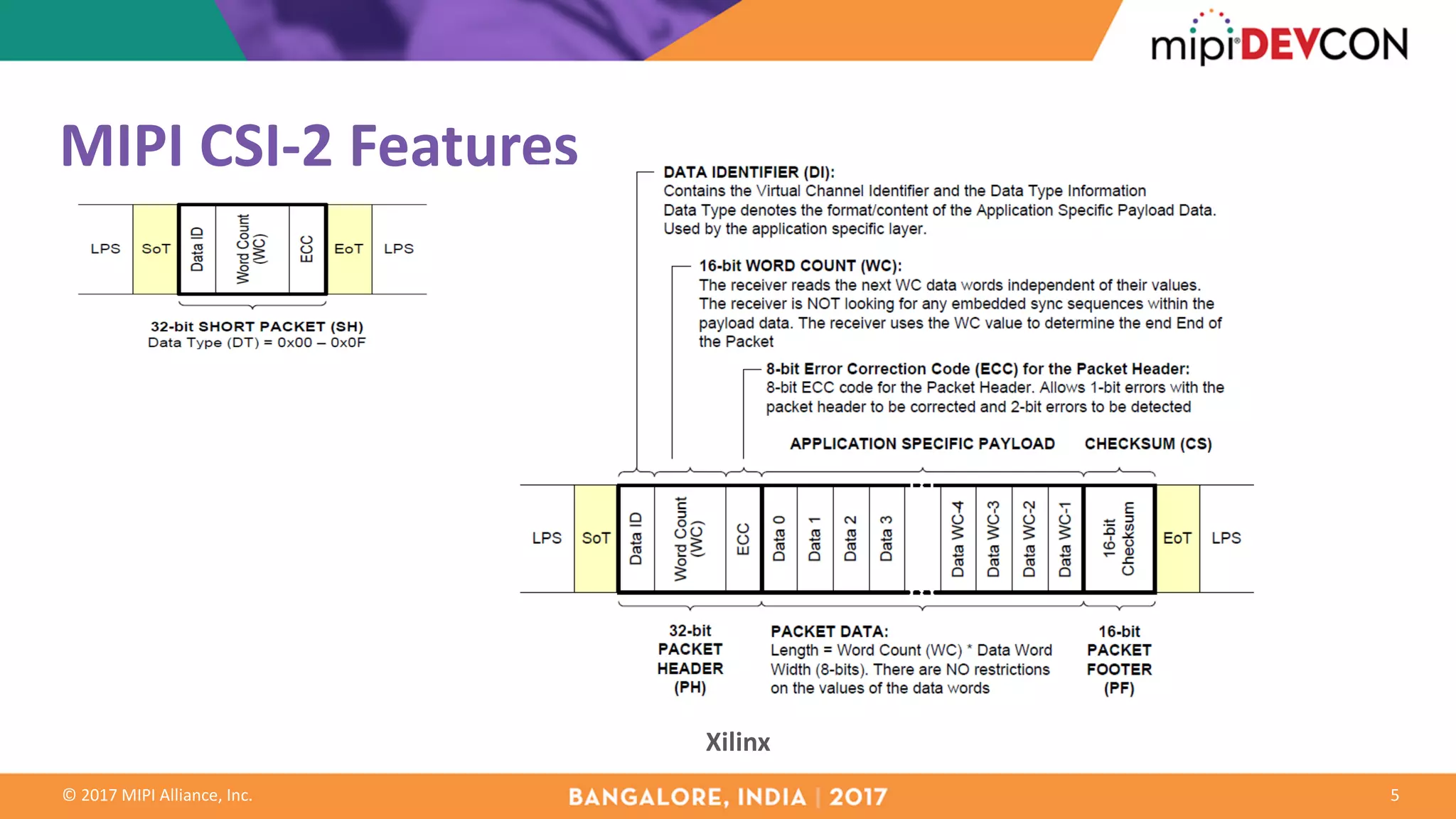

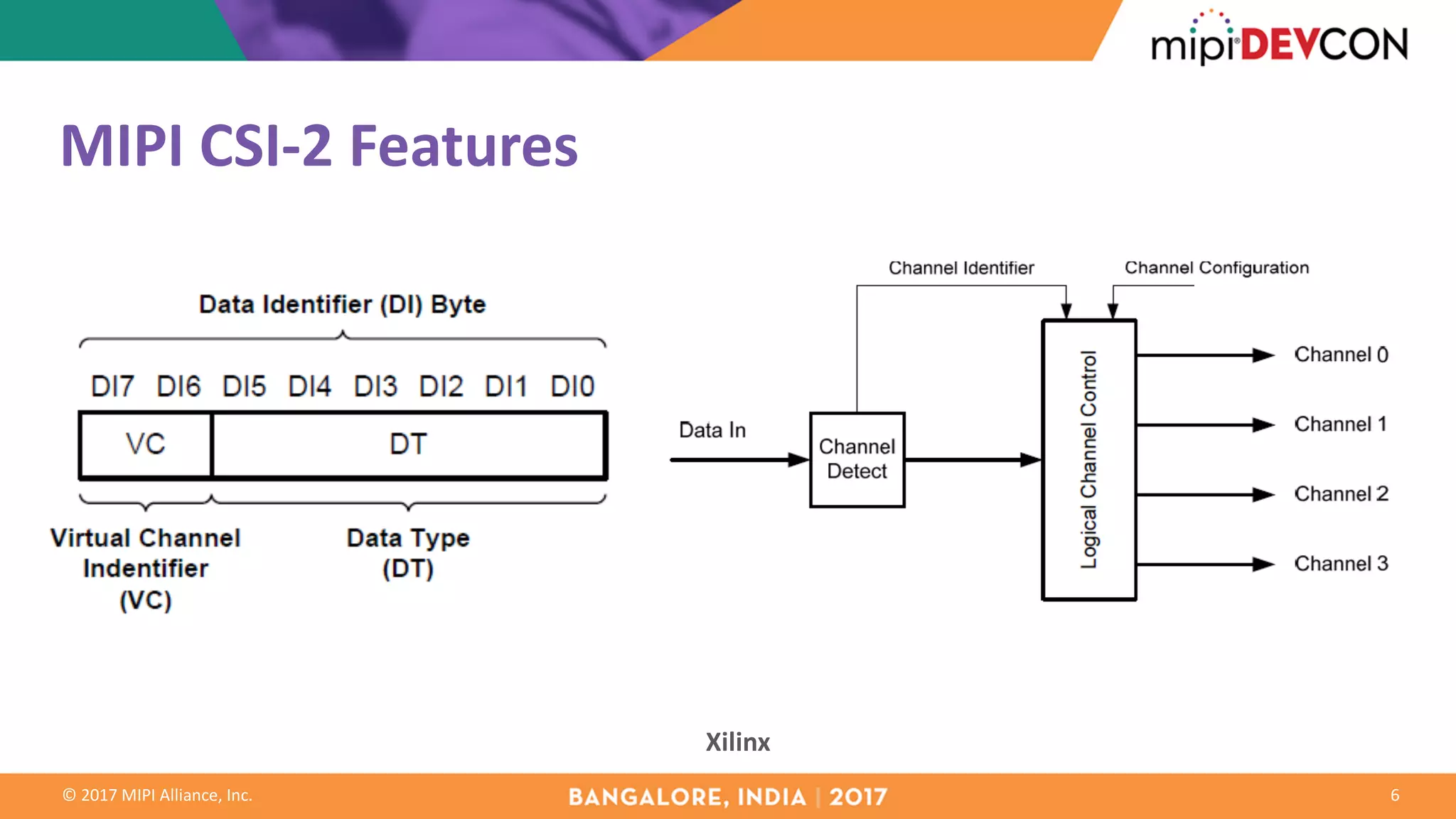

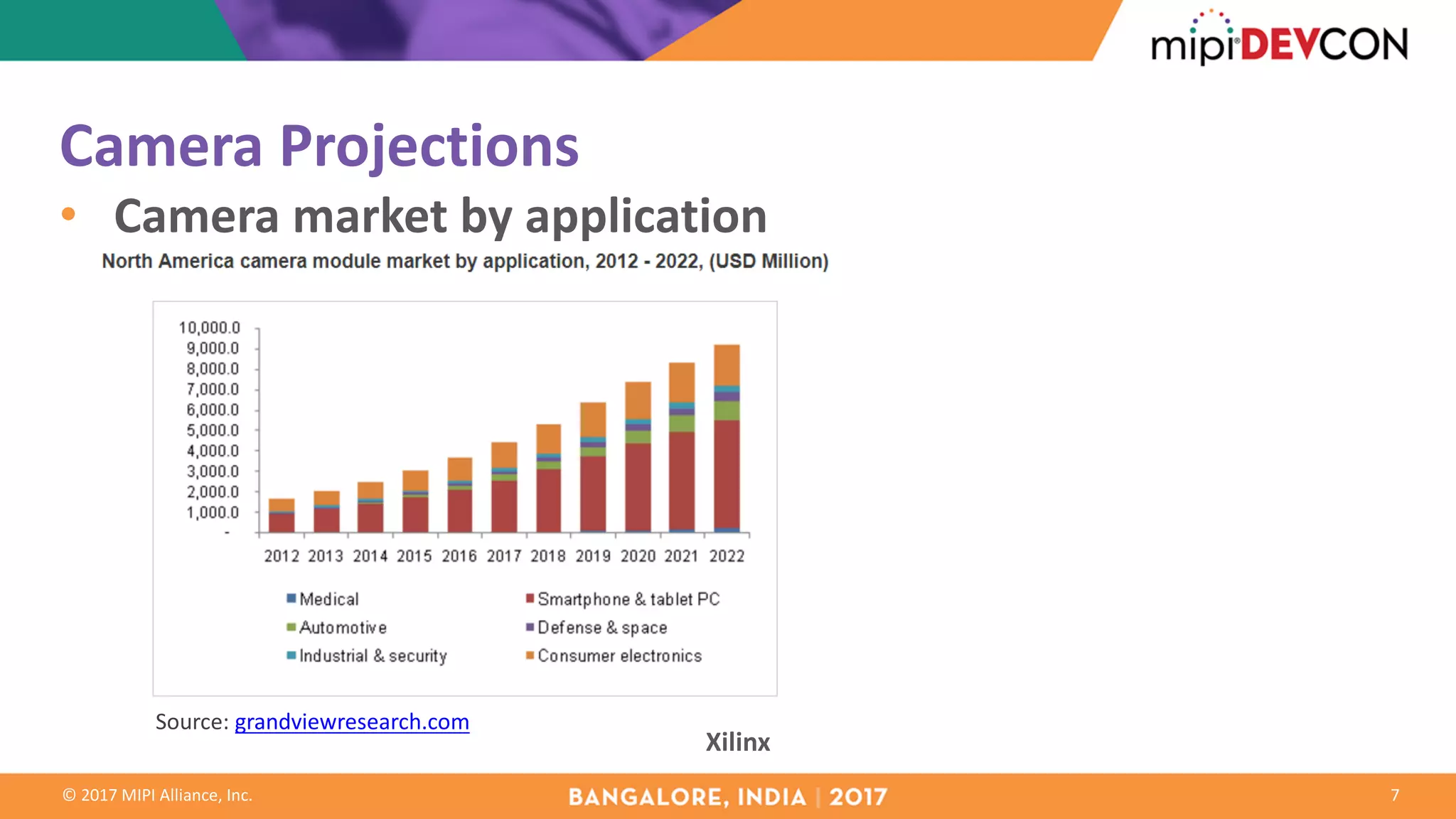

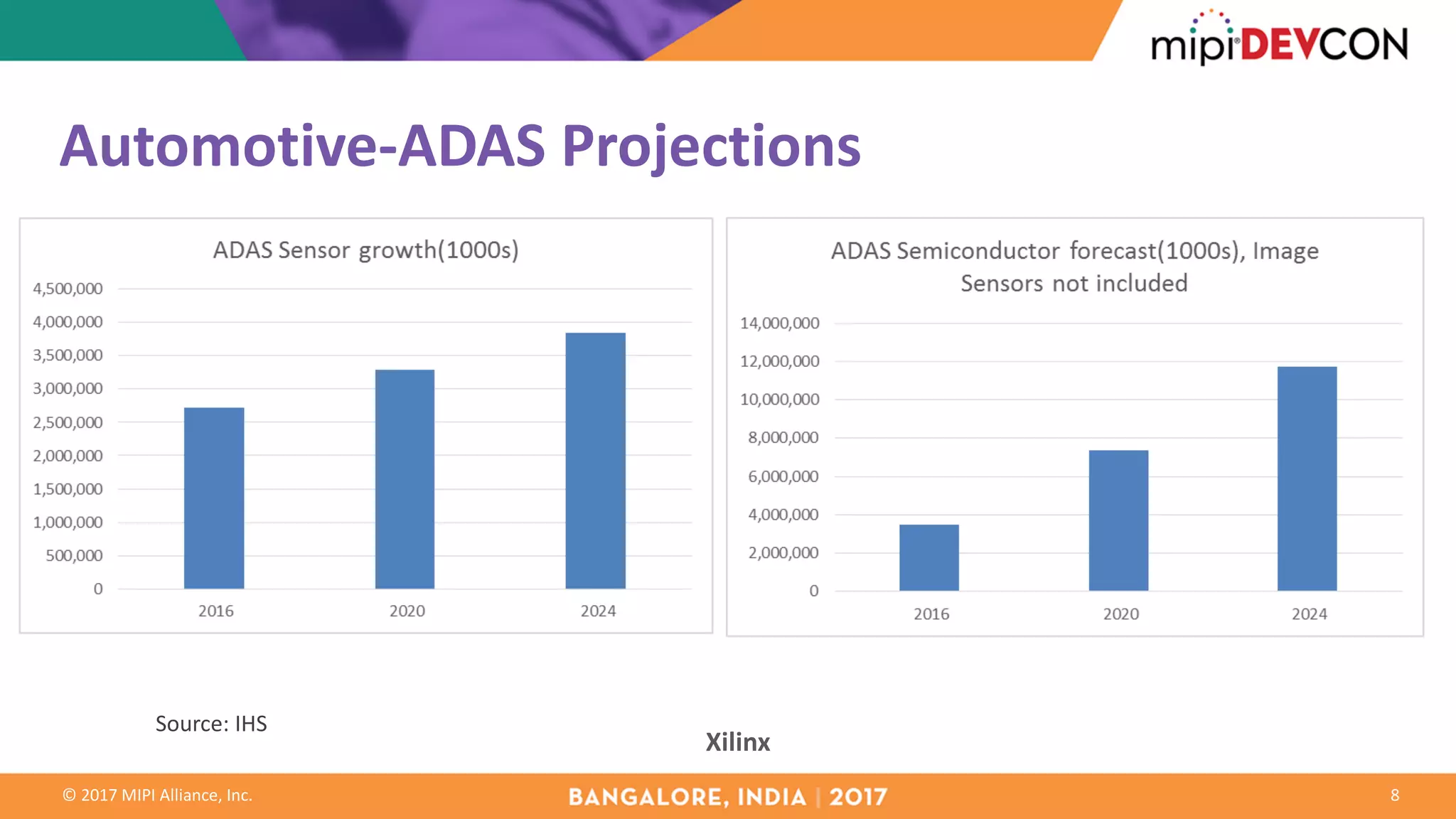

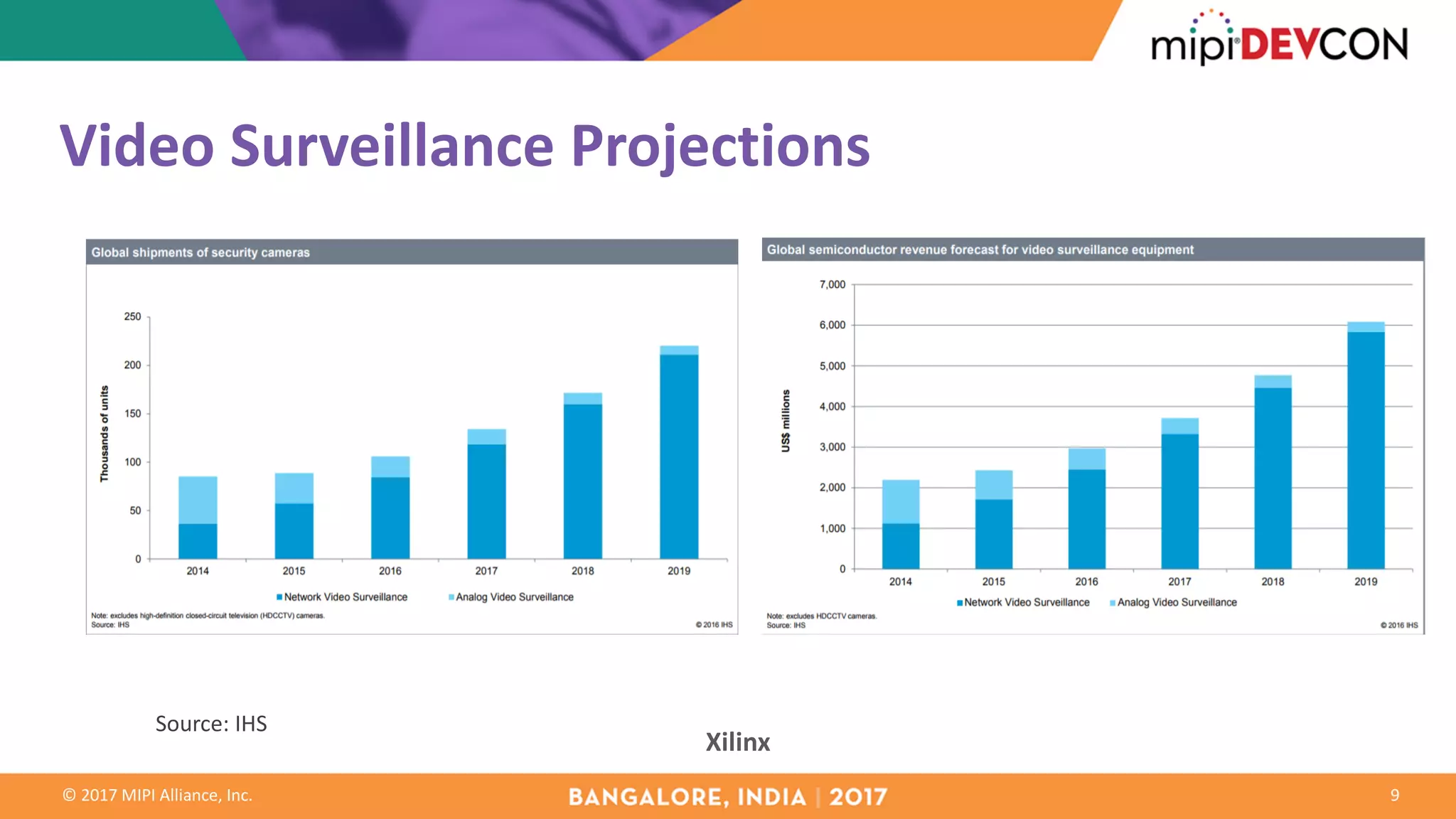

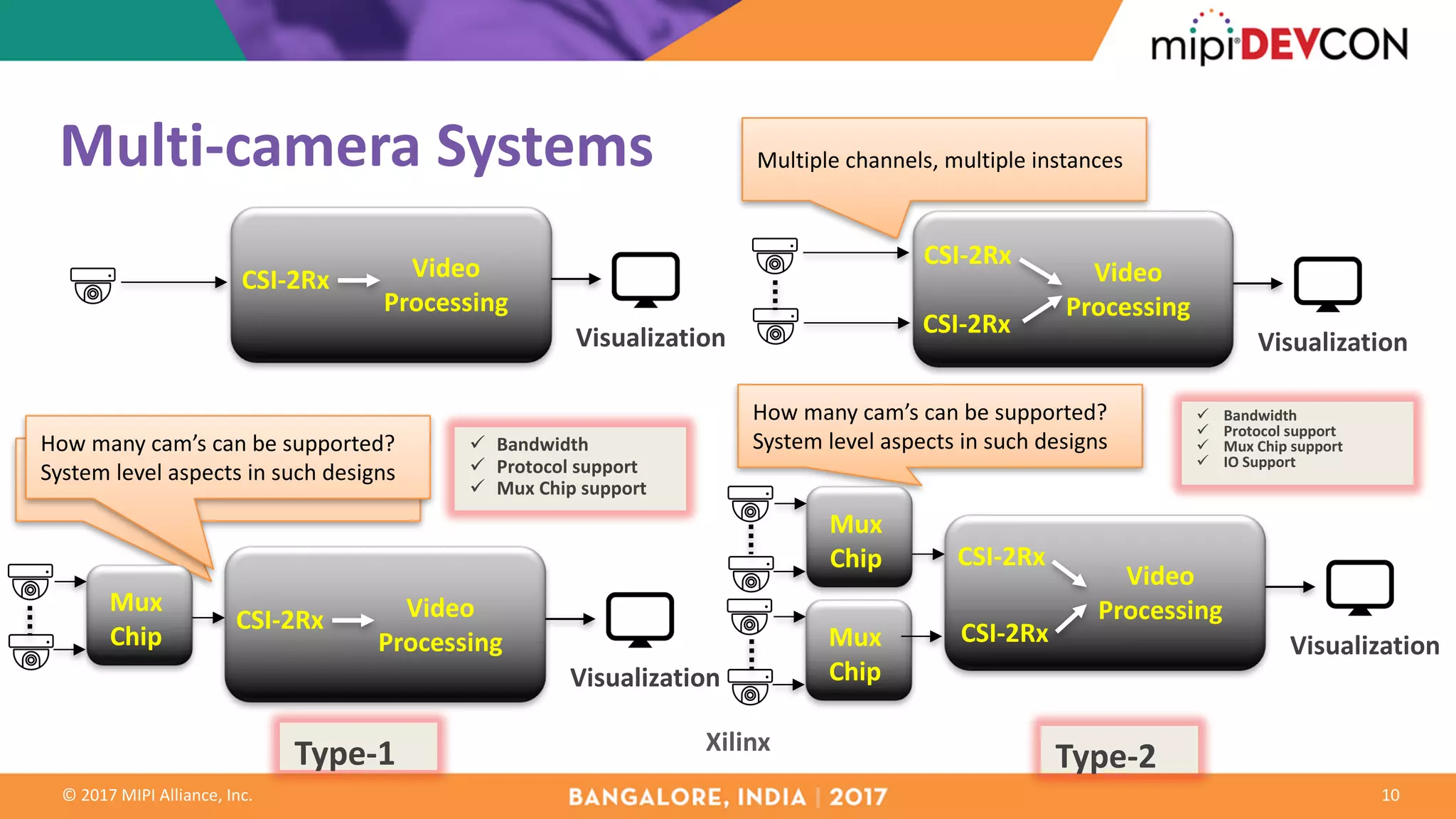

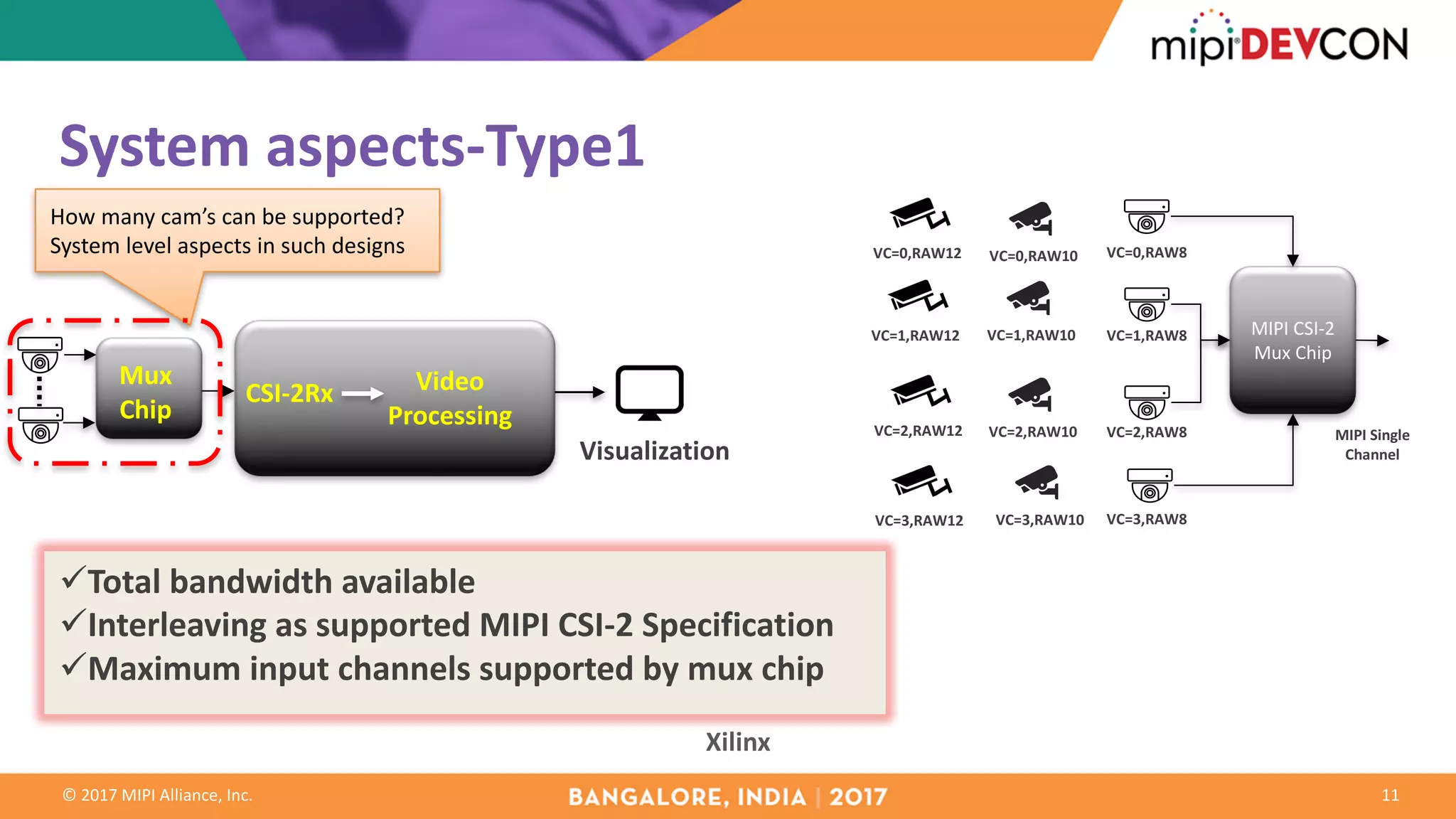

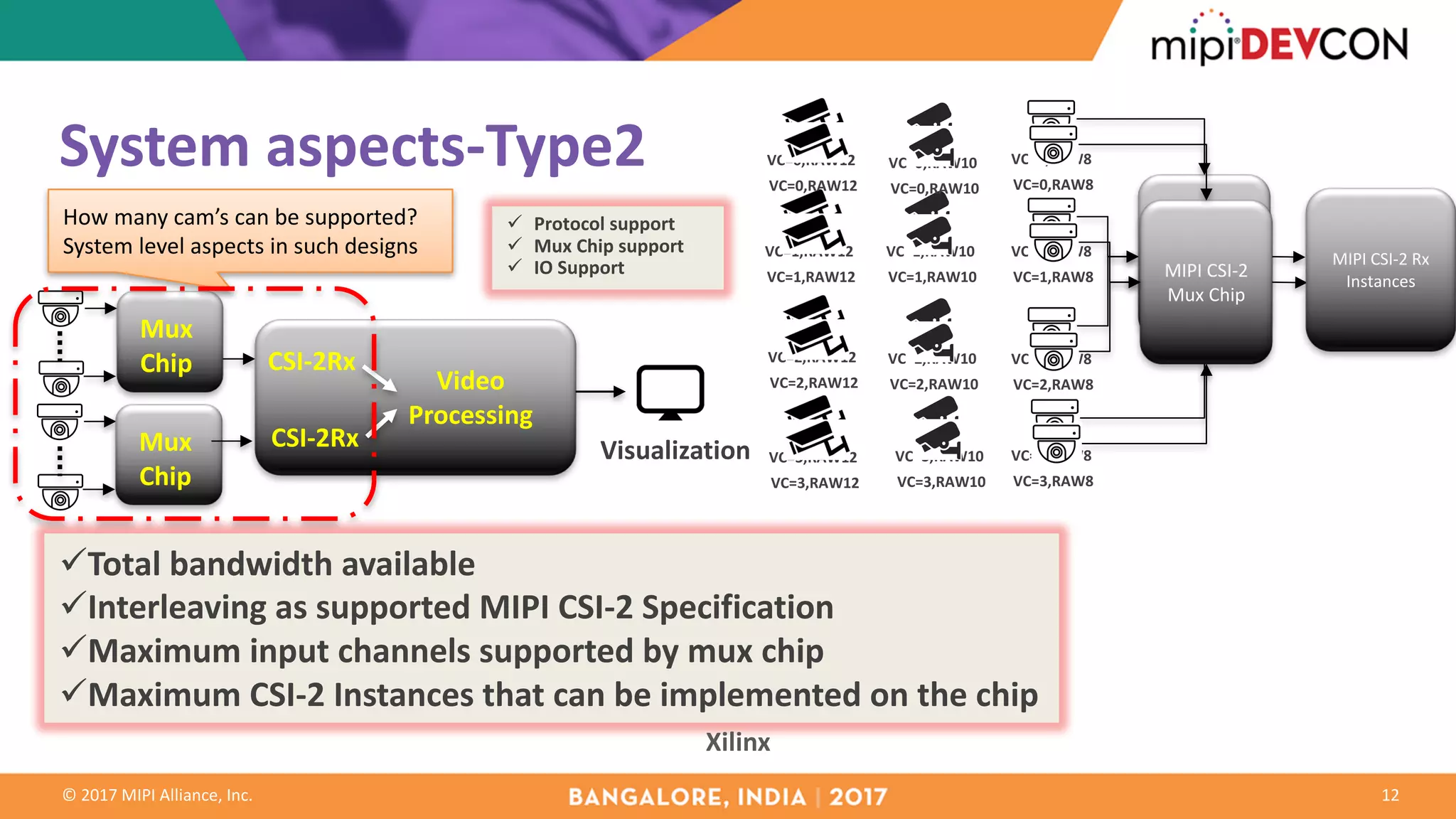

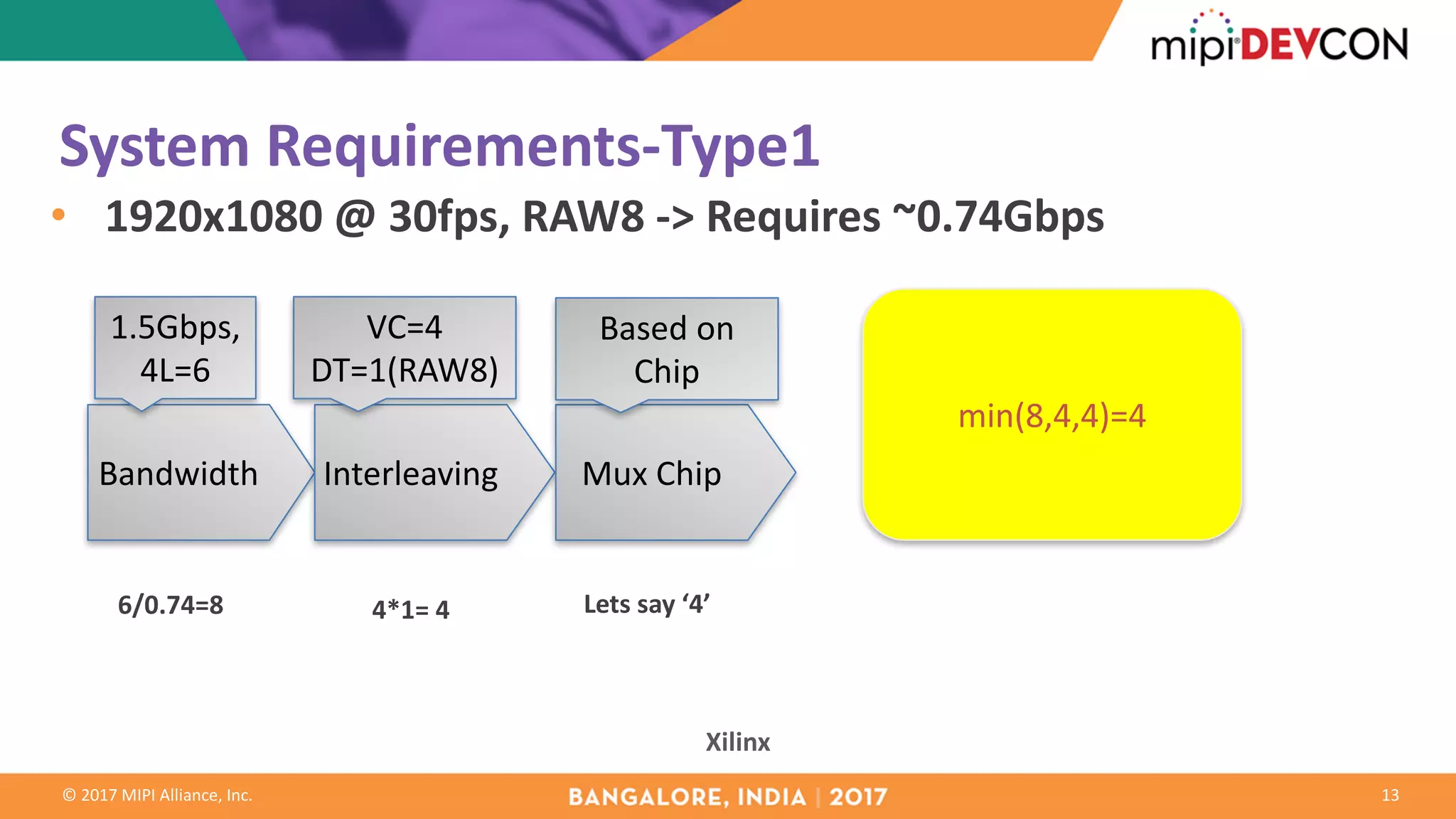

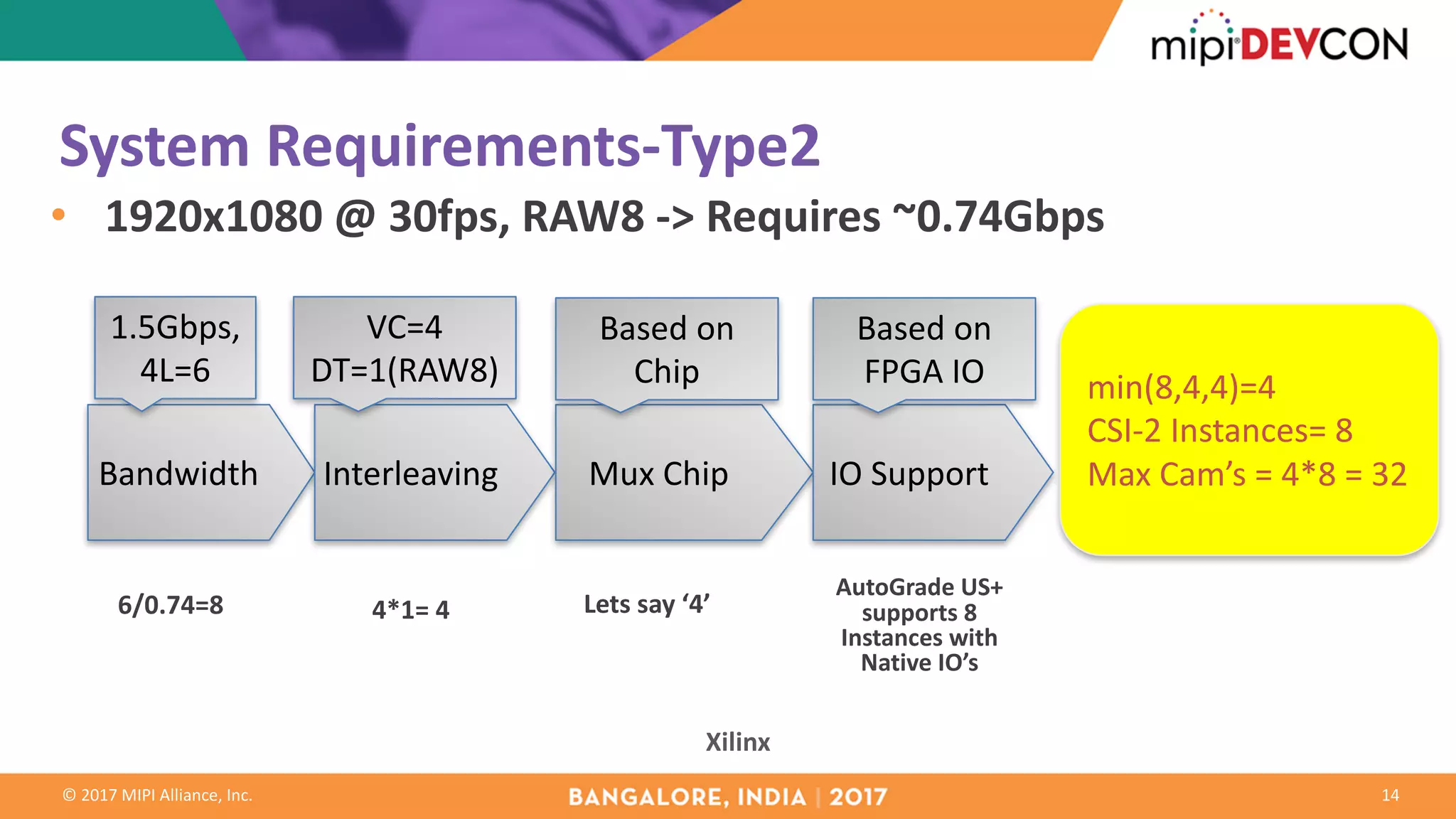

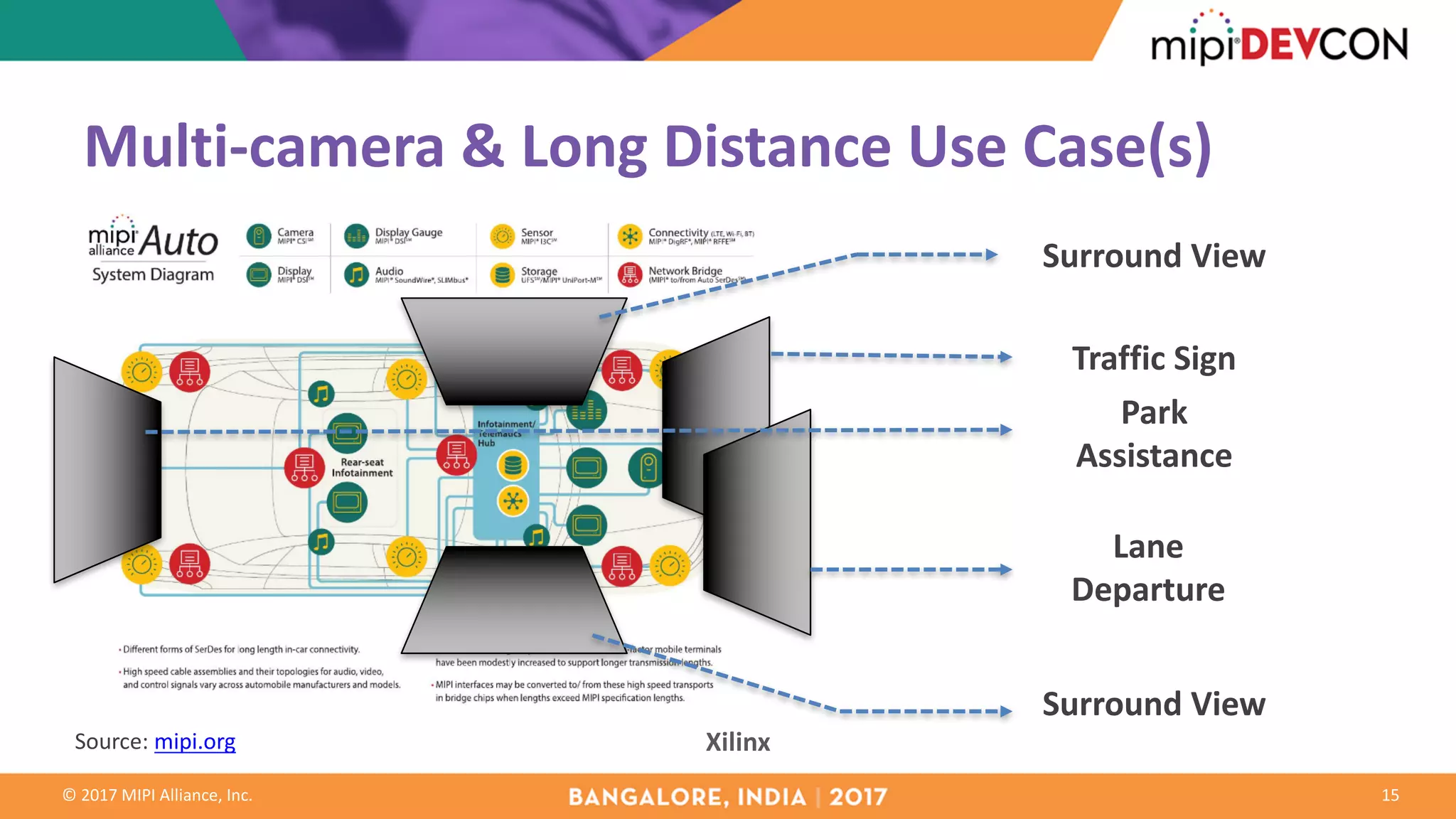

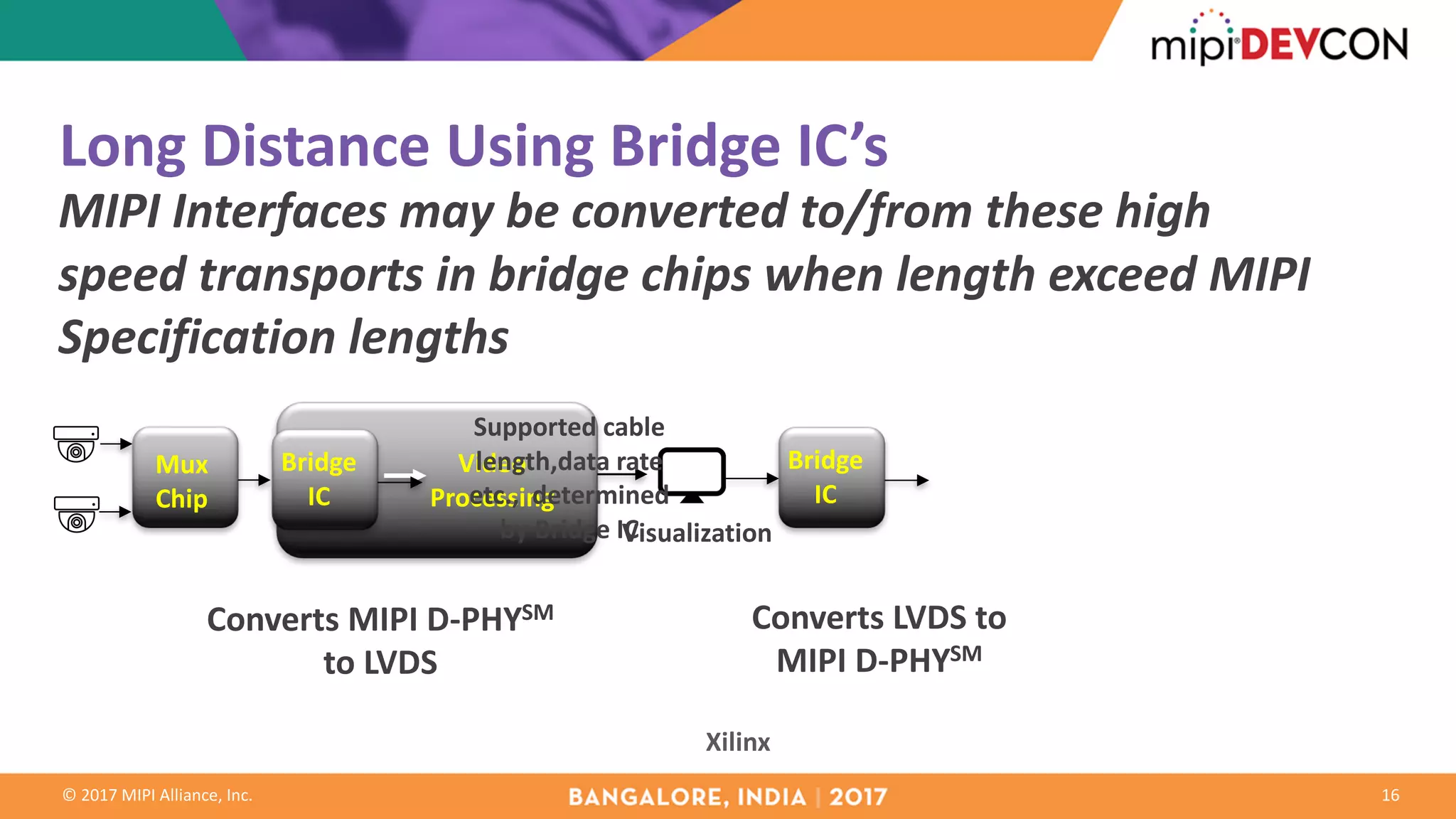

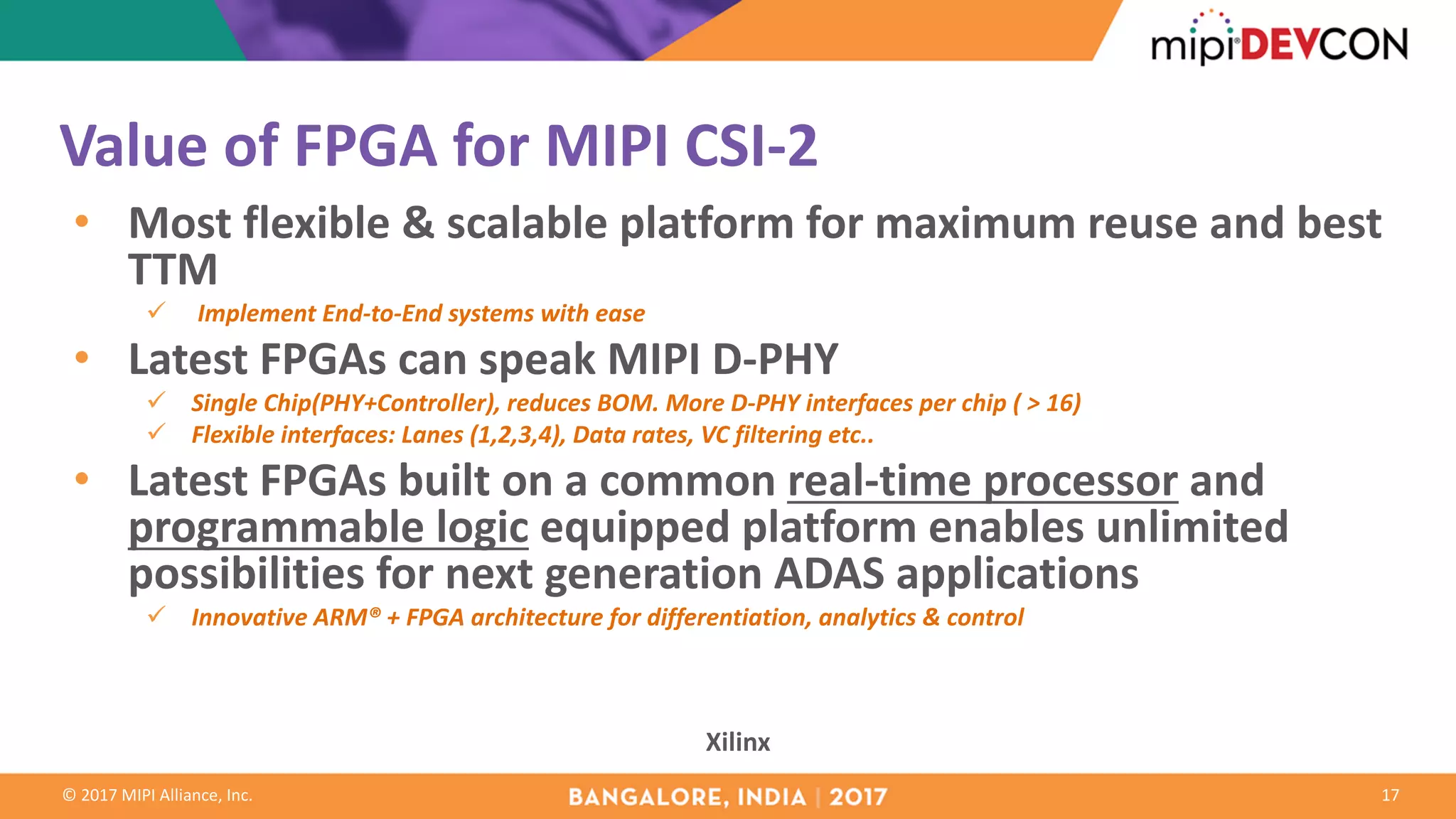

The document discusses the MIPI CSI-2 interface and its implementation for multi-camera and long-range use cases using FPGAs. It covers features of the MIPI CSI-2 specification, projections for the camera market, and system requirements for multi-camera systems. Additionally, it highlights the advantages of using FPGAs for these applications, including flexibility and scalability.