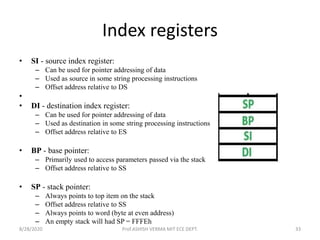

The document discusses the 8051 microcontroller and various advanced microprocessors, including their architectures, salient features, and differences between RISC and CISC architectures. It covers the evolution of microprocessors from the early Intel models like the 4004 to the Pentium, detailing specifications such as clock speeds, transistor counts, and memory addressing. The content also includes information about the internal structure, register organization, and functional capabilities of the 8086 microprocessor.