This document summarizes Drew Fustini's presentation about Linux on RISC-V. The key points are:

1) RISC-V is an open instruction set architecture that can be used as an alternative to proprietary ISAs like ARM and x86. It allows anyone to freely develop CPUs, SoCs and other hardware.

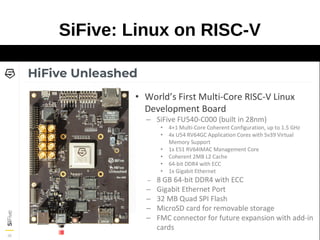

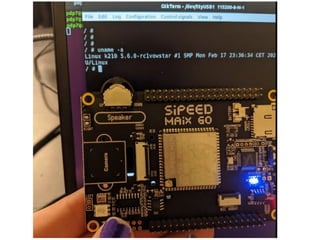

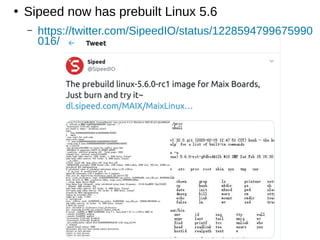

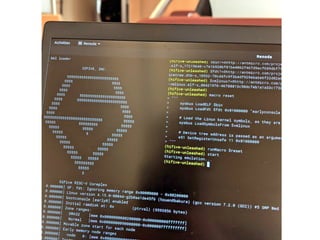

2) Several companies now offer RISC-V chips that run Linux, such as SiFive's HiFive Unleashed board. Open source projects are also bringing up Linux on chips like the Kendryte K210.

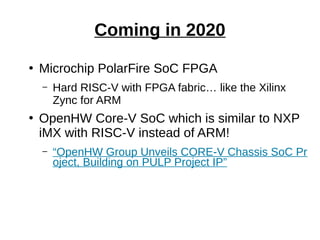

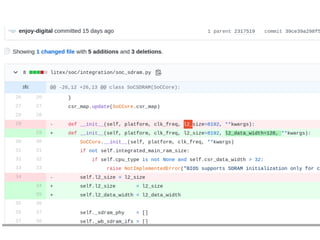

3) Open source FPGA tools like IceStorm, Trellis, X-Ray and SymbiFlow have made FPG