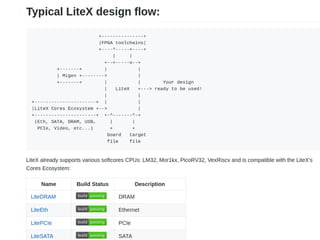

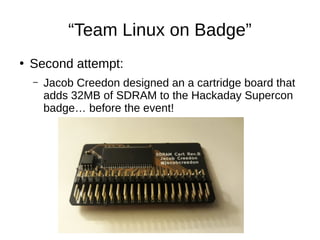

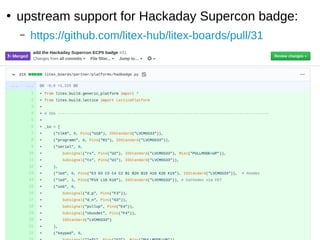

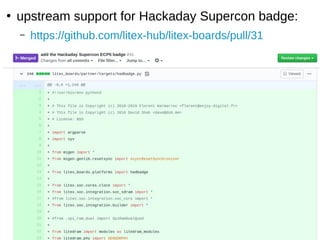

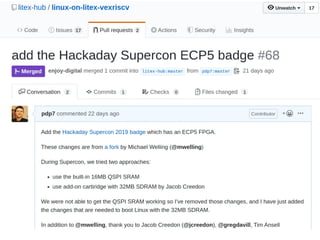

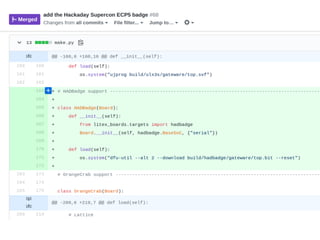

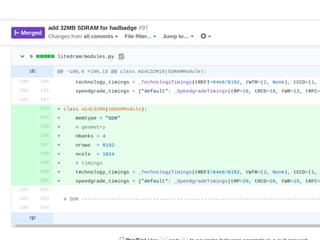

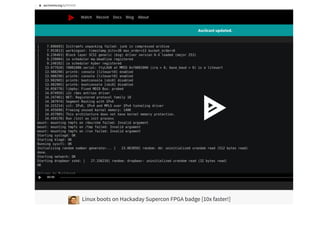

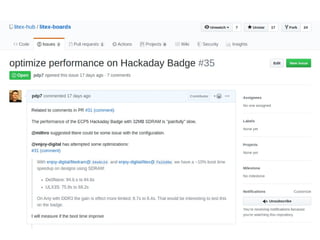

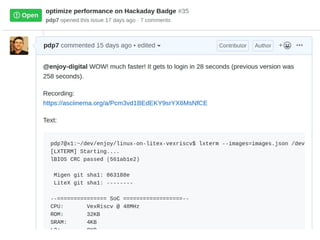

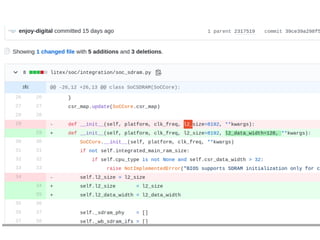

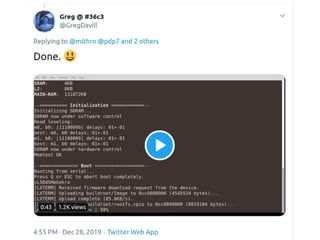

This document summarizes Drew Fustini's talk on running Linux on an FPGA badge using RISC-V and open source tools. It discusses how a team used LiteX and VexRiscv to build a SoC with a RISC-V CPU on the Hackaday Supercon badge FPGA that could boot Linux from an external SDRAM cartridge added to the badge. It also promotes open source FPGA tools like Project Trellis, LiteX, and boards like the Orange Crab and ULX3S for enabling open hardware development.