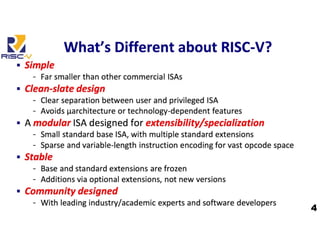

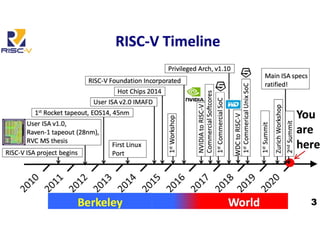

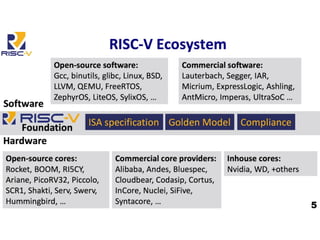

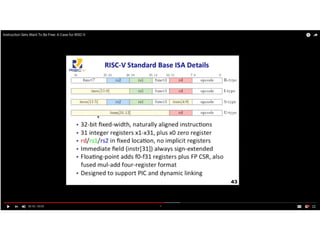

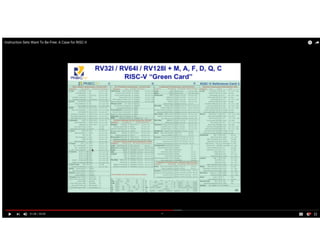

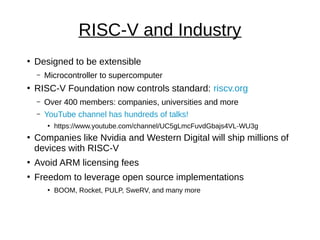

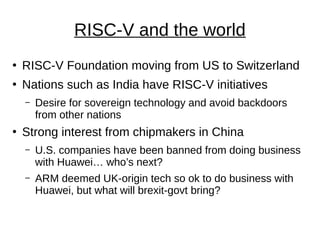

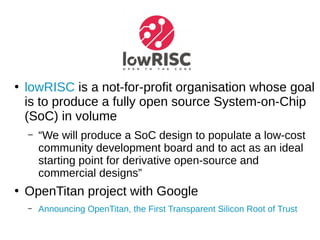

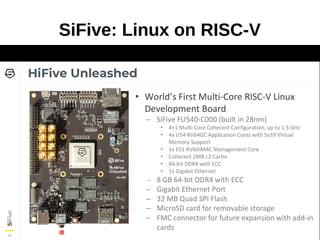

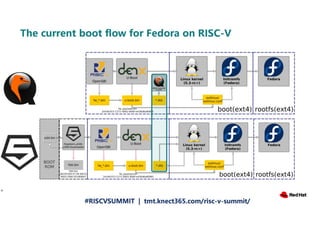

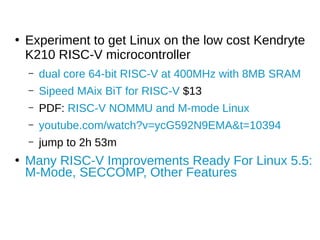

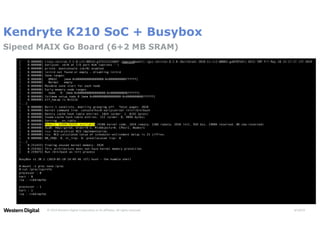

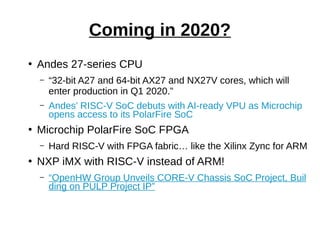

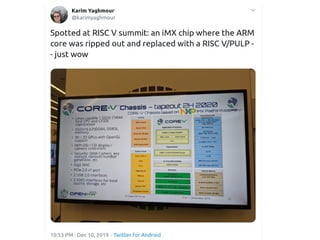

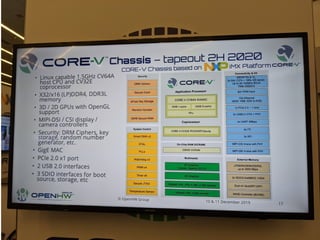

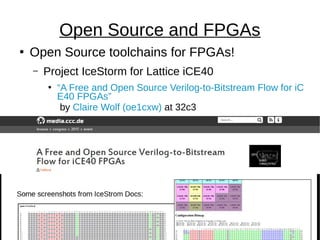

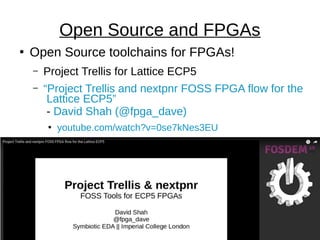

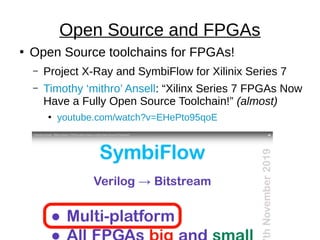

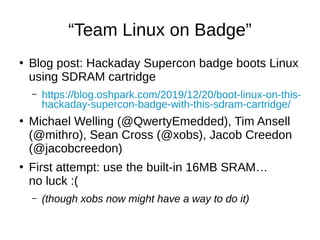

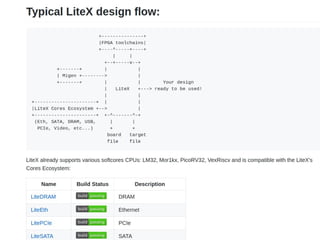

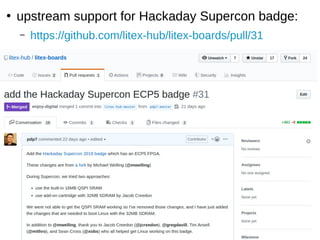

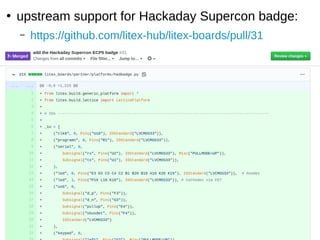

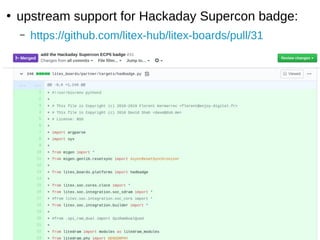

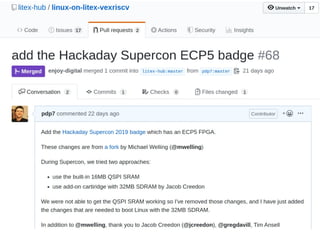

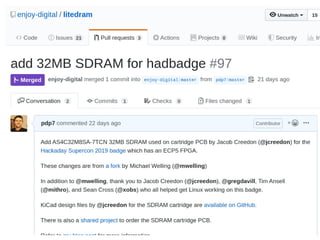

Die Präsentation behandelt die Implementierung von Linux auf RISC-V, einer offenen und freien Befehlssatzarchitektur, die in der Industrie an Bedeutung gewinnt. Dabei werden Fortschritte in der Hardware-Entwicklung, die Rolle der RISC-V-Stiftung und verschiedene Open-Source-Tools für FPGAs vorgestellt, die Zusammenarbeit zwischen Unternehmen und Bildungseinrichtungen fördern. Ebenfalls sind strategische Überlegungen hinsichtlich der globalen Chip-Produktion und der Sovereign Technology in Ländern wie Indien und China enthalten.