This document contains an assignment submission for a course on VLSI Design. It includes:

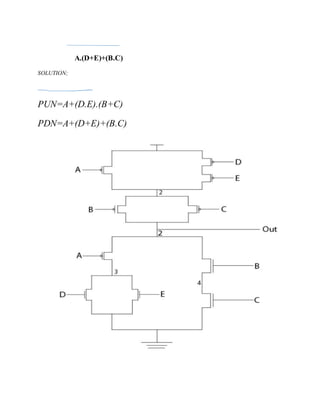

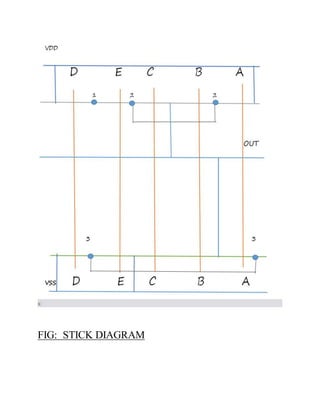

1) An explanation of stick diagrams and how they are constructed to visualize transistor placement and routing for a logic circuit.

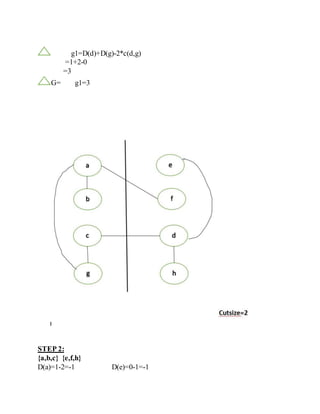

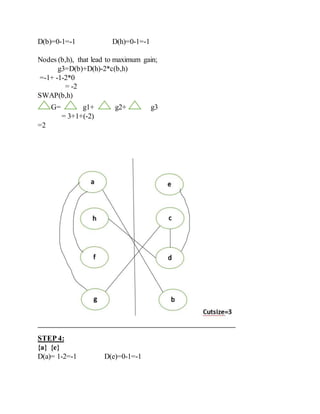

2) An overview of the Kernighan-Lin algorithm for iterative partitioning of graphs to minimize cut size through pairwise exchange of nodes between partitions.

3) An example application of a single pass of the Kernighan-Lin algorithm on a sample circuit to demonstrate the process.