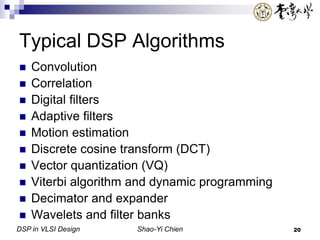

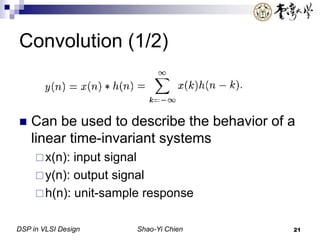

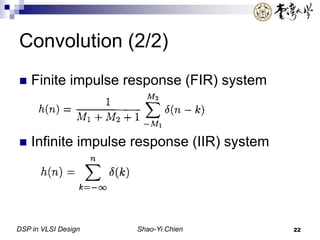

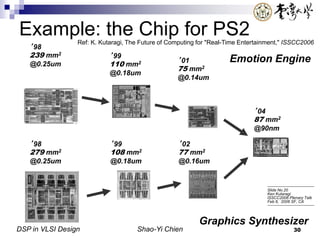

The document discusses digital signal processing (DSP) systems and their implementation in very-large-scale integration (VLSI) design. It highlights typical DSP algorithms, advantages of both analog and digital signal processing, the performance metrics of DSP systems, and the challenges related to power consumption and system complexity. Additionally, it covers various representations of DSP algorithms and the evolution of scaling in CMOS technology.

![DSP in VLSI Design Shao-Yi Chien 32

Problems: Increasing Static Power

VDD decreases

Save dynamic power

Protect thin gate oxides and short channels

No point in high value because of velocity sat.

Vt must decrease to

maintain device performance

But this causes exponential

increase in OFF leakage

Major future challenge

Static

Dynamic

[Moore03]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-32-320.jpg)

![DSP in VLSI Design Shao-Yi Chien 34

Problems: Power Density

Intel VP Patrick Gelsinger (ISSCC 2001)

If scaling continues at present pace, by 2005, high

speed processors would have power density of

nuclear reactor, by 2010, a rocket nozzle, and by

2015, surface of sun.

“Business as usual will not work in the future.”

Intel stock dropped 8%

on the next day

But attention to power is

increasing

[Gelsinger01]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-34-320.jpg)

![DSP in VLSI Design

Heterogeneous System Integration

Shao-Yi Chien 43

[TSMC 2015]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-43-320.jpg)

![DSP in VLSI Design

InFO (Integrated Fan Out)

Shao-Yi Chien 44

[TSMC 2015]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-44-320.jpg)

![DSP in VLSI Design

CoWoS (Chip-On-Wafer-On-Substrate)

Shao-Yi Chien 45

[TSMC 2015]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-45-320.jpg)

![DSP in VLSI Design

Example of CoWoS

Shao-Yi Chien 46

[TSMC 2015]](https://image.slidesharecdn.com/1introduction-240908135332-aa6a7925/85/introduction-to-digital-signal-processing-systems-46-320.jpg)