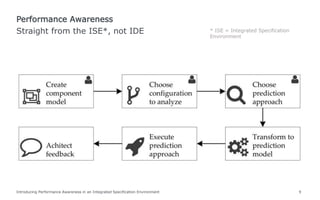

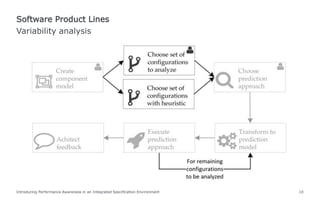

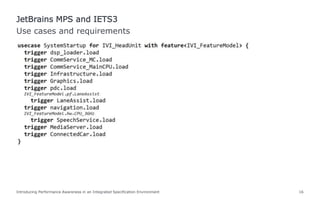

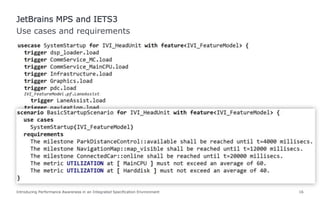

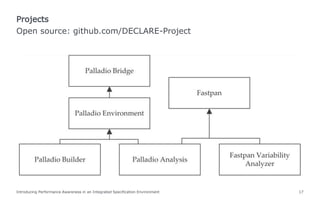

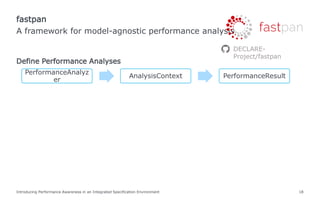

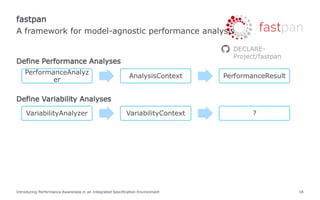

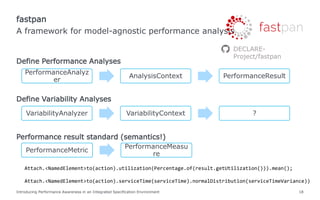

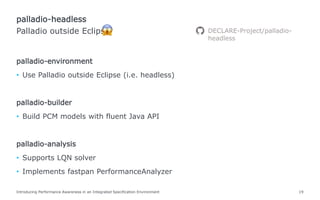

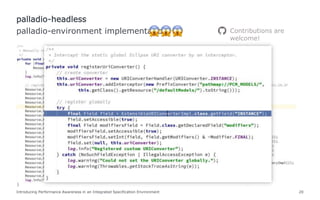

This master's thesis discusses the integration of performance awareness into the software specification process at the University of Stuttgart. It highlights the significance of performance prediction and modeling, the challenges of implementing these concepts in development environments, and a framework for performance analysis through the DECLARE project. The document concludes that while real-time diagnostics and variability analysis are achievable, further analysis for incomplete configurations is still needed.

![Introducing Performance Awareness in an Integrated Specification Environment 4

Performance prediction at its finest

Palladio

Becker et al. [2009]](https://image.slidesharecdn.com/thesis-fk-presentation-splitted-161220105734/85/Introducing-Performance-Awareness-in-an-Integrated-Specification-Environment-4-320.jpg)

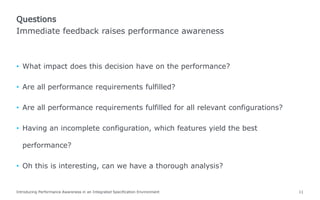

![• Palladio can provide real-time diagnostics

• Variability analysis in IETS

3

• [Yes] What impact does this decision have on the performance?

• [Yes] Are all performance requirements fulfilled?

• [Yes] Are all performance requirements fulfilled for all relevant

configurations?

• [Not yet] Having an incomplete configuration, which features yield the best

performance?

Results & Conclusion

Introducing Performance Awareness in an Integrated Specification Environment 27](https://image.slidesharecdn.com/thesis-fk-presentation-splitted-161220105734/85/Introducing-Performance-Awareness-in-an-Integrated-Specification-Environment-41-320.jpg)