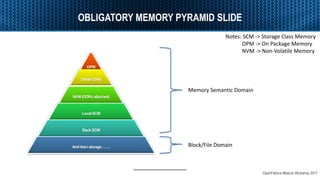

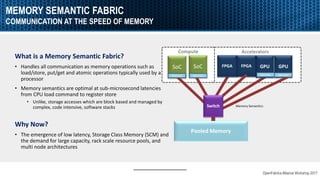

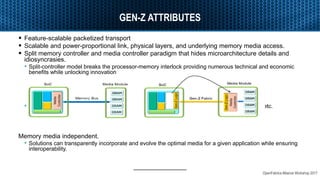

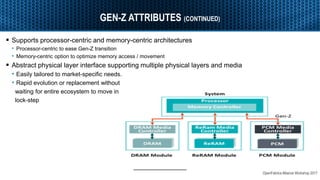

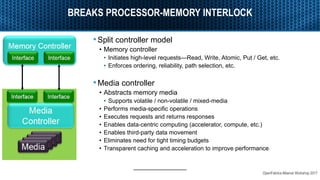

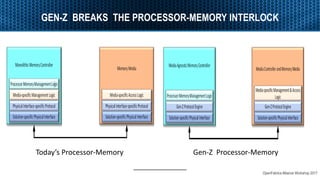

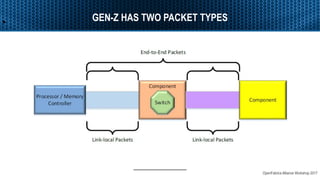

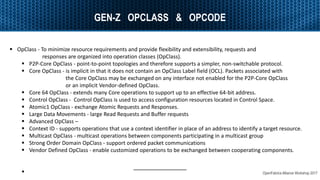

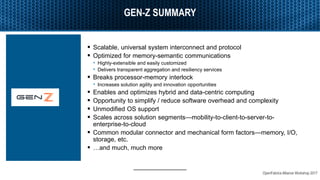

This document provides an overview of Gen-Z, a new interconnect architecture proposed to address challenges with increasing data growth, flat memory capacity, and the need for real-time data insights. Gen-Z is designed to provide high bandwidth and low latency memory semantic communications across systems. It breaks the traditional processor-memory interlock by introducing a split controller model. This allows for more flexible and composable solutions that can leverage different memory technologies. The Gen-Z Consortium is developing open standards for the architecture with the goal of enabling innovation through an open and non-proprietary approach.