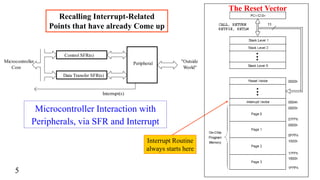

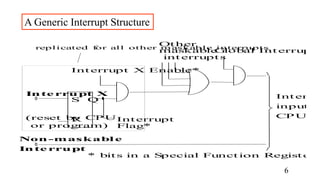

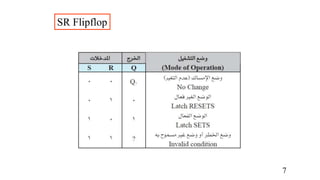

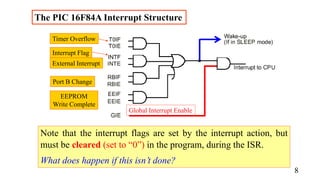

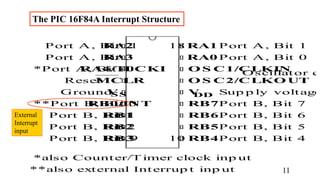

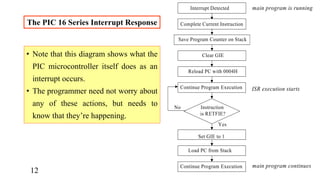

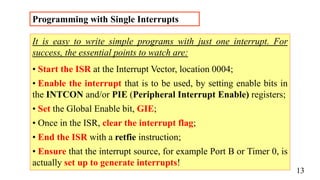

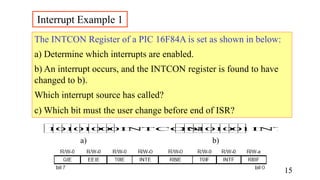

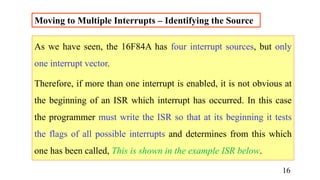

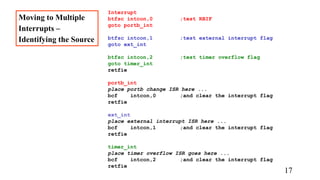

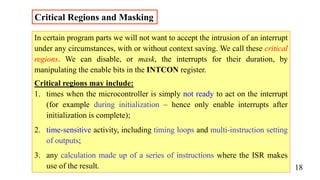

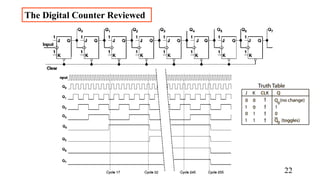

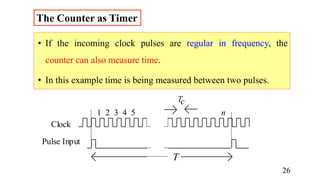

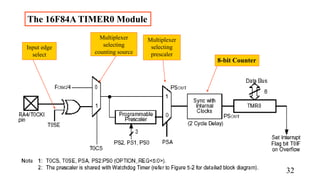

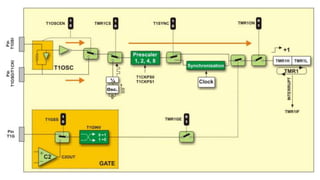

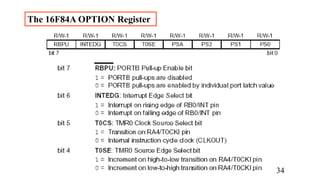

This chapter introduces interrupts, counters, timers and their applications in microcontrollers. It discusses the underlying hardware structures that support interrupts and counting functions. It then describes the specific interrupt and Timer 0 structures in the PIC16F84A microcontroller. Simple programming examples are provided to demonstrate how to use interrupts and Timer 0 for applications like input detection and time delay. The chapter also discusses interrupt latency and techniques like interrupt masking for use in critical program sections.