Eric Theis resume61.1

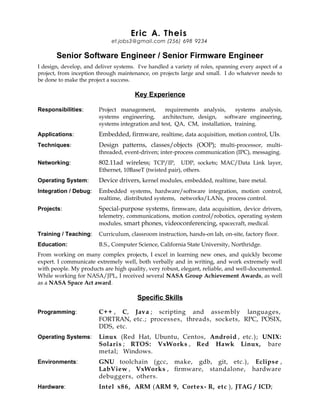

- 1. Eric A. Theis et.jobs3@gmail.com (256) 698 9234 Senior Software Engineer / Senior Firmware Engineer I design, develop, and deliver systems. I've handled a variety of roles, spanning every aspect of a project, from inception through maintenance, on projects large and small. I do whatever needs to be done to make the project a success. Key Experience Responsibilities: Project management, requirements analysis, systems analysis, systems engineering, architecture, design, software engineering, systems integration and test, QA, CM, installation, training. Applications: Embedded, firmware, realtime, data acquisition, motion control, UIs. Techniques: Design patterns, classes/objects (OOP); multi-processor, multi- threaded, event-driven; inter-process communication (IPC), messaging. Networking: 802.11ad wireless; TCP/IP, UDP, sockets; MAC/Data Link layer, Ethernet, 10BaseT (twisted pair), others. Operating System: Device drivers, kernel modules, embedded, realtime, bare metal. Integration / Debug: Embedded systems, hardware/software integration, motion control, realtime, distributed systems, networks/LANs, process control. Projects: Special-purpose systems, firmware, data acquisition, device drivers, telemetry, communications, motion control/robotics, operating system modules, smart phones, videoconferencing, spacecraft, medical. Training / Teaching: Curriculum, classroom instruction, hands-on lab, on-site, factory floor. Education: B.S., Computer Science, California State University, Northridge. From working on many complex projects, I excel in learning new ones, and quickly become expert. I communicate extremely well, both verbally and in writing, and work extremely well with people. My products are high quality, very robust, elegant, reliable, and well-documented. While working for NASA/JPL, I received several NASA Group Achievement Awards, as well as a NASA Space Act award. Specific Skills Programming: C++ , C, Java ; scripting and assembly languages, FORTRAN, etc.; processes, threads, sockets, RPC, POSIX, DDS, etc. Operating Systems: Linux (Red Hat, Ubuntu, Centos, Android , etc.); UNIX: Solaris ; RTOS: VxWorks , Red Hawk Linux, bare metal; Windows. Environments: GNU toolchain (gcc, make, gdb, git, etc.), Eclipse , LabView , VxWorks , firmware, standalone, hardware debuggers, others. Hardware: Intel x86, ARM (ARM 9, Cortex- R, etc ), JTAG / ICD;

- 2. PCI, I2C, GPIO, USB, Ethernet , 802.1 1 ad ; SPARC; VAX; etc.

- 3. Experience Varian Medical Systems Senior Firmware Engineer Oncology Systems October 2015 - Present Embedded Systems Team (contractor) Investigated and solved a variety of issues in an extremely complex medical radiation therapy system, used in large hospitals for cancer treatment. Took over a project to refactor the subsystem controlling the multi-leaf collimator, simplifying and clarifying the hardware abstraction layer in preparation for a new design (Rhapsody, VxWorks, C++). Once familiar with the system, I focused on the subsystem controlling the linear accelerator and the related motors and electronics which generate and control the X-ray treatment beam. As every issue was very complex, and correct behavior is absolutely essential, I wrote a small document describing each issue in detail, and the solution implemented. I was also called upon to triage issues uncovered in manufacturing and in the field, recommending further diagnostic actions, or isolating the issue to a specific subsystem and passing the issue to the appropriate expert. The system used a Windows PC for the operator control system. It communicates via TCP and UDP to each of 10 distributed single-board ‘nodes’, each running VxWorks 6.9. Each node contained an Intel-based SOM, linked via PCI to an on-board XyLinx FPGA, which in turn used a proprietary protocol over 10baseT cabling to communicate with the subsystem-specific controller board in the treatment room. The nodes’ FPGAs embed a MicroBlaze soft ‘core’ to drive their dedicated tasks. The entire system has more than 10 motor driven axes, which produce synchronized motion and radiation delivery under realtime software control. The beam generation node was unusually complex, in that its dedicated controller in turn communicates with multiple sub-controllers via CANbus, a number of sensor signals, and current-loop safety lines. The software was designed and maintained using UML in Rhapsody, using C++ code which was in turn built using MS Visual Studio or the VxWorks build system. Debugging employed a variety of tools, including WindRiver’s WindView for debugging realtime issues, a CANbus sniffer, and copious logging. Nitero, Incorporated Senior Firmware Engineer 60 GHz Wi-Fi CMOS March 2014 – August 2015 Firmware Team Developed and debugged firmware for a new 60 GHz IEEE 802.11ad Wi-Fi module, as part of a small firmware team in a startup environment. The firmware was standalone (no RTOS), coded in C using the ARM tool chain, ARM DS-5 hardware debugger, via its Eclipse front end. The host systems ran Android, Ubuntu Linux, and Red Hat Linux using custom PCIe device drivers. The chip was a mixed-signal low power solution, designed for mobile devices, such as smartphones and tablets. It contained two ARM Cortex-R5 cores, and number of custom modules on the AXI bus, including a PCIe interface, tightly coupled memory (two types), custom packet transmit/receive controllers, an interrrupt controller, clocks, timers, GPIOs, I2C devices, a serial debug port, and various other special-purpose devices. The firmware implemented the entire 802.11 wireless link layer protocol for the new 60GHz bands. Host Linux drivers used DMA over PCIe to communicate to the ARM processors. The ARM processors used direct access to memory-mapped registers to control the various modules on the AXI bus, and thus the RF hardware. Participated in architecture, design, interface design, development, debugging of the firmware, as well as multiple Wi-Fi Alliance "Plugfests", testing our equipment's interoperability with that of other vendors. Expanded, refined, and debugged the prototype beaconing and wireless beacon interval (frame) timing, including considerable tuning requiring use of a scope and logic analyzer. Implemented the entire IEEE 802.11ad beam-forming and beam- refinement protocols (aka "Sector Level Sweeps"). Performed extensive debugging of all aspects of the system, including identifying and characterizing multiple obscure issues with both software and hardware. v61.1 5/8/16

- 4. For a prototype/demo effort on a Freescale i.MX 6 (ARM Cortex-A9) Sabre development board, modified an Android video driver and built a custom kernel module to grab display frames and send them over a wireless LAN at high speed for display on a sister system. Worked on similar modules on a Qualcomm Snapdragon 805 development system. Polycom, Incorporated Senior Staff Engineer Video Conferencing Endpoints May 2011 - January 2014 System Software Team Architected substantial innovations for the platform software for the next generation high-end video conferencing systems: A hardware abstraction layer, video source and sink abstraction, IPC message passing scheme, and XML/XSD based shared configuration service. Implemented the prototypes of the hardware abstraction layer and video source/sink abstraction layer. Supervised development of the production versions of both subsystems, overseeing and mentoring resources both local and in Beijing. Developed a general system service, abstracting multiple platform-dependent operations. Supervised development of, provided technical guidance for, and helped debug two Linux video device drivers, developed by contractors in India. Fixed a multitude of system level bugs, including driver issues. Worked with hardware engineers to trace GPIO and I2C problems to the part level. Wrote the software command specification for a new video camera. On another project, developed and implemented an architecture to integrate an Android GUI app with existing (non-Android) processes handling audio, video, and telephony. Helped debug issues communicating with the audio DSP, and the Windows-based configuration app via USB. Products were standalone embedded systems based on the TI Netra processor (ARM9), running Android 4.0 (ICS), developed in C, C++, Java and JNI, Google Protocol Buffers over Linx, and various script languages. Texas Instruments Consultant Texas Instruments, OMAP Processor Business Unit December 2010 – May 2011 (Employee of Imperial, contractor to Wind River, for a TI project) Debugged various system-level issues with TI's adaptation of Android 2.2 (Froyo), 2.3 (Gingerbread), and 3.0 (Honeycomb) to its OMAP4 (4430 and 4460) ARM platforms. Developed and documented procedures for testing power management features. Diagnosed and resolved issues when booting from an SD card. Performed analysis of cache performance on TI and customer platforms, evaluating verious implementations of memory copying for the Bionic libc library. LG Electronics Consultant LG Mobile Electronics, Optimus Smartphone July 2010 - December 2010 (Employee of Sapphire, contractor to Accenture, for an LG project) Debugged Linux kernel and device drivers for a Qualcomm chipset, reproduced and characterized elusive bugs, for final release testing of LG's new Optimus smartphone. Reviewed and documented the I2C and GPIO drivers in the BSP. Led a small project which re-engineered the phone's "charging mode", using C and JTAG support. The phone runs Google's Android 2.2 (Froyo) release, on Qualcomm's MSM7627 chipset. The chipset uses an ARM 9 processor for the modem (mobile telephone) functions, and an ARM 11 processor for the Android OS, other devices (display, USB, etc.), and the Java applications. They communicate via RPC and shared memory. NASA Marshall Space Flight Center Lead Software Engineer Ares 1 rocket Instrument Unit EGSE v61.1 5/8/16

- 5. March 2009 - June 2010 (Employee of Geologics, contractor to Boeing, for NASA contract) Led a team designing and developing the Electrical Ground Support Equipment (EGSE) for the assembly, integration, and checkout of the electronics for NASA's new Ares 1 rocket. To manage the dynamic and emergent nature of the Ares 1 rocket's development, the project evolved from a traditional "waterfall" methodology to an Agile Scrum methodology. Performed requirements definition, design documentation, PDR, and CDR. Designed and developed the basic distributed infrastructure all the software components are based on, and participated in developing several rapid prototypes to show the customer. Designed the software as a distributed system, primarily using UML in Enterprise Architect. Per the Agile Development methodology, implemented much of the system during design, using the Eclipse development environment on Red Hat Linux, using C++, the OpenSplice Data Distribution System (DDS) to communicate among processes and computers, and the Qt graphics libraries to drive the GUI. The flexible distributed system design accommodated the very dynamic requirements. The EGSE racks contain two Concurrent realtime computers, running Red Hawk Realtime Linux. The software drives seven Gigabit Ethernet buses, four Agilent power supplies, an RF receiver/frame sync/decommutator system, nine 1553 buses, two RS-422 and six discrete line interfaces. Components of the software simulated the behavior of various parts of the rocket, to support testing components individually. NASA Jet Propulsion Laboratory (JPL) Instrument I&T EGSE Lead Aquarius instrument April 2008 - March 2009 Senior Information Systems & Computer Science Software Engineer Supported all Electrical Ground Support Equipment (EGSE) used for the assembly, integration, and checkout of NASA's Aquarius instrument. The EGSE includes all hardware that connects to the instrument, and the software that drives it: The spacecraft simulator (PC), the 1553 bus, two racks of equipment for powering, monitoring, and controlling the instrument, three PCs running custom software that control the racks, and a Sun workstation. Developed a socket interface between two existing applications. Diagnosed and resolved a host of issues relating to all aspects of the EGSE: administered the Windows systems and network, set up backups, fixed bugs in the controlling software (C, C++), wrote scripts to automate various operations, wrote a new LabView script, and enhanced existing ones. Systems were PCs running Windows XP, Centos Linux, Sun Solaris (UNIX), interconnected via a multilevel local Ethernet network. The various systems run applications based on C, C++, and LabView, and MatLab. Instrument I&T EGSE Lead Orbiting Carbon Observatory January 2007 - March 2008 (Contractor, Columbus Technologies and Services, Inc.) Led a team responsible for all Electrical Ground Support Equipment (EGSE) used for the assembly, integration, and checkout of NASA's Orbiting Carbon Observatory (OCO) instrument. This included: The 1553 spacecraft bus, an RS-422-based interface to a solid-state recorder simulator system, power from computer-controlled power supplies, as well as two discrete signals used to indicate spacecraft events. Diagnosed and resolved a host of issues relating to all aspects of the instrument electronic interfaces, spacecraft and instrument commanding, telemetry, testing, and operations. Became the primary EGSE and instrument operator, writing procedures and training all other instrument operators. Also resolved issues with the Optical Calibration equipment (OGSE), including a balky heliostat system, and LabView and IEEE 488/GPIB issues. Systems were PCs running Windows XP, Red Hat and Centos Linux, Sun/SPARC workstations running Solaris (UNIX), and a PowerPC running VxWorks, all interconnected via a multilevel local Ethernet network, gatewayed to the JPL-wide network. The various systems run applications based on C, C++, and LabView. Senior Software Engineer Mars Smart Lander (MSL) project July 2006 - December 2007 (Contractor, Columbus Technologies and Services, Inc.) Designed and developed interface 'bots' to control the flight computer and other equipment for the Mars Science Laboratory (MSL) rover (aka “Curiousity”), during development. Computer is a RAD-750 running VxWorks; v61.1 5/8/16

- 6. the control bot was written using Tcl/Tk and Expect under Red Hat Linux and Solaris. The bots are part of the Bench Test Equipment for debugging, exercising, characterizing, and calibrating the flight hardware. The bots handle controlling the power, downloading and booting VxWorks, starting the test software, issuing commands to VxWorks and the development software, and monitoring and logging any messages emitted by any of these elements. This software interfaces with an existing body of software derived from other missions. Senior Software Engineer Mars Exploration Rovers, Phoenix Mars Lander June 2005 - July 2006 (Contractor, Columbus Technologies and Services, Inc.) Developed significant modifications to and new features for the Rover Sequence Editor (RoSE), which is used daily by NASA's Mars Exploration Rover (MER) mission for controlling the two rovers currently active on Mars. These modifications expand RoSE's abilities, specifically to adapt it to two new NASA Mars missions: The Mars Polar Lander '06 (aka "Phoenix") launching in 2006, and the Mars Science Laboratory (aka "MSL": A new Mars rover, launching in 2011). The work required coming up to speed on Java very quickly, then making modifications to the existing Java and XML. Half of the work involved incorporating the existing standalone RoSE into the existing Eclipse environment for the MSL mission, as part of their Extreme Programming team. Cognizant Engineer / Lead Programmer Multi-mission Ground Data System July 2001 - June 2005 (Contractor, Columbus Technologies and Services, Inc.) Cognizant Development Engineer (CDE) for the Simulation (SIM) subsystem of the Advanced Multi-Mission Operations System (AMMOS). Developed metacode for and generated a wide variety of complicated testing datasets for a number of flying and upcoming NASA spacecraft. Added additional functionality to SIM to handle new CRCs, Turbo encoding/decoding, Pseudo-randomization, and various other capabilities. Performed substantial rewrite of the system, removing old design flaws and greatly increasing its capabilities by making it object-oriented (to the degree possible), using C, C++, and Perl. Assisted in the multithreaded design of the Data Accountability Subsystem (DAS). UCLA Extension Technical Instructor School of Business and Information Systems October 1995 - March 2009 (part time) Taught various courses (Introduction to UNIX/Linux, Intermediate UNIX/Linux, UNIX/Linux Shell Scripting, Advanced C Programming, X/Windows/Motif programming, Solaris System Administration I and II), both at UCLA and on-site for companies. Completely overhauled the existing UNIX courses and lab systems. Consistently rated in the top 2% of instructors by students, and received frequent requests from students to teach other classes. Sun Microsystems USB Development Team Lead Kernel I/O Frameworks Group November 1998 - July 2001 Member of Technical Staff Led one of two teams in the development and integration of a new device driver and multithreaded kernel I/O framework for Universal Serial Bus (USB) support into Sun's flagship SVR4 UNIX (Solaris 7, 8, 9). Coordinated and participated in Sun's demos and testing at a USB Implementer's Forum in Milpitas, CA. Fixed a number of driver and kernel bugs related to USB (in C). Wrote extensions to the standard Solaris debugger to support debugging the USB framework and drivers. Wrote extensions to a system administration utility providing dynamic display, configuration control, and software hotplugging of USB devices, which required kernel interaction. NCR / Teradata Software Engineer Operating Systems Group October 1997 - November 1998 (Contractor, Systems Integrated) Converted the software repository from CVS to ClearCase. Overhauled the group's software packaging, making extensive changes to the project's installation scripts and procedures. Fixed numerous bugs in the group's product. v61.1 5/8/16

- 7. Sun Microsystems Device Driver Developer Kernel I/O Frameworks Group December 1993 - October 1997 (Contractor, Mini-Systems Associates) Debugged, tested, and integrated various SCSI and Ethernet device drivers for Sunsoft’s multithreaded Solaris x86 (SunOS) Unix (SVR4), for PC 386, 486 and Pentium systems, with ISA, EISA, and PCI buses. Wrote a Solaris driver for the AMD PCscsi PCI/SCSI chips. Rewrote the Solaris 2.4 kernel module which provides PCI support so that it provides virtually all of the new Device Driver Interface (DDI) functions from Solaris 2.5. Wrote the documentation for this. Rewrote, debugged, and tested the device drivers for SPARC systems for Fast Ethernet (100baseT), Token Ring, and FDDI to use a generic STREAMS device driver module. SeeBeyond, Inc. (Now part of Sun Microsystems) Manager of Research and Development Core Products Group April 1994 - August 1994 (Contractor - Part time) Created and implemented Quality Assurance, directed cleanup of a very buggy and very late product version, calmed down customers, got the product shipped, created a bug-tracking system, organized existing development staff, hired a new GUI programmer. Implemented policies to prevent similar situations in the future. Developed the requirements, design, and schedule for the next two major releases of the company's flagship product. NASA Jet Propulsion Laboratory (JPL) Software Engineer / Programmer Deep Space Network November 1992 - December 1993 (Contractor, Midcom Inc.) Designed software for a system which performs complex analysis and calibration for NASA's Deep Space Network. Designed and built the GUI. System is a Sun/SPARC, with VME and HPIB (IEEE 488) buses. The software was ANSI C, X-Windows (X11R4), and Motif, under SunOS (UNIX). NASA/JPL has since applied for patents on the system, which has won a NASA new technology award. TEKELEC Programmer Network Analyzer Group August 1992 - November 1992 (Contractor) Programmed enhancements (C, C++, X-Windows/Motif, Interactive UNIX) to an existing FDDI and Ethernet network protocol analyzer. Ported the enhanced application to Token Ring (802.5). Integrated and configured a PC-based evaluation network, using Novell Netware 3.11 and Token Ring. Tested both new configurations. PacTel Cellular Senior Systems Analyst / Systems Programmer Mobile Communicatons Group April 1992 - August 1992 (Contractor) Specified, designed, and prototyped a Client-Sever system (using a custom-designed protocol) to link an existing customer tracking and billing system through a 56K DECNET link to a credit bureau on the east coast. The system integrated PacTel's VAX/VMS clusters with the credit bureau's ULTRIX (UNIX) machines. -- (MORE UPON REQUEST) -- v61.1 5/8/16