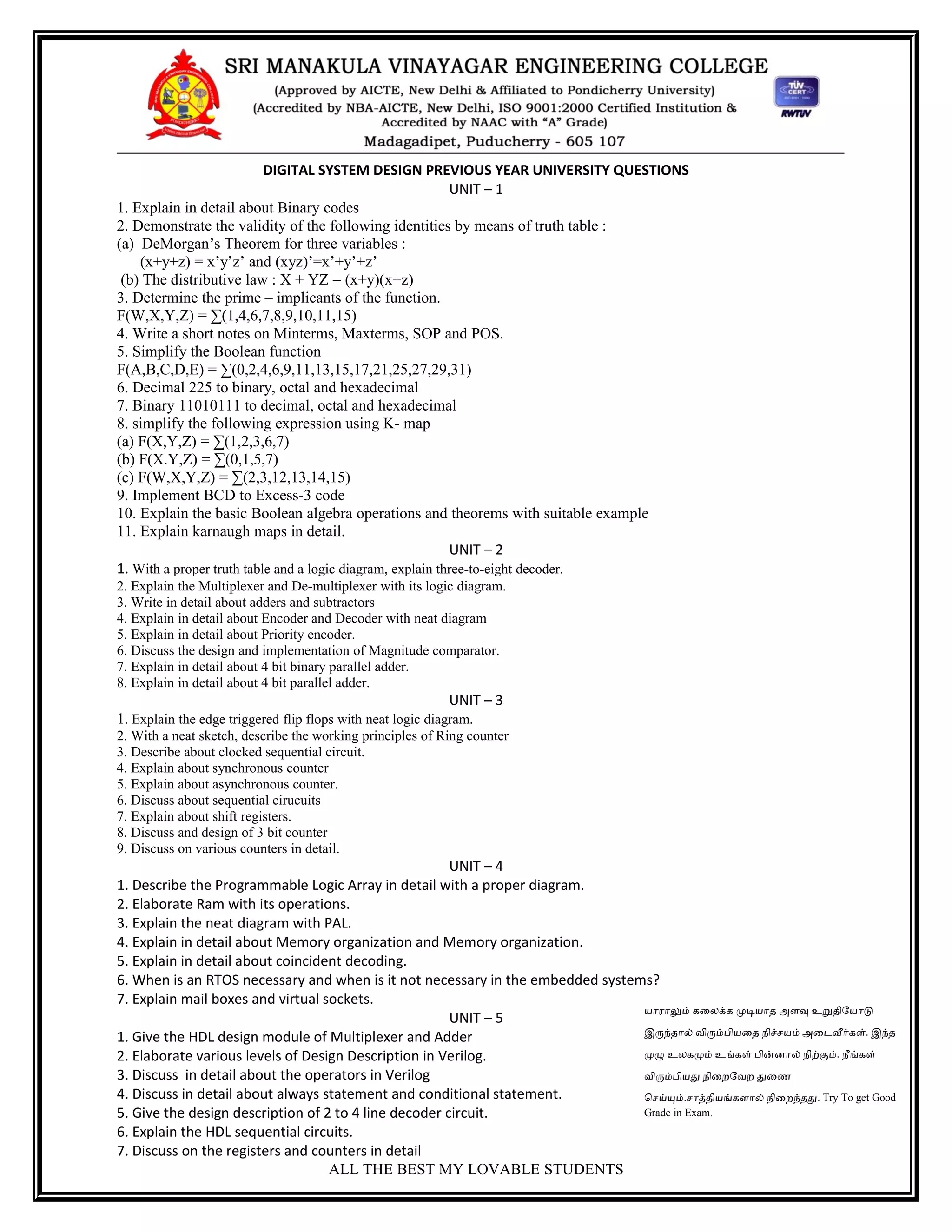

This document contains questions from previous year university examination papers on the topic of digital system design. It covers 5 units:

Unit 1 includes questions on binary codes, Boolean algebra identities, prime implicants, minterms, maxterms, SOP, POS, simplifying Boolean functions, and Karnaugh maps.

Unit 2 includes questions on decoders, multiplexers, adders, encoders, priority encoders, magnitude comparators, and parallel adders.

Unit 3 includes questions on edge triggered flip flops, ring counters, clocked sequential circuits, synchronous counters, asynchronous counters, and shift registers.

Unit 4 includes questions on programmable logic arrays, RAM, PAL, memory