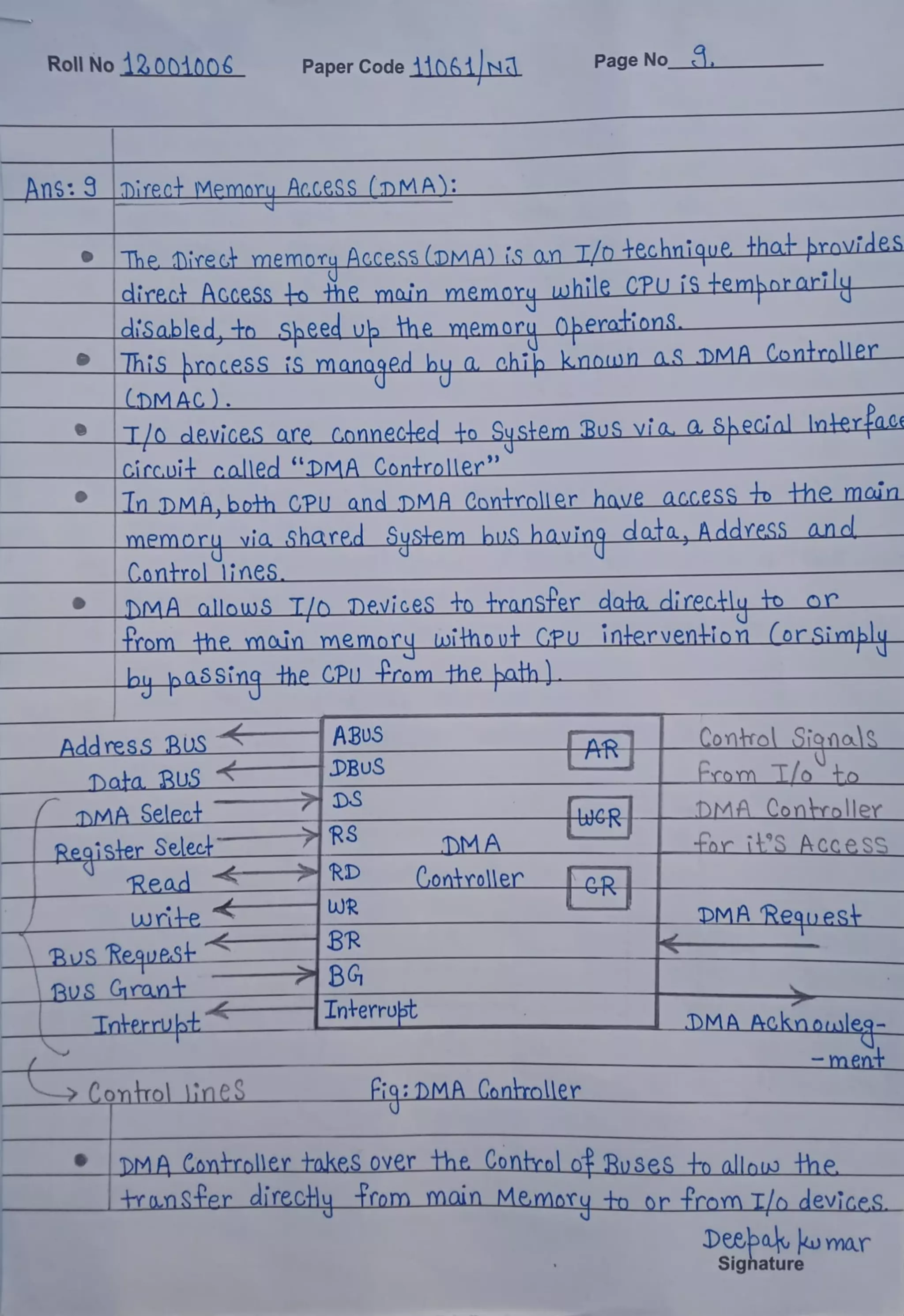

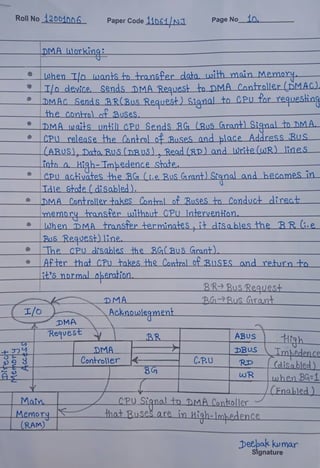

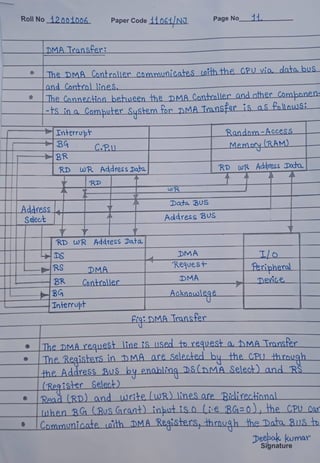

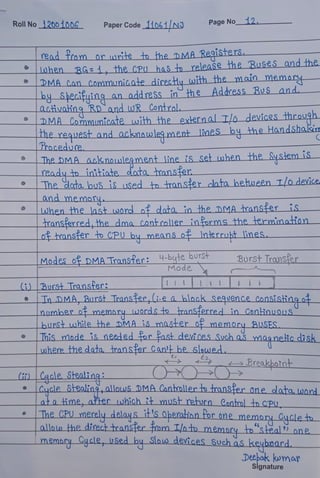

The document discusses Direct Memory Access (DMA) which allows input/output (I/O) devices to access main memory directly without intervention from the Central Processing Unit (CPU). It describes how the DMA controller takes control of the address bus, data bus, read and write lines to facilitate direct transfer between I/O devices and memory while the CPU is temporarily disabled. It also explains the different signals and lines used by the DMA controller to communicate with devices and memory as well as the two common modes of DMA transfer: burst and cycle stealing.