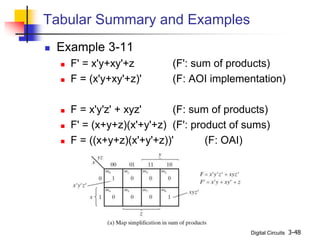

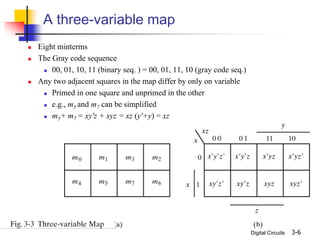

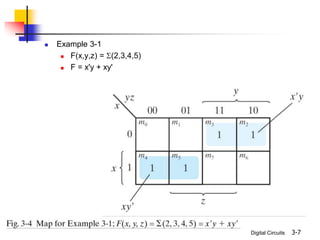

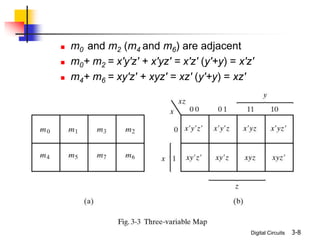

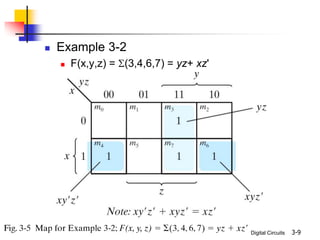

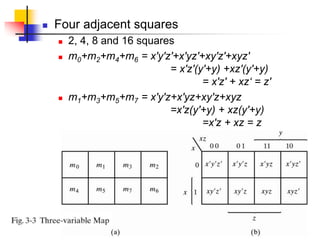

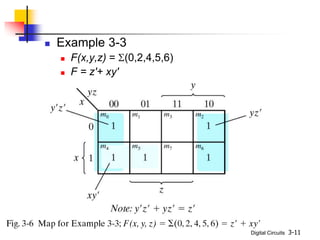

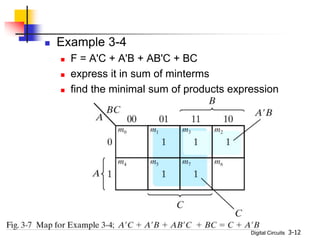

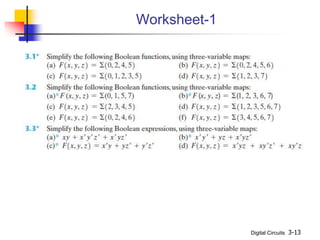

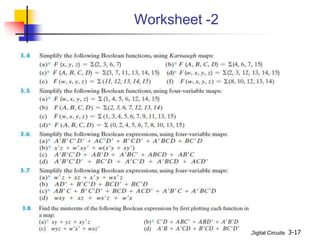

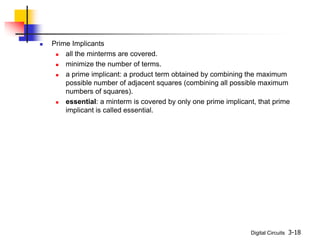

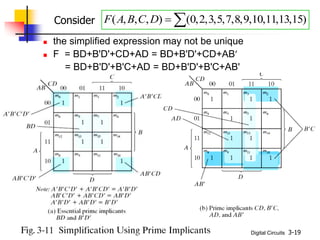

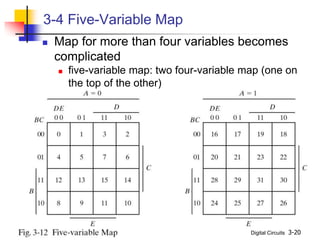

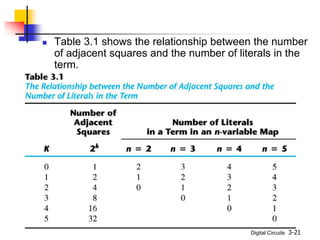

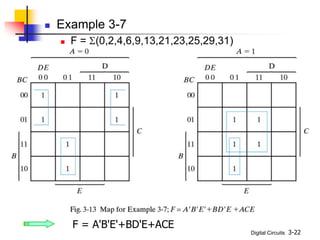

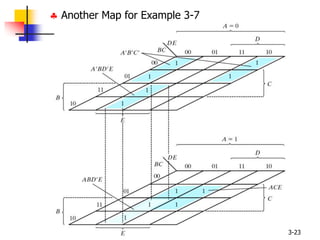

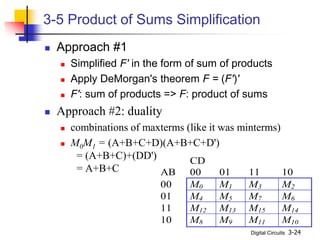

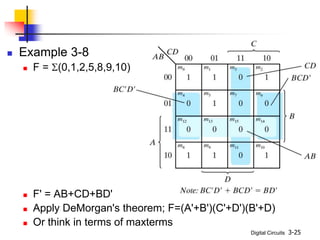

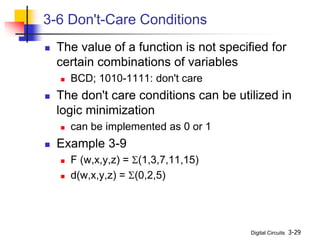

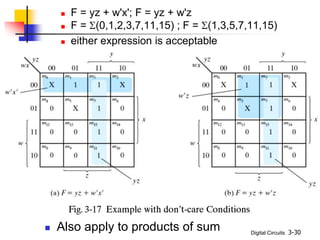

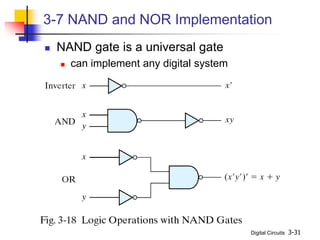

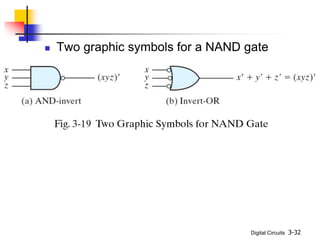

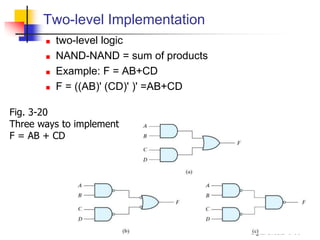

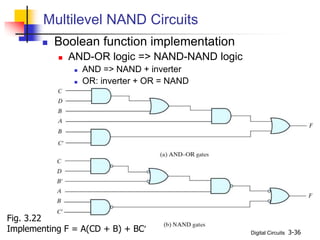

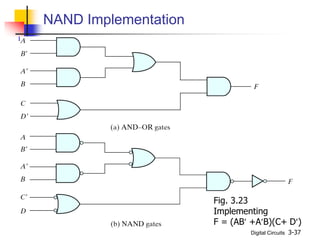

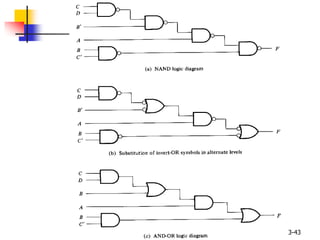

This document discusses gate-level minimization techniques. It introduces Karnaugh maps as a graphical method to minimize Boolean functions with up to 5 variables by grouping adjacent minterms. The document covers constructing K-maps, simplifying functions using grouping of minterms, and provides examples. It also discusses other minimization techniques like product-of-sums simplification using De Morgan's laws, incorporating don't care conditions, and implementing minimized functions using NAND, NOR, AND-OR-Invert and OR-AND-Invert gates.

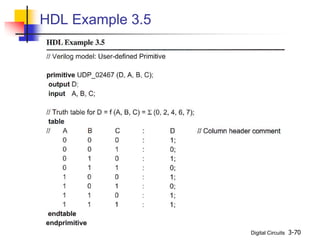

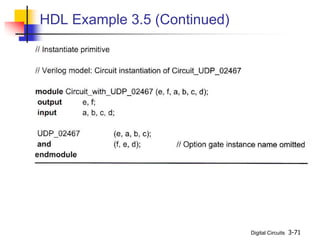

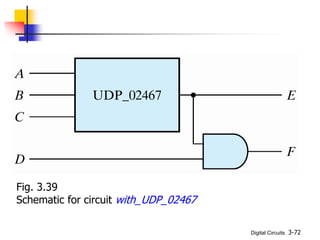

![Digital Circuits 3-44

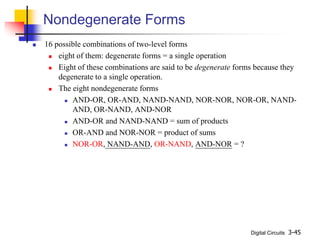

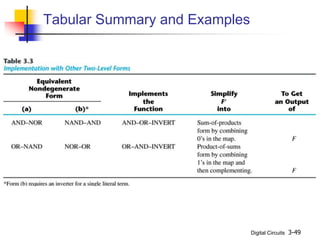

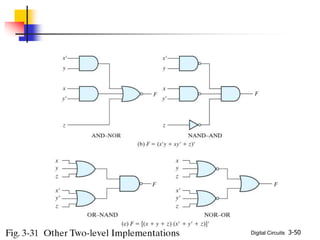

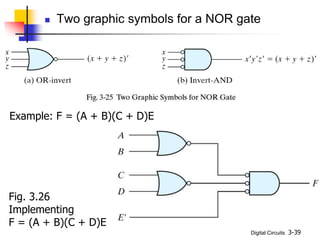

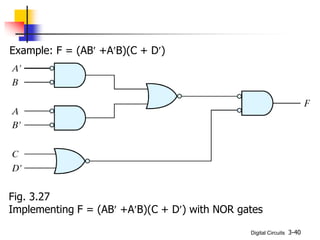

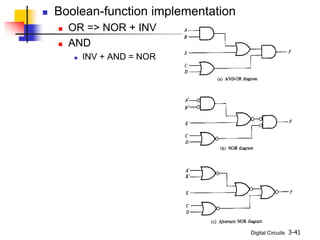

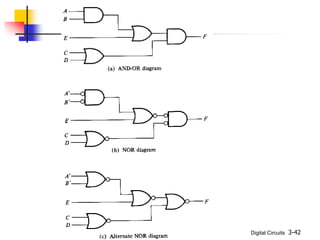

3-8 Other Two-level Implementations

Wired logic

NAND or NOR gates allow the possibility of aa wire connection between the outputs of two gates to provide a

specific logic function.

open-collector TTL NAND gates: wired-AND logic

The AND gate is drawn with the lines going through the centre of the gate to distinguish it from a conventional

gate.

A wired-logic gate does not produce a physical second-level gate, since it is just a wire connection.

The NOR output of ECL gates: wired-OR logic

Emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family.

( ) ( ) ( ) ( )( )

( ) ( ) [( )( )]

F AB CD AB CD A B C D

F A B C D A B C D

AND-OR-INVERT function

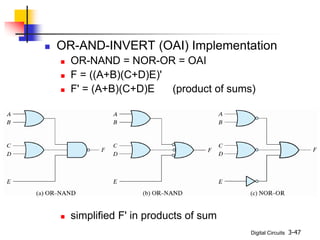

OR-AND-INVERT function](https://image.slidesharecdn.com/unit-1part-3-220804015635-71c828ff/85/DLD-BOOLEAN-EXPRESSIONS-44-320.jpg)