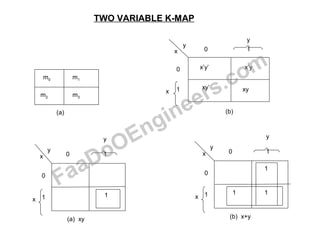

Two Variable K-Map and Prime Implicants

- 1. m0 m1 m3m2 (a) y x’y’ x’y xyxy’1 0 y x 0 1 x (b) (b) x+y 1 0 y x 0 1 x y (a) xy 1 0 y x 0 1 x y 1 1 11 TWO VARIABLE K-MAP FaaDoOEngineers.com

- 2. m0 m4 m1 m3 m2 m5 m6m7 y x x’y’z’ xy’z’ x’y’z x’yz x’yz’ xy’z xyz’xyz yz x 0 1 00 01 11 10 z THREE VARIABLE MAP y z yz 1 0 1 1 1 1 1 1 1 1 00 01 11 10 MAP FOR F=x’yz+x’yz’+xy’z’+xy’z F=x’y+xy’ FaaDoOEngineers.com

- 3. Reflected Code Binary Code Reflected Code 0000 0000 0001 0001 0010 0011 0011 0010 0100 0110 0101 0111 0110 0101 0111 0100 1000 1100 1001 1101 1010 1111 1011 1110 1100 1010 1101 1011 1110 1001 1111 1000 FaaDoOEngineers.com

- 4. MAP FO R : x’yz+xy’z’+xyz+xyz’=yz+xz’ yz x 00 01 11 10 0 1 1 1 1 1 z y A BC A 00 01 11 10 0 1 C BC B 1 1 1 11 1 MAP FOR : A’C+A’B+AB’C+BC=C+A’B yz x 00 01 11 10 0 1 y x F(x,y,z)=Σ(0,2,4,5,6)=z’+xy’ 1 1 1 1 1 FaaDoOEngineers.com

- 5. m0 m1 m3 m2 m6 m14 m10m11m9m8m8 m12 m13 m15 m7m5m4 (a) y z w 00 01 11 10 00 01 11 10wx yz x w’x’y’z’ w’xy’z’ wxy’z’ wx’y’z’ w’x’y’z w’x’yzw’x’yz w’x’yz’ w’xyz’ wxyz’ wx’yz’wx’yzwx’y’z wxy’z wxyz w’xyzw’xy’z FOUR VARIBALE MAP 1 square represents a term of 4 literals. 2 adjacent squares represent a term of 3 literals. 4 adjacent squares represent a term of 2 literals. 8 adjacent squares represent a term of 1 literal. 16 adjacent squares represent the function equal to 1 FaaDoOEngineers.com

- 6. MAP FOR : F(w,x,y,z)=Σ(0,1,2,4,5,6,8,9,12,13,14)=y’+w’z’+xz’ y yz z 00 01 11 10 10110100 wx x w 1 1 1 1 1 1 1 1 1 1 1 C CD D 00 01 11 10 10110100 AB B A 1 1 1 1 1 MAP FOR : A’B’C’+B’CD’+A’BCD’+AB’C’=B’D’+B’C’+A’CD’ 1 1 FaaDoOEngineers.com

- 7. A C AB 00 01 11 10 000 001 011 010 110 111 101 100 CDE B D E E FIVE -VARIABLE MAP 0 1 3 2 6 77 5 4 8 9 11 10 15 13 12 282931 == 30 14 26272524 16 17 19 18 22 23 21 20 FaaDoOEngineers.com

- 8. B ABC DEF 000 001 011 010 110 111 101 100 000 001 011 010 0 1 3 2 6 77 5 4 8 9 11 10 15 13 12 282930 31 26272524 16 17 19 18 22 23 21 20 110 111 111 101 100 C C D A E FF 48 56 49 51 50 54 55 53 52 57 59 58 62 63 61 60 40 41 43 42 46 47 45 44 32 33 35 34 38 39 37 36 SIX VARIABLE MAP 14 FaaDoOEngineers.com

- 9. No of adjacent squares & literals in a term 2k adjacent squares=n-k literals n-variable map k 2k n=2 n=3 n=4 n=5 n=6 n=7 0 1 2 3 4 5 6 7 1 2 1 2 3 4 5 6 0 4 0 1 2 3 4 5 3 8 0 1 2 3 4 4 16 0 1 2 3 5 32 0 1 2 6 64 0 1 7 128 0FaaDoOEngineers.com

- 10. 11 1111 1111 11 1 1 CDE 000 001 011 010 110 111 101 100 C B AB 00 01 11 10 E D E A F=BE+AD’E+A’B’E’ F(A,B,C,D,E)=Σ (0,2,4,6,9,11,13,15,17,21,25,27,29,31) FaaDoOEngineers.com

- 11. Example F(A , B, C, D) =∑(0,1,2,5,8,9,10) (ii) Simplify it in: (iii) Sum of products (iv) Product of sums AB (i) Sum of products F=B’D’+B’C’+A’C’D F’ =AB+CD+BD’ (ii) F=(A’+B’)(C’+D’)(B’+D) 00 01 11 10 A 11 CD 00 01 10 1011 0000 0010 1011 C D B FaaDoOEngineers.com

- 13. GATE IMPLEMENTATION X Y Z F 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 1 7 0 1 0 1 1 0 1 1 1 1 0 TRUTH TABLE OF FUNCTION F F(x,y,z)= Σ(1,3,4,6) F(x,y,z)= Σ(1,3,4,6) F(x,y,z) = ∏ (0,2,5,7) FaaDoOEngineers.com

- 14. 1001 0110 0 1 00 01 11 10 z yzx x y Sum of products F=x’z+xz’) Product of sums F’=xz+x’z’ F=(x’+z’)(x+z) FaaDoOEngineers.com

- 15. NAND and NOR implementation x y z F=(xyz)’ AND invert x y z F=(x’+y’+z’)=(xyz)’ Invert-OR F=(x+y+z)’ OR-invert (a) TWO GRAPHIC SYMBOLS FOR NAND GATE x y z F=x’y’z’=(x+y+z)’ Invert-AND (b) TWO GRAPHIC SYMBOLS FOR NOR GATE FaaDoOEngineers.com

- 16. x’x x x’ Buffer-invert AND-invert x x’ OR-invert THREE GRAPHIC SYMBOLS FOR INVERTORFaaDoOEngineers.com

- 17. A B C D E A B C D E’ F F (a) (b) NAND Implementation Simplified Boolean function F=AB+CD+E Convert AND gates with at least two literals to NAND gates at first level. THREE WAYS TO IMPLEMENT F=AB+CD+E FaaDoOEngineers.com

- 18. Draw a single NAND gate at level-2 & NAND gate for a term with single literal (c) A B C D E F F={(AB)’.(CD)’.E’} F=AB+CD+D FaaDoOEngineers.com

- 19. x’ y’ z’ x F Two-level implementation 1000 0001 z 00 01 11 10 yyz 0 1 x F(x,y,z)= Σ(0,6) F=x’y’z’+xyz’ F’=x’y+xy’+z (a) MAP SIMPLIFICATION IN SUM OF PRODUCTS y z’ (b) F=x’y’z’+xyz’ FaaDoOEngineers.com

- 20. X’ y x Y’ z F’ Three level implementation F (c) F’=x’y+xy’+z IMPLEMENTATION OF THE FUNCTION WITH NAND GATES F(x,y,z) = Σ(0,6) FaaDoOEngineers.com

- 21. NOR Implementation F (C+D) A B C D E (A+B) Simplified Boolean function F=(A+B)(C+D)E F A B C D E’ Convert OR gates with at least two inputs to NOR gates at first level (a) (b) THREE WAYS TO IMPLEMENT F=(A+B)(C+D)E FaaDoOEngineers.com

- 22. A B C D E (C) Draw a single NOR gate at level 2 & a NOR gate for a term with single literal. FaaDoOEngineers.com

- 23. Example F(n, y, z) = {(0, 6) F = x’y’z’ + xyz’ F’ = x’y + xy’ + z x y’ x’ y z’ F (a) F = (x + y’) (x’ + y)z’ x y z x’ y’ z F F’ (b) F’ = (x + y + z) (x’ + y’ + z) IMPLEMENTATION WITH NOR GATES FaaDoOEngineers.com

- 24. y 0100 0100 01X0 X11X 01 11 10 YZ 00 01 11 10 w x z wx 00 F(w,x,y,z)= Σ(1,3,7,11,15) D(w,n,y,z)=Σ(0,2,5) Combing 1’s and X’s F=w’z+yz or F=w’x’+yz FaaDoOEngineers.com

- 25. YZ y 0100 0100 01X0 X11X 01 11 10 00 01 11 10 w x z wx 00 Combing 0’s and X’s F’=z’+wy’ F=z(w’+y) EXAMPLES WITH DON’T CARE CONDITION FaaDoOEngineers.com

- 26. DETERMINE THE PRIME-IMPLICANTS OF THE FUNCTION F(w,x,y,z)=∑(1,4,6,7,8,9,10,11,15) (a) (b) (c) 0001 1 0100 4 1000 8 0110 6 2 1 9 1010 10 0111 7 2 11 11 1111 15 1, 9 (8)* 4, 6 (2)* 8, 9 (1) 8, 10 (2) 6, 7 (1)* 9, 11 (2) 10,11 (1) 7, 15 (8)* 11,15 (4)* 8, 9, 10, 11, (1,2)* 8, 9, 10, 11, (1,2)* FaaDoOEngineers.com

- 27. PRIME-IMPLICANTS Decimal Binary w x y z Term 1,9 (8) 4,6 (2) 6,7 (1) 7,15 (8) 11,15 (4) 8,9,10,11 (1,2) - 0 0 1 0 1 - 0 0 1 1 - - 1 1 1 1 - 1 1 1 0 - - X’ y’ z W’ x z’ w’ x y X y z w y z W x’ F=x’y’z+w’xz’+w’xy+xyz+wyz+wx’ FaaDoOEngineers.com

- 28. (i) Selection of PRIME-IMPLICANTS 1 4 6 7 8 9 10 11 15 x’y’z 1,9 X X w’xz’ 4,6 X X w’xy 6,7 X X xyz 7,15 X X wyz 11,15 X X wx’ 8,9,10,11 X X X X F=x’y’z+w’xz’+wx’+xyz Essential Prime-implicants FaaDoOEngineers.com

- 29. 1111 1 111 1 01 11 10 YZ 00 01 11 10 w x z wx 00 F(w,x,y,z)=∑(1,4,6,7,8,9,10,11,15) y MAP FOR THE FUNCTION OF F = x’y’z+w’xz’+xyz+wx’ FaaDoOEngineers.com

- 30. THE TABULATION METHOD (Q-M Mehthod) Example: F(w,x,y,z) = ∑(0,1,2,8,10, 11,14,15) (i) DETERMINATION OF PRIME-IMPLICANTS (a) (b) (c) wxyz wxyz wxyz 0 0000√ 0,1 000-* 0,2 00-0√ 0,2,8,10 -0-0* 0,8,2,10 -0-0* 1 0001√ 0,8 -000√ 2 0010√ 10,11,14,15 1-1-* 10,11,14,15 1-1-* 8 1000 √ 2,10 -010√ 8,10 10-0√ 10 1010√ 10,11 101-√ 11 1011√ 10,14 1-10√ 14 1110√ 11,15 1-11√ 15 11111√ 14,15 111-√ Prime-implicants F=w’x’y’+x’z’+wy FaaDoOEngineers.com

- 31. (i) Selection of PRIME-IMPLICANTS 0 1 2 8 10 11 14 15 w’x’y’ 0,1 X X x;z’ 0,2,8,10 X X X X wy 10,11,14,15 X X X X Essential Prime-implicants : F=w’x’y’+x’z’+wy FaaDoOEngineers.com

- 32. 111 11 11 1 00 01 11 10 Y 10 11 01 00 wx yz W X F= w’x’y’ + x’z’+wy MAP FOR THE FUNCTION FaaDoOEngineers.com

- 33. RULES FOR NAND and NOR IMPLEMENTATION Case Function to Simplify Standrad From to Use How to drive Implement with Number of Levels to F (a) (b) (c) (d) F F F F Sum of Products Sum of Products Product of Sums Product of Sums Combine 1,s in map Combine 0, s In map Complement F in (b) Complement F in (a) NAND NAND NOR NOR 2 3 2 3 FaaDoOEngineers.com

- 34. A B C D F F = (AB + CD)’ F = (A B)’ . (C D)’ (a) Wired – AND in open Collector TTL NAND gates C A B D F F = [(A + B ) ( C + D)]’ F = (A + B)’ + (C + D)’ (b) Wired – OR in ECL gates FaaDoOEngineers.com

- 35. A B C D E A B C D E F F (AND – OR - INVERT) OR – AND - INVERT WIRED LOGIC A B C D E F (a) AND - NOR (b) AND - NOR (c) NAND - AND AND – OR – INVERT CIRCUITS F = (AB + CD + E)’ (Non degenerate form) AND - - NOR & NAND – AND are equivalent forms FaaDoOEngineers.com

- 36. NONDEGENERATE FORMS COMMON GATE : AND, OR, NAND, NOR IF AT LEVEL 1 : ONE TYPE OF GATE AT LEVEL 2 : ONE TYPE OF GATE * POSSIBLE COMBINATIONS = 16 8 OF THESE COMBINATIONS ARE SAID TO BE DEGENERATE FORMS BECAUSE THEY DEGENERATE TO A SINGLE OPERATION. FOR EXAMPLE : NAND – OR AND – AND OPERATION NAND – NOR OR – OR OPERATION NOR – AND AND – NAND OPERATION NOR – NAND OR – NOR OPERATION 8 OF THESE COMBINATION S ARE SAID TO BE NON – DEGENERATE FORMS BECAUSE THEY PRODUCE AN IMPLEMENTATION IN SUM OF PRODUCTS OR PRODUCT OF SUMS. FOR EXAMPLE : AND – OR OR – AND NAND – NAND NOR – NOR NOR – OR NAND – AND OR – NAND AND - NOR FaaDoOEngineers.com

- 37. A B C D E F (a) OR - NAND A B C D E F (b) OR - NAND CONTED FaaDoOEngineers.com

- 38. A B C D E F (C) NOR - OR OR – AND – INVERT F = [(A + B ) (C + D ) E]’ (Non – degenerate form) OR – NAND & NOR – OR ARE EQUIVALENT FORMSFaaDoOEngineers.com

- 39. X’ y X y’ z F X’ y X y’ z F Example AND - NOR NAND - AND F = x’ y + x y’ + z (a) F = (x’ y + x y’ + z)’ 1 0 0 0 0 0 0 1 0 1 00 01 11 10 F’ = x’ y + x y’ + z F = x’ y z’ + x y z’ FaaDoOEngineers.com

- 40. x y z z x’ y’ F x y z z x’ y’ F OR - NAND NAND - OR F = x’ y’ z’ + x y z’ F = (x + y + z) (x’ + y’ +z) (b) F = [(x + y + z) (x’ + y’ + z)]’ TWO – LEVEL IMPLEMENTATION FaaDoOEngineers.com