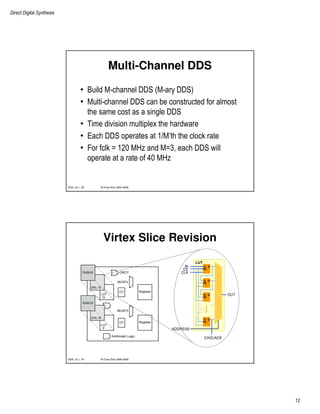

This document discusses direct digital synthesis (DDS) techniques. DDS allows digitally generating waveforms by mapping a phase increment to sinusoidal outputs. Key aspects covered include: phase truncation DDS using lookup tables, dithered DDS to reduce spurs, and Taylor series expansion DDS for higher precision. Applications include digital up/down converters. Multi-channel DDS can efficiently generate multiple signals using time division multiplexing of hardware.

![Direct Digital Synthesis

4

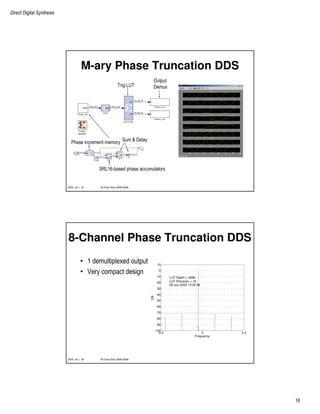

© Chris Dick 2004-2009DDS v2.1 7

Phase Truncation DDS

0 0.1 0.2 0.3 0.4 0.5

-100

-80

-60

-40

-20

0

NORMALIZED FREQUENCY

DB

PHASE

INCREMENT

∆φ M

clk

PHASE

ACCUMULATOR

(e.g. 28-32 bits)

fout = ∆φ fclk/2N

SINE/COSINE

LOOKUP

TABLE

e.g. N = 8-16

θ(n)^

θ(n)

Q( )

N sin(θ(n))

^

cos(θ(n))^

B

B

0 20 40 60 80 100

0

0.5

1

TIME

ERROR

20 40 60 80 100

-1

0

1

TIME

AMPLITUDE

© Chris Dick 2004-2009DDS v2.1 8

DDS Noise

• The term contributing to the DDS noise

component can be calculated by examining the

effect of the phase accumulator quantizer

ˆ( ) [ ( ) ( )] ( ) ( )

ˆ( ) ( )

( ) ( )

ˆ( ) ( ) ( )

[1 ( )]

( )

DESIRED COMPONENT

UNDESIRED COMPONENT

j n j n n j n j n

j n j n

j n j n

n n n

e e e e

e e j n

e j n e

θ θ δθ θ δθ

θ θ

θ θ

θ θ δθ

δθ

δθ

+

= +

= =

≈ +

= +](https://image.slidesharecdn.com/dds2-171227113639/85/Dds-2-4-320.jpg)

![Direct Digital Synthesis

15

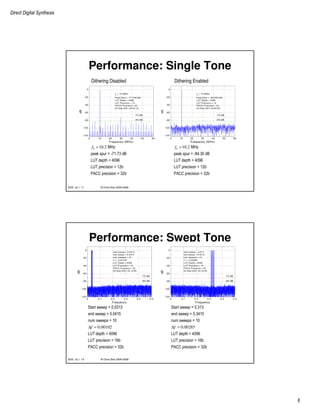

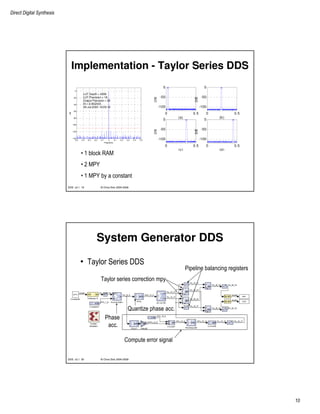

© Chris Dick 2004-2009DDS v2.1 29

M-ary Taylor Series DDS

Channel demultiplexing

M-ary phase accumulator

DDS

© Chris Dick 2004-2009DDS v2.1 30

3-Channel Taylor Series DDS

-0.5 0 0.5

-140

-120

-100

-80

-60

-40

-20

0

Frequency

DB

LUT Depth = 4096

LUT Precision = 18

Output Precision = 20

f = [0.1, 0.2, 0.3]

09-Jun-2002 11:37:14

• 3 tones efficiently generated

by time sharing the hardware

• Sample-rate versus area

tradeoff](https://image.slidesharecdn.com/dds2-171227113639/85/Dds-2-15-320.jpg)