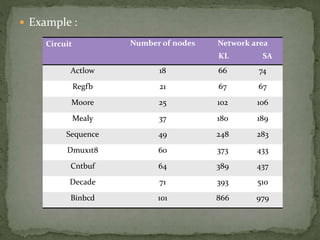

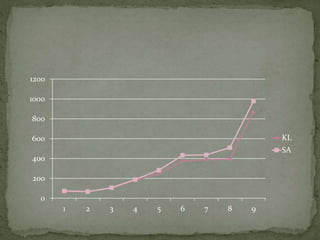

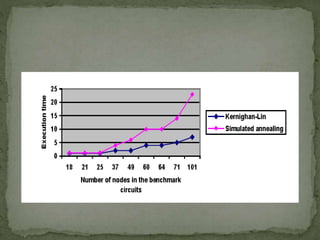

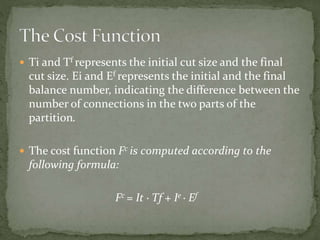

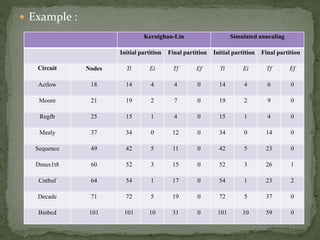

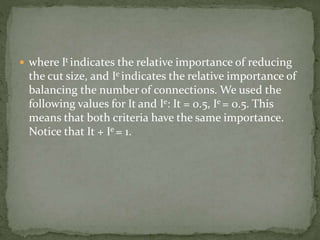

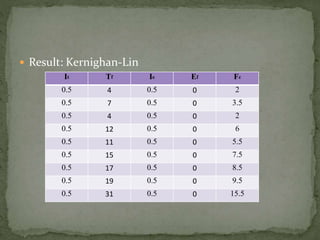

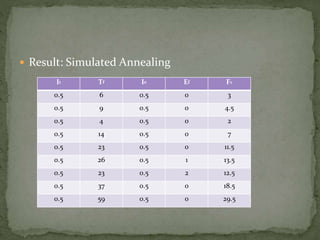

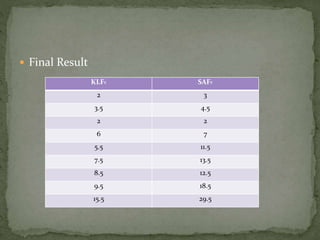

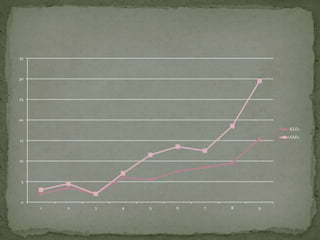

The document summarizes a study comparing the Kernighan-Lin (KL) and Simulated Annealing (SA) graph partitioning algorithms. The study evaluated the algorithms based on estimated network area, execution time, and cost function on various benchmark circuits. For smaller circuits, there was little difference between the algorithms. However, for larger circuits with more nodes, KL produced better results with lower execution times and cost function values compared to SA. The KL algorithm was found to produce the best overall results.