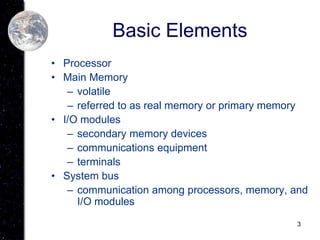

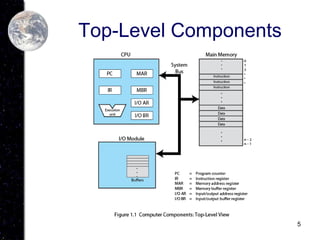

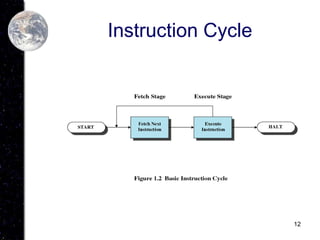

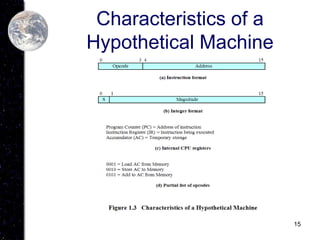

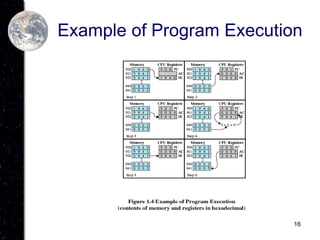

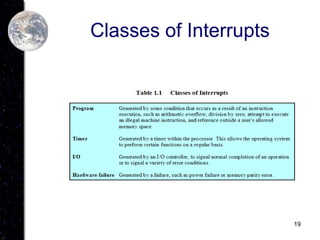

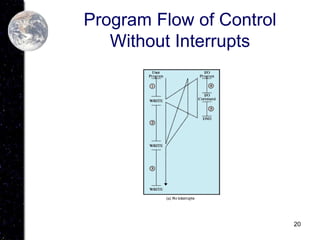

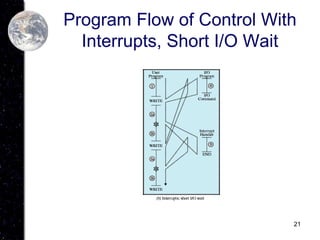

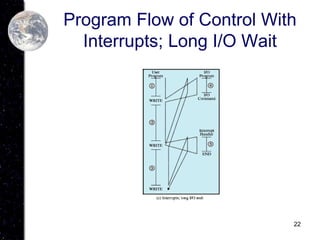

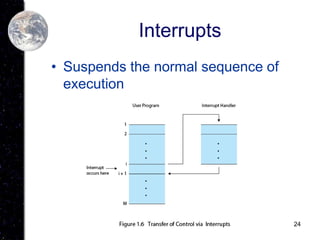

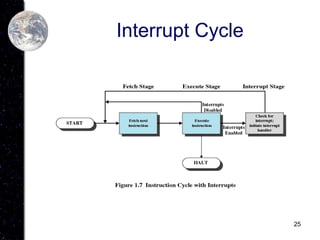

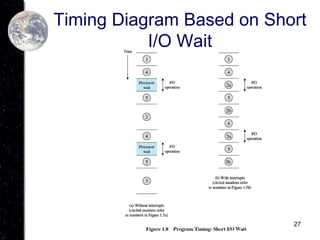

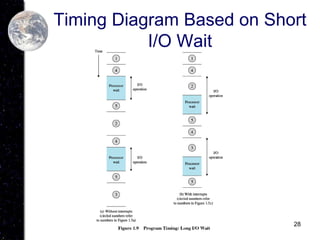

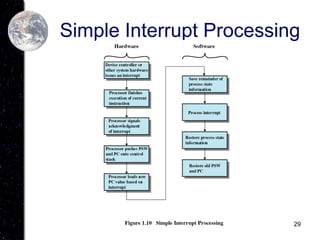

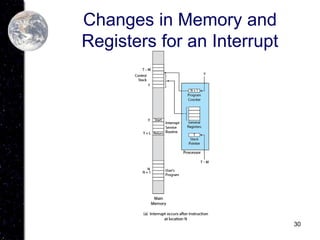

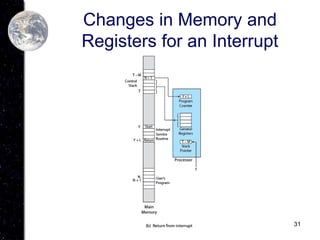

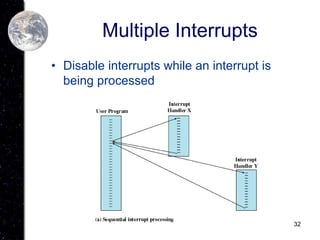

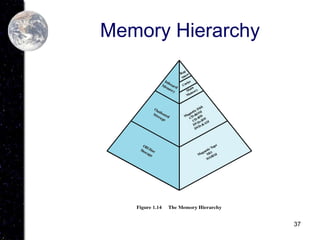

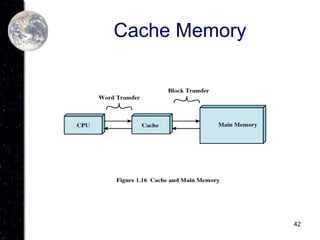

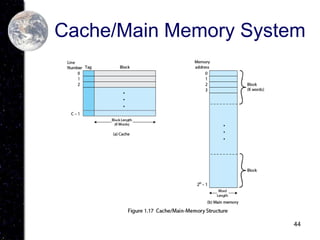

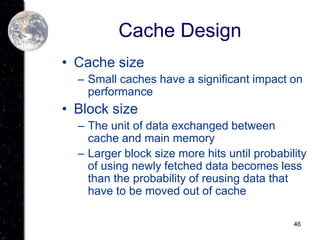

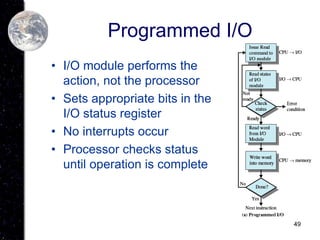

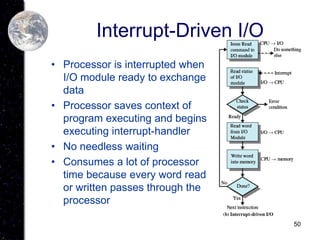

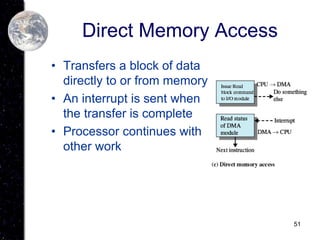

This document provides an overview of basic computer system components and their functions. It discusses the operating system, main hardware components like the processor and memory, and how they interact. It also covers concepts like interrupts, memory hierarchy, caches, and different I/O techniques like programmed I/O, interrupt-driven I/O, and direct memory access. The document is intended as an introductory overview of computer systems.