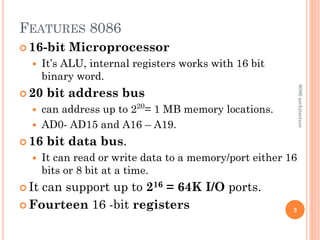

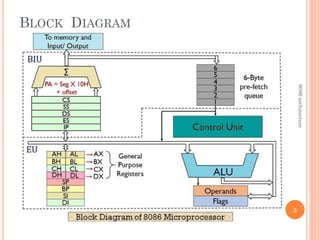

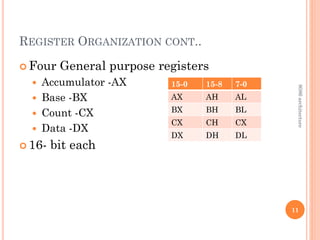

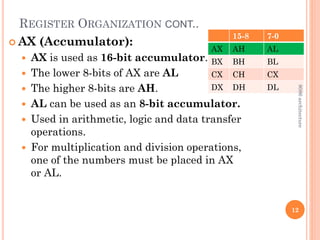

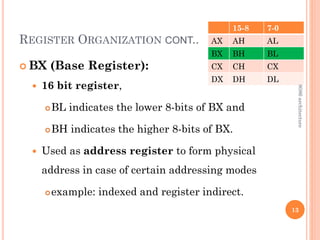

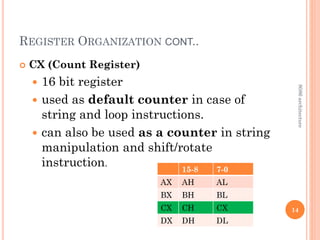

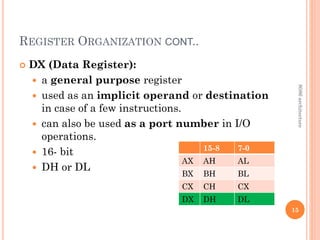

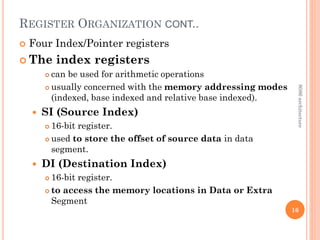

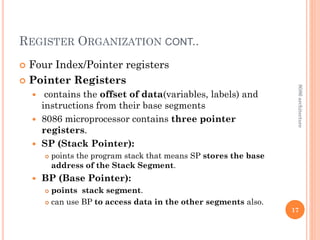

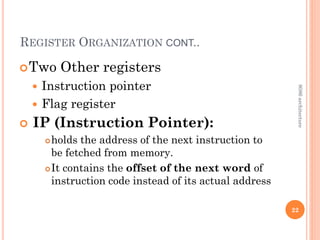

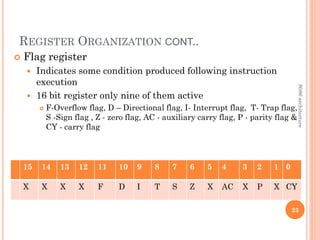

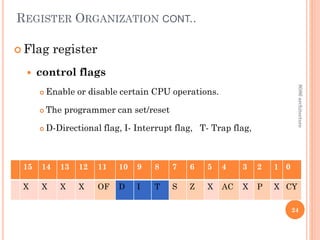

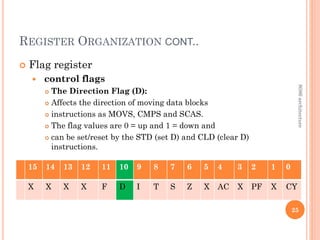

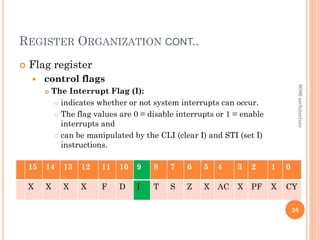

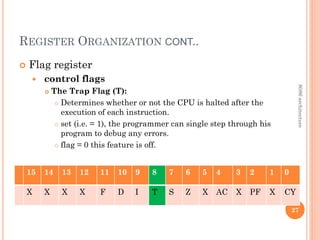

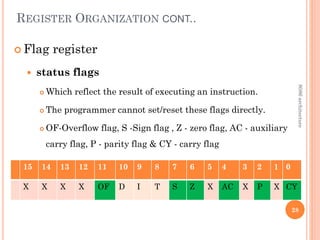

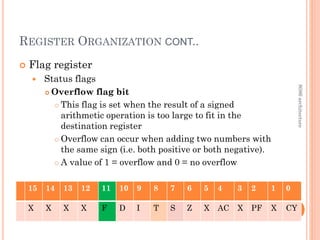

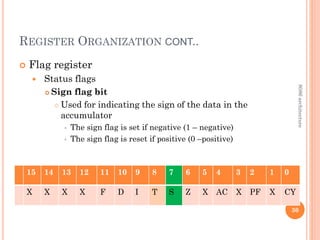

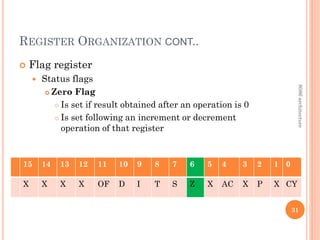

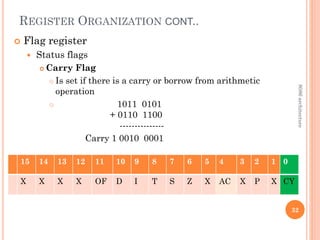

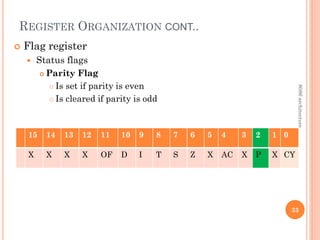

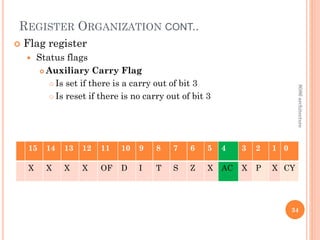

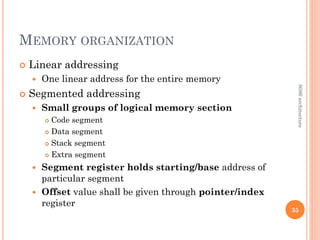

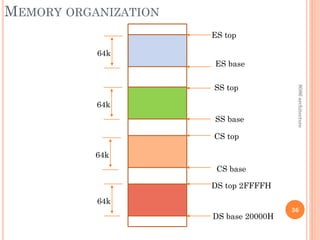

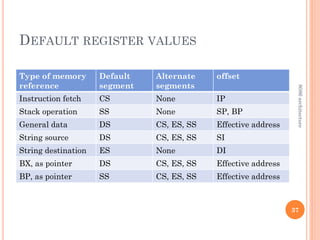

Chapter 2 of the document covers the 8086 microprocessor architecture, detailing its key features including a 16-bit microprocessor, a 20-bit address bus capable of addressing 1 MB of memory, and fourteen 16-bit registers. It describes the structure of the bus interface unit and execution unit, along with various types of registers used for data storage and processing. The document also discusses memory organization, segmentation, and the role of flags in execution control.