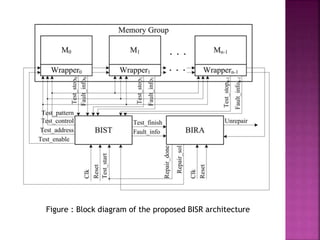

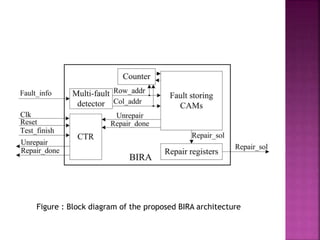

The document presents a proposed built-in self-repair (BISR) scheme for multiple embedded memories. It discusses testing embedded memories using built-in self-test (BIST) and repairing faults using built-in redundancy analysis (BIRA). The proposed approach uses parallel BIST to test memories concurrently and then serial BIRA to repair faulty memories one by one, prioritizing larger memories. This trades off test time and repair time against optimal repair rate and reduced area overhead.